Fターム[4M104AA06]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | II−VI族 (146)

Fターム[4M104AA06]に分類される特許

81 - 100 / 146

薄膜トランジスタアレイおよびその製造方法

【課題】 本発明は、クシ型電極を用いた薄膜トランジスタのフィードスルーを低減しつつ、電極の電気抵抗の増大や作製の難しさを改善した薄膜トランジスタアレイを提供することを課題とする。

【解決手段】 ソース・ドレイン電極をクシ型とし、ドレイン電極の幅をソース電極の幅より細くし、ドレイン電極あるいはソース・ドレイン電極の根元をテーパー状にすることにより、電気抵抗の増大を抑制し、かつ歩留まりを向上した薄膜トランジスタアレイ。

(もっと読む)

半導体装置及びその製造方法

【課題】垂直トランジスタを用いたCMOSインバータ回路の形成面積を小さくする。

【解決手段】半導体基板1上に絶縁分離帯2により画定された素子形成領域5にp型及びn型不純物領域1p、1nを形成し、それらをドレイン領域としその上に立設されたナノワイヤ3をチャネルとするpMOS及びnMOSトランジスタTr1、Tr2が設けられる。素子形成領域5の表面には不純物領域1p、1nとオーミック接合する接続領域4が形成され、トランジスタTr1、Tr2の外側で出力信号用ビア16と接続する。また、トランジスタTr1、Tr2のゲート電極13を接続するゲート電極配線15には、入力信号用のビア17が接続する。このCMOS回路は、2つのトランジスタと2個のビアの形成領域があれば形成できる。

(もっと読む)

光制御装置および画像表示装置

【課題】材料費、工程数を低減しその結果歩留まりを向上させ、コストを低減する。

【解決手段】薄膜トランジスタと、薄膜トランジスタと電気的に接続される電極104を有する光制御素子と、を備えた光制御装置であって、薄膜トランジスタの半導体領域102と画素電極104とが同一の半導体層からなり、同一の半導体層はIn,Ga,Znから選択される元素の少なくとも一つを含む酸化物からなる非晶質層である。半導体層の画素電極となる部分は、半導体領域よりも抵抗率が低い。また、保持電荷蓄積容量部にも抵抗率の低い領域を用いることができる。加えて、電極を延設し配線として用いることもできる。光制御素子はエレクトロルミネッセンス素子、液晶セル、電気泳動型粒子セル等を用いることができる。

(もっと読む)

半導体ナノ構造体、半導体デバイス及びそれらを形成する方法

【課題】 ナノ構造体の長手方向軸に沿った均一なドーパント濃度、及びナノ構造体の半径方向における示差的なドーパント濃度によって特徴付けられるドーピング・プロファイルを有する三次元のナノ構造体を提供すること。

【解決手段】 長手方向軸に沿って配列される複数の部分を含む半導体構造体が提供される。好ましくは、半導体構造体は、中間区域と、中間区域の対向する端部に配置された2つの末端区域とを含む。第1のドーパント濃度を有する半導体コアは、好ましくは、中間区域及び2つの末端区域を貫通して長手方向軸に沿って延びる。第2の、より高いドーパント濃度を有する半導体シェルは、好ましくは、半導体構造体の2つの末端区域で半導体コアの一部を取り囲むが、中間区域では取り囲まない。半導体構造体が100nmを超えない断面寸法を有するナノ構造体であることが、特に好ましい。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】電極と活性層が接する状態における一方のエッチングによるパターニングにおいて、活性層を削るなどのオーバーエッチ等によるダメージを活性層に生ずること無くソース/ドレイン電極層のエッチングを行うこと。

【解決手段】活性層にアルカリ耐性を有する材料を採用し、ソース/ドレイン電極にアルカリに溶解する性質を有する材料を採用し、ソース/ドレイン電極のパターニングの際に、アルカリ性のエッチャントを用いてエッチングをすることで、下層の活性層にダメージを与えること無く上層のソース/ドレイン電極をエッチングによりパターニングすることが可能になる。

(もっと読む)

FINFETデバイスのフィンの上に完全にシリサイド化されたデュアル・ゲートを形成する方法

【課題】 FinFetデバイスのフィンの上に完全にシリサイド化されたデュアル・ゲートを形成する方法を提供すること。

【解決手段】 FinFetデバイスのフィンの上に完全にシリサイド化されたゲートを形成する方法が開示される。本開示は、ポリシリコン層及びポリシリコン・ゲルマニウム層から各々のフィンの上のゲート・スタックをパターン形成し、次に、フィンの一方の上のポリシリコン・ゲルマニウム層を除去する方法を提供する。本開示は、さらに、両方のフィンの上に金属層を形成することと、FinFetデバイスをアニールして、FinFetデバイスの各々のフィンの上に完全にシリサイド化されたゲートを形成することとを含む。

(もっと読む)

ZnO系ダイオード

【課題】熱にも可視光にも強いZnO系ダイオードを提供する。

【解決手段】本発明によるZnO系ダイオードでは活性層が第1電極と第2電極との間に挟まれている。第1電極と第2電極とが活性層の上に設置されていても良い。活性層はMxIn1-xZnOを含む。ここで、Mは3族元素を表し、xはその成分比を表す。第1電極は活性層より仕事関数が小さく、第2電極は活性層より仕事関数が大きい。活性層に含まれる3族元素Mは好ましくは、Ga、Al、Tiのいずれかである。活性層に含まれる3族元素Mの成分比xは好ましくは0.2〜0.8である。第1電極は好ましくは、Ti、Al、Ca、Liの少なくともいずれかを含む。第2電極は好ましくは、Pt、Mo、W、Irの少なくともいずれかを含む。

(もっと読む)

電極構造

【課題】イオン化エネルギーが十分に小さな不純物(アクセプターもしくはドナー)が存在せず、p型もしくはn型半導体を作ることが出来ないワイドギャップ半導体に対して、正孔または電子を注入することが可能な電極構造を提供する。

【解決手段】イオン化エネルギーが0.2〜1eVの不純物がドープされたワイドギャップ半導体と、不純物イオンの結合エネルギーよりも小さな仕事関数を有し、かつ、ワイドギャップ半導体と接合される金属層と、を備え、外部電場を印加されることにより金属層からワイドギャップ半導体へ正孔が注入される電極構造。

(もっと読む)

薄膜半導体装置及びその製造方法

【課題】良好な電気的特性を備える薄膜半導体装置及びその製造方法を提供する。

【解決手段】薄膜半導体装置10は、基板11と、第1絶縁層(アンダーコート層)12と、第1導電層13と、第2絶縁層14と、半導体層15と、チャネル領域16と、ソース領域17と、ドレイン領域18と、ゲート絶縁膜19と、層間絶縁膜20と、ゲート電極21と、ソース電極22と、ドレイン電極23と、バイアス電極24と、を備える。バイアス電極24と第1導電層13によって半導体層15の基板側の界面にバイアス電圧を印加することによりオフ電流の低減や閾値電圧などの不安定性を抑止することができ、薄膜半導体装置10は良好な電気的特性を備える。

(もっと読む)

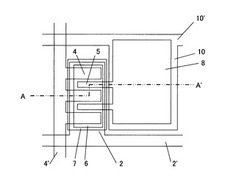

電子素子

【課題】製造コストが低く高速応答性の良好な電子素子を提供することを課題とする。

【解決手段】基板1の上にライン状の第1電極の上面2aに絶縁層3を形成する。この絶縁層3は、電極層2を形成するためのエッチング処理で用いるレジストを除去せずに残したものである。電極層2の側面2bから、絶縁層3の上面を経て、電極層2の側面2cにわたって、絶縁層4を形成する。絶縁層4の上には導電層5を形成する。電極層2の側面2bの側の絶縁部Bに平面視隣接して電極層6を形成し、同様に側面2cの側に電極層7を形成する。絶縁部Bを覆う領域に半導体層8を形成する。絶縁部Aの比誘電率及び膜厚は、この絶縁部Aを絶縁部Bと同一の膜厚及び同一の比誘電率を有する絶縁層で構成した場合よりも静電容量が小さくなるように設定する。

(もっと読む)

半導体デバイス層からの不純物の除去

本発明は、半導体デバイス(1)の製造中に、少なくとも一つの半導体デバイス層(4)から該半導体デバイス層(4)を用いて不純物を除去する方法を提供し、上記少なくとも一つの半導体デバイス層(4)は、化合物半導体材料及び/又はゲルマニウムを備え、少なくとも一つの半導体デバイス層(4)を準備した後、半導体デバイス(1)の製造中に実行される各加熱工程は、900℃以下の温度で、5分以下の時間により決定される低サーマルバジェットを有する。上記方法は、半導体デバイス層(4)よりも不純物に関して高い溶解度を有するゲルマニウム・ゲッタリング層(3)を設けることを備え、ゲルマニウム・ゲッタリング層(3)は、少なくとも一つの半導体デバイス層(4)に直接又は間接に接触して少なくとも部分的に設けられ、これにより、不純物は、少なくとも一つの半導体デバイス層(4)からゲルマニウム・ゲッタリング層(3)へ拡散することができる。本発明は、また、発明の実施態様による不純物の除去方法を用いて半導体デバイスを形成する方法を提供し、及びそれにて得られる半導体デバイスを提供する。  (もっと読む)

(もっと読む)

シリコンナノワイヤに基づくトンネル効果トランジスタ

【課題】トンネル電界効果トランジスタ(TFET)は、金属酸化物半導体電界効果トランジスタ(MOSFET)の後継者と考えられるが、シリコンベースのTFETは一般に低いオン電流、トンネルバリアの大きな抵抗に関する欠点を有する。

【解決手段】より高いオン電流を達成するために、他のシリコン(Si)チャネル中にゲルマニウム(Ge)トンネルバリアを備えたナノワイヤベースのTFETが用いられる。ナノワイヤは、シリコンとゲルマニウムの間の格子不整合が、高い欠陥のある界面とならないように導入される。従来のMOSFET構造に比較して、静的電力の低減と共に動的電力の低減が得られる。これにより、多層ロジックは、ナノワイヤSi/GeTFETを用いることで、非常に高いオンチップトランジスタ密度となる。

(もっと読む)

ナノワイヤ及びナノワイヤを備える装置並びにその製造方法

【課題】新規なナノワイヤ構造を提供し、電子デバイスに応用する。

【解決方法】本発明のナノワイヤ101は、第1の材料から形成された結晶性半導体のナノワイヤ本体104と、前記半導体を構成する元素を一部に含む第2の材料から形成され、ナノワイヤ本体104の表面の少なくとも一部に位置する複数の微粒子103とを備え、ナノワイヤ本体104の表面が平滑である。

(もっと読む)

ゲート誘電体上に完全シリサイド化(FUSI)ゲート電極を選択的に形成する方法、及びその完全シリサイド化ゲート電極を有する半導体デバイス

【課題】 完全シリサイド化ゲート電極及びその作成方法を提供する。

【解決手段】 本発明は、ゲート電極を完全にシリサイド化(FUSI)することにより、1つ又は複数のデバイス領域内に金属ゲート電極を選択的に作成する方法に関する。FUSIの選択的な形成は、従来のn+及びp+ドープ・ポリシリコン電極とは異なる、仕事関数と適合可能な金属ゲート電極をデバイス上に作成することを可能にする。各デバイス領域は、ポリシリコン・ゲート電極又は完全シリサイド化(FUSI)ゲート電極を含む少なくとも1つの電界効果トランジスタ(FET)デバイスからなる。シリコン層及びGe含有層からなるゲート電極が、Ge含有層の選択的除去プロセスと組み合せて用いられる。Ge含有層は、FUSIの仕事関数と適合しない閾値電圧を有するデバイス上では除去されない。FUSIの仕事関数と適合するデバイスは、接合部シリサイド化ステップの前に除去されるGe含有層を有する。ゲート電極の残りの薄いシリコン層は、接合部シリサイド化ステップと同じステップ中に完全にシリサイド化される。

(もっと読む)

電界効果トランジスタ、TFT駆動回路、パネルおよびディスプレイ

【課題】半導体ナノワイヤを用い良好なトランジスタ特性を有する新規な電界効果トランジスタの構造を提供する。

【解決手段】本発明の一例である電界効果トランジスタは、基板40、ゲート電極41、ゲート絶縁膜42がこの順に配置され、ゲート絶縁膜42の上に半導体ナノワイヤ45とソース電極43・ドレイン電極44が設けられている。半導体ナノワイヤ45とソース電極43・ドレイン電極44とのコンタクト領域において、半導体ナノワイヤ45の表面をソース電極43・ドレイン電極44の構成材料が覆っている。

(もっと読む)

半導体発光素子

【課題】高出力及び高輝度、高寿命の半導体発光素子を提供する。

【解決手段】第1/第2導電型半導体層上に其々第1/第2電極を、同一面側に備えた半導体発光素子であり、第1電極は、第1台座部とこれを基点として同方向に延びる2以上の第1延伸部とを備え、第2電極は、第2台座部とこれから第1台座部に近づくように第1延伸部と略同方向に延びる第2延伸部とを備え、2以上の第1延伸部は、其々同方向部分に、第2電極における第1台座部から最も遠い端部を越えて素子外周方向に配置された終端部を有し、一方の第1延伸部は同方向部分に第1台座部が設けられ、他方の第1延伸部は同方向部分で、第1電極と第2電極との間隔が最短となるように配置され、第2延伸部は、他方の第1延伸部の同方向部分と第2台座部との最短間隔及び他方の第1延伸部の同方向部と第2延伸部との最短間隔が同じになるように第2台座部から延伸してなる半導体発光素子。

(もっと読む)

シリサイド・コンタクトとその上のメタライゼーションとの間の接触抵抗を低減する方法及び構造体

【課題】シリサイド・コンタクトとその上のメタライゼーションとの間の接触抵抗を低減する方法及び構造体を提供する。

【解決手段】上に配置される少なくとも1つの電界効果トランジスタを含み、前記少なくとも1つの電界効果トランジスタに隣接して配置されるシリサイド・コンタクト領域16A,16B,16Cを含む、半導体基板12と、前記半導体基板上に配置され、前記少なくとも1つの電界効果トランジスタの上に延び、前記シリサイド・コンタクト領域を露出させるコンタクト開口部20を有する絶縁中間層18と、前記コンタクト開口部内の金属ゲルマニウム化物含有コンタクト材料24とを備える。

(もっと読む)

半導体集積回路及びその作製方法、並びに半導体集積回路を用いた半導体装置

【課題】半導体基板にスルーホールを形成する工程や、半導体基板を裏面から研磨する工程は、非常に長い時間を要し生産性を低下させる要因となる。また、半導体基板を積層する構造であるため、積層して形成された半導体集積回路は厚くなり機械的な柔軟性に劣っている。

【解決手段】複数の基板上に剥離層を形成し、剥離層上に半導体素子、および貫通配線のための開口部を形成する。そして、半導体素子を有する層を基板から剥離し、重ね合わせて積層し、開口部に導電性を有する層を形成して貫通配線を形成することによって半導体集積回路を作製する。

(もっと読む)

II−VI族半導体光変換素子内のオーミック接触のパッシベーションキャップ層

【課題】II-VI族半導体素子において、多層コンタクト層の最表面BeTe層の酸化を防止する。

【解決手段】II-VI族半導体素子は、半導体層10のスタックを含む。オーミク接触34が提供され、このスタックに電気的に結合する。このオーミック接触は、酸化性物質に暴露されるときに、ある酸化速度を有する。パッシベーションキャップ層42は、オーミック接触の上に重なり、オーミック接触の酸化速度よりも小さい酸化速度を有する。

(もっと読む)

シリコン・ナイトライド・キャップを用いて内因性の応力を加えられたシリサイドを有するCMOSデバイスを形成するための構造および方法

【課題】シリコン・ナイトライド・キャップを用いて内因性応力を加えられたシリサイドを有するCMOSデバイスを形成するための構造および方法を提供する。

【解決手段】最初に、FETのS/D領域の上にシリサイド金属Mを含む金属層を形成した後、第一のアニール工程を行って第一の相の金属シリサイド(MSix)を含むS/D金属シリサイド層を形成する。次に、FETの上にシリコン・ナイトライド層を形成した後、第二のアニール工程を行う。第二のアニール工程の間に、金属シリサイドは、第一の相(MSix)から第二の相(MSiy)、ここで×<y、へ変換される。金属シリサイド変換によって、FETのS/D金属シリサイド層の中で体積収縮または膨張のどちらかが引き起こされ、その結果、シリコン・ナイトライド層によって閉じ込められているS/D金属シリサイド層の中では、内因性の引張り応力または圧縮応力が発生する。

(もっと読む)

81 - 100 / 146

[ Back to top ]