Fターム[4M104AA06]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | II−VI族 (146)

Fターム[4M104AA06]に分類される特許

21 - 40 / 146

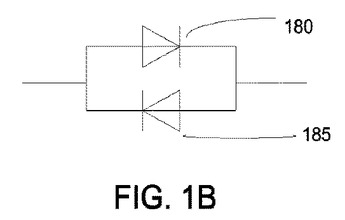

ショットキーダイオードスイッチおよびそれを含むメモリユニット

スイッチング素子は、第1の部分と第2の部分とを有する第1の半導体層と、第1の部分と第2の部分とを有する第2の半導体層と、上記第1の半導体層と上記第2の半導体層との間に配置される絶縁層と、上記第1の半導体層の上記第1の部分と接触して第1の接合部を形成するとともに、上記第2の半導体層の上記第1の部分と接触して第2の接合部を形成する第1の金属コンタクトと、上記第1の半導体層の上記第2の部分と接触して第3の接合部を形成するとともに、上記第2の半導体層の上記第2の部分と接触して第4の接合部を形成する第2の金属コンタクトとを含み、上記第1の接合部と上記第4の接合部とはショットキー接触部であり、上記第2の接合部と上記第3の接合部はオーミック接触部である。  (もっと読む)

(もっと読む)

堆積錫酸カドミウム層のアニール方法および装置

マルチレイヤ構造を製造する方法は、積層体をアニールする工程を含み、該アニール工程は、不活性ガスの存在下で前記積層体を加熱する工程を含むことができ、前記積層体はカドミウムおよび錫を含む層を含む。  (もっと読む)

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

透明な整流性の金属−金属酸化物−半導体接触構造およびその製造方法および使用

本発明は、特に光電子工学、太陽光技術、およびセンサ技術の電子部品において使用するための透明な整流性接触構造ならびにその製造方法に関する。本発明による透明な整流性接触構造は、下記の構成要素:a)透明な半導体、b)金属酸化物、金属硫化物、および/または金属窒化物から成り、透明で絶縁性でなく伝導性でなく、固有抵抗が好ましくは102Ωcm〜107Ωcmの範囲内である層、およびc)透明な導電体から成る層を有し、層b)は半導体a)と層c)の間に形成されており、この層b)の組成は特許明細書の中で詳しく定義されている。 (もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

半導体素子接点

半導体材料の1つの面上に化学的無電解プロセスによって所望の接点材料の酸化物を堆積させる工程と、所望の接点材料の接点を製造するために化学的無電解プロセスによって酸化物を還元する工程とを含む、半導体材料上に電気接点構造を製造する方法が記載される。このような電気接点構造を組み込んでいる半導体素子およびこのような電気接点構造を組み込んでいる半導体素子を製造する方法も記載される。 (もっと読む)

窒化物半導体装置の製造方法

【課題】p型電極のコンタクト抵抗を低減することができる窒化物半導体装置の製造方法を提供する。

【解決手段】n型GaN基板上に、V族原料としてアンモニアとヒドラジン誘導体を用いて、p型GaN層(p型窒化物半導体層)を形成する。次に、p型GaN層にオーミック接触するp側電極を形成する。p型GaN層を形成した後に450℃より高い温度で熱処理を行わない。これにより、p側電極58のコンタクト抵抗を低減することができる。従って、動作電圧を低くすることができるため、発熱による電力消費を低減することができ、高出力でも劣化の少ない長寿命の半導体レーザーを得ることができる。また、コンタクト抵抗が低いため、高速の応答が可能になる。さらに、高温の熱処理を必要としないため、プロセス変動の影響を受けにくく、歩留まりを向上させることができ、低コスト化が可能になる。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

化合物半導体電子デバイス、及び化合物半導体集積電子デバイス

【課題】ウルツ鉱構造の化合物半導体を用いてノーマリ・オフの化合物半導体電子デバイスを提供する。

【解決手段】キャリア走行半導体層15はスペーサ半導体層17と支持体13との間に位置する。基準軸Nxは、支持体13のウルツ鉱のc軸に直交する。電子デバイス11では、基準軸Nxに直交した基準平面R2に沿ってヘテロ接合が延びるので、ピエゾ電界Pzが基準平面R2に平行な方向に向く。ピエゾ電界Pzはヘテロ接合21に沿って延在する内部電界として働き、これはヘテロ接合21の二次元キャリアに作用して、ゲート電極19直下のヘテロ接合における電子濃度が調整される。内部電界の働きによりゲート電極19にゼロボルトが印加されるとき、二次元電子はゲート電極19直下のヘテロ接合21のバンドの屈曲部に実質的に蓄積されず、電子デバイス11はノーマリ・オフ特性を有する。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

リフトオフ方法及び薄膜トランジスタの製造方法

【課題】歩留まりの低下を防止して、製造工程の簡素化を図ることが可能になるとともに、製造コストの低減を図ることができる表示装置及びその製造方法を提供することを目的とする。

【解決手段】半導体ナノワイヤ3とリフトオフレジスト12と金属膜13とが形成された基板1を、気体のマイクロバブルが混合された液体により構成された剥離液に浸漬させることにより、リフトオフレジスト12とともにリフトオフレジスト12上の金属膜13を剥離して、基板2上に金属膜13からなる所定のパターンを形成する。

(もっと読む)

薄膜トランジスタアレイの製造方法及び表示装置

【課題】ソース電極とドレイン電極を均一且つ効率的に製造でき、薄膜トランジスタの半導体特性を低下させない薄膜トランジスタアレイ及びその製造方法を提供する。

【解決手段】基板1上にスキャンライン2を形成する工程と、外部接続用開口部11以外の領域に絶縁層2を形成する工程と、塗布型電極材料を全面に塗布、焼成して塗布電極層を形成した後にエッチングして少なくともソース電極4s及びドレイン電極4dを形成する工程と、ソース電極4s及びドレイン電極4dとを跨ぐ半導体層5を形成する工程と、封止層6を、外部接続用開口部11に露出しているスキャンライン2a上には少なくとも形成しないようにして形成する工程と、封止層6上に表示電極層8を形成した後にエッチングして表示電極8を形成する工程とを有する。この場合において、表示電極形成時のエッチングにより、外部接続用開口部11に露出しているスキャンライン2a上に残った余分な塗布電極層を除去する。

(もっと読む)

金属High−kFETのためのデュアル金属およびデュアル誘電体集積

【課題】本発明は、一つの実施形態において半導体デバイスを形成する方法を提供する。

【解決手段】該方法は、第一導電型領域および第二導電型領域を包含する基板を用意するステップと、基板の第一導電型領域および第二導電型領域の上のゲート誘電体とHigh−kの該ゲート誘電体上を覆う第一金属ゲート導体を包含するゲート・スタックを形成するステップと、第一金属ゲート導体の第一導電型領域中に所在する部分を除去して、第一導電型領域中に所在するゲート誘電体を露出するステップと、基板に対し窒素ベース・プラズマを印加するステップであって、窒素ベース・プラズマは、第一導電型領域中に所在するゲート誘電体を窒化し、第二導電型領域中に所在する第一金属ゲート導体を窒化する、該印加するステップと、少なくとも第一導電型領域中に所在するゲート誘電体上を覆う第二金属ゲート導体を形成するステップと、を含む。

(もっと読む)

半導体構造体およびその製造方法(自己整合型ショットキー・ダイオード)

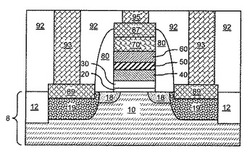

【課題】 自己整合型ショットキー・ダイオード及びその製造方法を提供する

【解決手段】 ショットキー障壁ダイオードは、セミコンダクタ・オン・インシュレータ(SOI)基板内の第2の導電型のドーピングを有するドープ保護環(リング)を含み、さらにダミー・ゲート電極の一方の側の、第2の導電型とは反対型の第1の導電型のドーピングを有する第1導電型ドープ半導体領域を含み、そしてショットキー障壁構造部は他方の側がドープ保護環により囲まれる。ショットキー障壁領域は、側部をダミー・ゲート電極及びドープ保護環により囲むことができる。ドープ保護環は、第2の導電型のドーピングを有するゲート側第2導電型ドープ半導体領域の非金属化部分を含む。ショットキー障壁領域は、側部を、ゲート側ドープ半導体領域及びSTI側ドープ半導体領域を含むドープ保護環により囲むことができる。ショットキー障壁ダイオードの設計構造体もまた提供する。

(もっと読む)

電界効果半導体装置及びその製造方法

【課題】ノーマリオフのHEMTを得ることが困難であった。

【解決手段】本発明に従うヘテロ接合型電界効果半導体装置は、電子走行層31と、第1及び第2の電子供給層32,33と、キャップ層34と、ソース電極8と、ドレイン電極9と、ゲート電極10と、シリコン酸化物から成る絶縁膜11と、p型金属酸化物半導体膜12とを有している。第2の電子供給層33に凹部7が形成され、この凹部7に絶縁膜11とp型金属酸化物半導体膜12とゲート電極10との積層体が配置されている。正孔濃度の高いp型金属酸化物半導体膜12はノーマリオフ特性に寄与し且つゲートリーク電流の低減に寄与する。絶縁膜11はゲートリーク電流の低減に寄与する。

(もっと読む)

電界効果半導体装置の製造方法

【課題】オン抵抗及びゲートリーク電流の小さいノーマリオフ型の電界効果半導体装置及びその製造方法を提供すること。

【解決手段】電流通路を形成するための少なくとも1つの半導体層を有している主半導体領域と、前記主半導体領域の一方の主面上に配置された第1の主電極6と、前記主半導体領域の一方の主面上に前記第1の主電極6から離間して配置された第2の主電極7と、前記主半導体領域の一方の主面上における前記第1の主電極と前記第2の主電極との間に配置されたゲート電極8と、前記主半導体領域と前記ゲート電極8との間に配置された金属酸化物半導体膜10とを備えている電界効果半導体装置の製造方法であって、前記金属酸化物半導体膜10を構成する金属材料を含有する薄膜を、前記主半導体領域上に蒸着させることを特徴とする電界効果半導体装置の製造方法。

(もっと読む)

半導体構造、半導体構造の形成方法、半導体装置の動作方法(高周波の高調波を減少するためのSOIRFスイッチ)

【課題】SOI基板における容量結合を減少した集積回路を提供する。

【解決手段】底部半導体層と同じ導電型のドーパントを含む第1のドープされた半導体領域18及び反対導電型のドーパントを含む第2のドープされた半導体領域28がSOI基板の埋め込み絶縁層20の直下に形成される。第1のドープされた半導体領域18及び第2のドープされた半導体領域28は、共にグランド電位に接続されるか、又は底部半導体層への少数キャリアの順方向バイアス注入に基づく過剰な電流を生じるには不十分は電圧、即ち、0.6V乃至0.8Vを越えない電位差を保って底部半導体層に対して順方向バイアスされる。上部半導体の半導体装置内の電気信号により誘起される電荷層内の電荷は第1及び第2のドープされた半導体領域に接続されている電気的コンタクトを介して引き出され、これにより半導体装置内の高調波信号を減少させる。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】ゲート絶縁層の厚さを大きくすることが容易であり、ゲート絶縁層の影響によるチャネル層の半導体特性の劣化が防止された薄膜トランジスタを提供する。

【解決手段】基板1上にソース電極5及びドレイン電極6を間隔をあけて形成し、次いでこれらソース電極5、ドレイン電極6及び基板1の上に、酸化物半導体層よりなる半導体層4を形成する。この半導体層4の上に有機絶縁層よりなる絶縁層3を形成し、次いでこの絶縁層3上にゲート電極2を形成して、トップゲート構造の薄膜トランジスタ10を得る。酸化物半導体層を形成した後に有機絶縁層を形成するため、酸化物半導体層の形成時に有機絶縁層中の有機物が酸化物半導体層に混入して半導体特性が劣化することが防止される。有機絶縁層は、金属酸化物絶縁層と比べて、厚さを大きくして耐電圧特性を向上させることが非常に容易である。

(もっと読む)

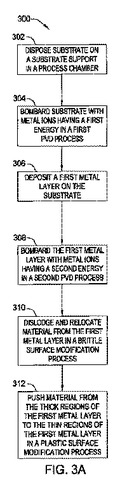

強化された銅のイオン化を伴うPVD銅シードオーバーハング再スパッタ

パターンが形成された基板上に金属を堆積させる方法および装置を提供する。金属層が,第1のエネルギーを有する物理蒸着工程で形成される。第2のエネルギーを用いて金属層上に第2の物理蒸着工程が行われ、ここで、堆積層は、脆性および塑性表面修正工程の相互作用を受け、基板上にほぼ同形の金属層が形成される。  (もっと読む)

(もっと読む)

21 - 40 / 146

[ Back to top ]