Fターム[4M104AA06]の内容

半導体の電極 (138,591) | 基板材料 (12,576) | 化合物半導体(半絶縁性基板を含む) (3,646) | II−VI族 (146)

Fターム[4M104AA06]に分類される特許

121 - 140 / 146

二重の閾値電圧制御手段を有する低閾値電圧の半導体デバイス

【課題】 Si又はGeの高い含有量を有する高k誘電体を絶縁中間層と組み合わせることによって、及び/又は、チャネル工学処理によって、閾値電圧及びフラットバンド電圧のシフトを低減させること。

【解決手段】 SiO2より大きい誘電率、及び、50%を超えるGe又はSi含有量を有する誘電体材料と、材料スタック工学処理によって閾値電圧/フラットバンド電圧を調整するための少なくとも1つの他の手段とを含む、半導体構造体、特にpFETが提供される。本発明において考慮される他の手段は、例えば、電荷を固定するために誘電体の上に絶縁中間層を用いること、及び/又は、工学処理されたチャンネル領域を形成することを含む。本発明はまた、このようなCMOS構造体を製造する方法にも関する。

(もっと読む)

逆ソース/ドレイン金属コンタクトを有する電界効果トランジスタ(FET)及びその製造方法

【課題】 コンタクト間隔及び寄生容量の問題に対する解決策を提供する、改善されたFET設計を構築する。

【解決手段】 本発明は、下方の第1の誘電体層内に配置された下部と上方の第2の誘電体層内に配置された上部とを有する逆ソース/ドレイン金属コンタクトを含む電界効果トランジスタ(FET)に関する。逆ソース/ドレイン金属コンタクトの下部は、上部より大きい断面積を有する。好ましくは、逆ソース/ドレイン金属コンタクトの下部は、約0.03μm2から約3.15μm2の範囲の断面積を有し、こうした逆ソース/ドレイン金属コンタクトは、約0.001μmから約5μmの範囲の距離だけ、FETのゲート電極から間隔を空けて配置される。

(もっと読む)

トランジスタおよび電子デバイス

【課題】チャネル層として酸化亜鉛を用いたトランジスタにおいて、チャネル層界面における電荷整合性および格子整合性を向上させる。

【解決手段】基板2上に形成したバッファ層3上に、酸化亜鉛をエピタキシャル成長させ、チャネル層4を形成する。さらに、その上に、Mg1-xCaxOをエピタキシャル成長させて界面改質層7を形成し、界面改質層7を介してゲート絶縁層8およびゲート電極9を形成する。

(もっと読む)

p型GaN上のオーム接触構造

【課題】 発光ダイオードのような半導体装置の製造に組み込まれている特定の材料を含む半導体材料上に設けることができる実効的なオーム接触構造を提供する。

【解決手段】 本発明のオーム接触構造は、p型GaNに基づく材料からなる層(225、350、425、550)と、金属接触をもたらすように構成されている金属からなる層(205、305、405、505)と、第1のVI族元素からなるp型II-VI族化合物半導体材料からなり、p型GaNに基づく材料からなる層に隣接して位置する第1の層(220、345、420、545)と、第1のVI族元素とは異なる第2のVI族元素からなるp型II-VI族化合物半導体材料からなり、金属からなる層に隣接して位置する第2の層(220、345、420、545)とからなる。

(もっと読む)

膜パターン及びその製造方法

【課題】膜パターンの機能(導電膜の場合は導電性)を阻害させることなく、基体に対する密着力が高い膜パターンを、液滴吐出法により提供する。

【解決手段】基板上にインクジェットから液滴を吐出し、乾燥固化し、密着性機能を持つドットアレイ10を形成する。このときドット直径以上のピッチで形成する。密着性機能を持つドットアレイの周りに導電性機能を持つドットアレイ11をドット直径以上のピッチで液滴吐出し、乾燥固化する。この後、導電性機能を持つドットの間にドットが一部重ねて連結するように導電性機能を持つドットアレイ12,13,14を同様の方法で形成する。密着性機能を持つドットアレイは機能性ドットアレイは基体表面に選択的に形成できるので、表面に電極等が形成されている基板にも適用できる。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、透明基板に遮光性を持たせてウェハ検出を容易にするとともに、微細なリソグラフを可能にする。

【解決手段】 透明基板1或いは透明半導体層2の表面及び裏面の少なくとも一方に、少なくとも一辺の長さが1μm以下の微細加工領域4を除いた領域に可視光を遮光する遮光膜3を設けて、プロセス装置におけるセンサによるウェハ検知が可能になるとともに、露光時に透明基板1の裏面から露光光6の反射が軽減され、開口の広がりを最小限にとどめる。

(もっと読む)

トランジスタ

【課題】 成膜中及び成膜後の雰囲気からの水分や酸素の吸着及び拡散を抑制し、全体として高比誘電率を有する絶縁層を提供することを目的とする。

【解決手段】 チャネルとチャネル上に絶縁層を有するトランジスタ1であって、絶縁層はチャネル側から第1の絶縁層5、第2の絶縁層4、第3の絶縁層3を有しており、第2の絶縁層4が第1の絶縁層5及び第3の絶縁層3よりも比誘電率が高く、第1の絶縁層5と第2の絶縁層4及び第2の絶縁層4と第3の絶縁層3各々の界面にはアモルファス領域が存在する。

(もっと読む)

応力が加えられたゲート金属シリサイド層を含む高性能MOSFET及びその製造方法

【課題】 応力が加えられたゲート金属シリサイド層を含む高性能の金属酸化物半導体電界効果トランジスタ(MOSFET)及び高性能MOSFETを製造する方法を提供すること。

【解決手段】 本発明は、ソース領域、ドレイン領域、チャネル領域、ゲート誘電体層、ゲート電極及び1つ又は複数のゲート側壁スペーサを備えた少なくとも1つの電界効果トランジスタ(FET)を含む半導体デバイスに関する。このようなFETのゲート電極は、1つ又は複数のゲート側壁スペーサによって横方向に制限され、かつ、FETのチャネル領域内に応力を生じさせるように配置され構成される内因性応力が加えられたゲート金属シリサイド層を含む。半導体デバイスは、少なくとも1つのp−FETを含むことが好ましく、p−チャネルFETは、1つ又は複数のゲート側壁スペーサによって横方向に制限され、かつ、FETのp−チャネル内に圧縮応力を生じさせるように配置され構成される内因性応力が加えられたゲート金属シリサイド層を備えたゲート電極を有することがより好ましい。

(もっと読む)

半導体装置、演算増幅器および半導体装置の製造方法

【課題】 ソース/ドレイン接合における接合リーク電流を抑制しつつ、バックゲートバイアスをトランジスタごとに個別に制御する。

【解決手段】 不純物のイオン注入を半導体基板11に局所的に行い、ウェル12a、12bを半導体基板11に形成してから、半導体基板11の表面に絶縁層13を形成し、単結晶半導体層23を介して半導体基板11上の絶縁層13上に半導体基板21を貼り合わせた後、多孔質層22をエッチング除去することにより、多孔質層22を境界として半導体基板21を単結晶半導体層23から剥離する。

(もっと読む)

半導体素子、電極形成方法及び半導体素子の製造方法

【課題】低動作電圧を実現することができ、信頼性の向上が可能な半導体素子を提供する。

【解決手段】p型窒化物半導体層と、窒化物半導体層表面上の酸化パラジウム膜30を含むp側電極18とを備える。

(もっと読む)

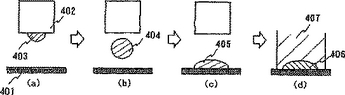

薄膜トランジスタの製造方法

【課題】 蒸着リフトオフという高価な工程を使用せずに、ゲート電極、ソース電極およびドレイン電極の位置合わせ精度を向上させ、ゲート電極に対するソース電極およびドレイン電極の重なりを小さい薄膜トランジスタ製造方法の提供。

【解決手段】本発明の薄膜トランジスタの製造方法は、透明絶縁基板上にゲート電極を形成する工程と、前記透明絶縁基板と前記ゲート電極を覆うようにゲート絶縁膜を形成する工程と、半導体層を形成する工程と、レジストを塗布する工程と、裏露光によって前記ゲート電極に自己整合したレジストパターンを形成する工程と、ソース電極とドレイン電極を形成する工程と、レジストを除去する工程とを少なくとも有する薄膜トランジスタの製造方法であって、前記ソース電極とドレイン電極を形成する工程が、金属ナノ粒子を含む液体を塗布する工程を含む。

(もっと読む)

発光ダイオード

ドーパントによる結晶の歪み・欠陥が生じず、発光効率が高く、不要な波長の発光が無く、発光波長を広く選択できる、発光ダイオードを提供する。ドーパントを添加しない同時二極性半導体を発光層とし、これに電子注入用電極すなわちn電極と、正孔注入用電極すなわちp電極とを接合して、発光ダイオードとした。  (もっと読む)

(もっと読む)

半導体装置、電子機器、半導体装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な半導体装置、表示装置及びその作製技術を提供することを目的とする。また、それらの半導体装置、表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】節を有する形状の導電層を、均一な間隔をもって隣接して形成する。隣接する導電層において、吐出する液滴の中心の位置が線幅方向に一致しないように、配線の長さ方向にずらして吐出する。液滴の中心がずれているので、導電層同士の線幅の最大個所(節の最大値)同士が隣接することがなく、より狭い間隔に隣接して設けることができる。

(もっと読む)

ゲート誘電体上にゲート金属または他の導体材料または半導体材料を電着するための方法(ゲート誘電体貫通電流を用いた電気化学処理によるゲート・スタック技術)

【課題】 ゲート誘電体等の誘電体の上に直接ゲート金属または他の導体材料または半導体材料を電気めっきするための方法を提供する。

【解決手段】 この方法は、基板、誘電体の層、および電解液または溶融物を選択することを含み、基板、誘電体層、および電解液または溶融物の組み合わせによって、基板から誘電体層を介して電解液または溶融物へと電気化学電流を流すことができる。また、誘電体貫通電流を用いて誘電体の電気化学的な変更を行うための方法も提供する。

(もっと読む)

n−FET用途のためのHfSiN金属を形成する方法

【課題】 高k誘電体及び界面層を含むゲート・スタック上に、熱的に安定した新しい金属化合物を提供すること。

【解決手段】 高k誘電体及び界面層を含むゲート・スタック上に、約4.0eVから約4.5eVまで、好ましくは約4.3eVの仕事関数を有する、熱的に安定したn型金属であるHfSiNを含む金属化合物である。さらに、(約1000℃のオーダーの)高温でHfSiN/高k誘電体/界面層のスタックをアニールした後、界面層が減少され、よって、ゲート・スタックは、TaSiNを用いて達成することができない、非常に薄い等価酸化物厚(伝統的には、12Å)をもたらす。

(もっと読む)

高い誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法

【課題】

高誘電率のSiO2ゲート積層体上に熱的に安定したp型金属炭化物としてTiCを製造する方法を提供する。

【解決手段】

本発明の金属化合物は、TiCを含み、約4.75乃至約5.3eV、望ましくは、約5eVの仕事関数を有し且つ高誘電率の誘電体および界面層を含むゲート積層体上で熱的に安定する。更に、そのTiC金属化合物は、非常に意欲的な等価酸化膜厚(EOT)およびp型金属酸化物半導体(pMOS)装置における14Åよりも小さい反転層厚へのスケーリングを可能にする1000℃においても非常に効率的な酸素拡散バリアである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 パッド電極下に能動層が配置されている場合においても、パッド電極下における密着性を確保しつつ、バリアメタル構造を能動面上に安定して形成できるようにする。

【解決手段】 不純物拡散層5a、5bの表面が覆われるようにして層間絶縁膜6上にバリアメタル膜8を形成し、フォトリソグラフィー技術を用いることにより、開口部7が覆われるようにしてパッド電極16下に配置されるバリアメタル膜8の表面を露出させるレジストパターンRを形成し、レジストパターンRをマスクとして、バリアメタル膜8をエッチングすることにより、パッド電極16下に配置される層間絶縁膜6上のバリアメタル膜8を除去し、バリアメタル膜8を介してゲート電極4および不純物拡散層5a、5bに接続された配線層9を層間絶縁膜6上に形成し、ゲート電極4および不純物拡散層5a、5b上に配置されたパッド電極16を形成する。

(もっと読む)

電極材料および半導体素子

II−VI族化合物半導体におけるp型オーミック接触電極の形成手法として、低抵抗で安定かつ毒性がなく生産性にすぐれた電極を形成する材料を提供し、すぐれた半導体素子を提供する。組成式AXBYCZ(A:1B族金属元素から選ばれる少なくとも1種の元素、B:8族金属元素から選ばれる少なくとも1種の元素、C:SあるいはSeから選ばれる少なくとも1種の元素)で示される材料からなる半導体電極材料とした。ただし、X,Y,ZはX+Y+Z=1であり、0.20≦X≦0.35,0.17≦Y≦0.30,0.45≦Z≦0.55とする。  (もっと読む)

(もっと読む)

液滴吐出装置、パターンの形成方法、および半導体装置の製造方法

本発明では液滴吐出装置から吐出された液滴が基板に着弾した後の位置制御を改善することが可能なパターンの作製方法を提供する。また着弾後の液滴位置精度を改善することが可能な液滴吐出装置を提供する。更には、本発明の液滴吐出装置を用いた半導体装置の製造方法を提供する。

本発明は、吐出部から吐出された液滴、又は液滴を着弾する基板にレーザ光を照射して、液滴の着弾位置を制御することを特徴とする。本発明によりフォトリソグラフィー工程を用いることなくパターンを形成することが可能である。  (もっと読む)

(もっと読む)

表面改質によるパターン化方法

(a)再配置可能なアパーチャマスクを基板の近くに配置する工程と、(b)基板の部分を表面改質処理に選択的に曝す工程であって、曝された部分が、アパーチャマスクの1つ以上のアパーチャによって画定される工程とによって表面改質をパターン化する方法。 (もっと読む)

121 - 140 / 146

[ Back to top ]