Fターム[4M104BB01]の内容

Fターム[4M104BB01]に分類される特許

2,061 - 2,080 / 2,965

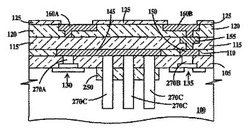

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】 低抵抗及び低インダクタンスの裏面貫通ビア及びその製造法

【解決手段】 裏面コンタクト構造体及びその構造体を製造する方法を提供する。この方法は、表面及び対向する裏面を有する基板(100)内に誘電体分離(250)を形成するステップと、基板(100)の表面上に第1誘電体層(105)を形成するステップと、誘電体分離(250)の周囲上及び内部に位置合せされ、誘電体分離(250)まで延びるトレンチ(265C)を第1誘電体層(105)内に形成するステップと、第1誘電体層(105)内に形成されたトレンチ(265C)を、誘電体分離(250)を貫通して基板(100)の厚さより小さな深さ(D1)まで基板(100)内部に延ばすステップと、トレンチ(265C)を充填し、且つトレンチ(265C)の上面を第1誘電体層(105)の上面と同一平面にして、導電性貫通ビア(270C)を形成するステップと、基板(100)の裏面から基板(100)を薄くして貫通ビア(270C)を露出させるステップとを含む。

(もっと読む)

シリコンワイヤの製造方法

【課題】本発明は、銅を触媒としてシリコンワイヤを成長する方法に関する。

【解決手段】本発明に係るシリコンワイヤの成長方法は、基材を提供する段階と、前記基材に複数の銅粒子からなる触媒層を形成する段階と、700Torrの圧力で、保護ガス及び反応ガスを導入して、前記触媒層が形成された前記基材を450℃以上程度に加熱して、前記基材にシリコンワイヤを成長させる段階と、を含む。

(もっと読む)

半導体装置

【課題】 NBTI劣化を抑制することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】 半導体装置の製造方法は、n型領域を有するシリコン基板の上に、窒素を含む酸化シリコンを用いたゲート絶縁膜と、ホウ素を含むシリコンを用いたゲート電極とを形成する工程と、ゲート電極両側の前記シリコン基板内にp型ソース/ドレイン領域を形成する工程と、ゲート電極の側壁上に酸化シリコンを用いてサイドウォールスペーサを形成する工程と、ゲート電極、サイドウォールスペーサを覆い、平坦化された表面を有する層間絶縁膜を形成する工程と、層間絶縁膜の平坦化された表面から内部に向って凹部を形成し,該凹部内に下地のバリア層とその上の銅領域を含む銅配線とを埋め込む工程と、銅配線の上に炭化シリコン層を形成する工程と、 前記炭化シリコン層の上方に絶縁層をCVDで形成する工程と、を含むことを特徴とする。

(もっと読む)

電界緩和機能を有するIII族窒化物電力半導体

素子の耐圧性を改善するために、ゲートの周囲の電界を緩和する電界緩和機能を含むIII族窒化物電力半導体素子。 (もっと読む)

半導体装置

【課題】差動アンプの特性を向上させることができるMOS型トランジスタを有する半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体基板上にゲート電極と、一対のソース領域と、一対のドレイン領域とを有するMOS型トランジスタを備え、ゲート電極が、十字状であり、一対のソース領域及び一対のドレイン領域は、それぞれ、ゲート電極の中心に対し対角状に配置され、一対のソース領域同士及び一対のドレイン領域同士は、電気的に接続されることを特徴とする。

(もっと読む)

複合キャップによりシリサイド形成を改善するためのエア・ブレーク

【課題】 複合キャップによりシリサイド形成を改善するためのエア・ブレーク

【解決手段】 シリサイド応力を調節するための構造体及び方法、具体的にはn−FET性能を最適化するようにn−FETのゲート導体上に引張り応力含有シリサイド領域を造成する(402)ための構造体及び方法が開示される。より具体的には、n−FET構造体の上に第1金属層−保護キャップ層−第2金属層スタックが形成される(403−406)。しかしながら、第2金属層の堆積(406)の前に、保護層を空気に曝す(405)。このエア・ブレークのステップは、保護キャップ層と第2金属層の間の付着性を変化させ、それゆえに、シリサイド形成中に第1金属層に付与される応力に影響を与える。その結果として、n−FET性能に最適な引張り応力のより大きなシリサイドが生成される。さらに、この方法は、このような引張り応力含有シリサイド領域を、比較的薄い第1金属層−保護キャップ層−第2金属層スタック、より具体的には比較的薄い第2金属層を用いて形成することを可能にし、ゲート導体と側壁スペーサの間の接合部に蓄積される機械的エネルギーを最小にしてシリコン・ブリッジ形成を防止する。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】3マスク工程を通じて良好なパターンデザインを形成すると共に、段差の除去できる薄膜トランジスタ基板の製造方法を提供する。

【解決手段】本発明の薄膜トランジスタ基板の製造方法は、薄膜トランジスタ140が形成されたゲート絶縁膜125を覆う保護膜150上にコンタクトホール及び画素電極160が形成される領域をオープンさせるための第1フォトレジストパターンを形成する段階、第1フォトレジストパターンが形成された保護膜150上に透明導電膜を全面蒸着させた後、コンタクトホール及び画素電極160が形成される領域以外に形成された透明導電膜を露出させる第2フォトレジストパターンを形成する段階、第2フォトレジストパターンにより露出された透明導電膜をエッチング処理した後、保護膜150上に残留する第1及び第2フォトレジストパターンを除去して、保護膜150上にコンタクトホール及び画素電極160を形成する段階を含む。

(もっと読む)

金属ゲート電極及びポリゲート電極を有する高性能回路

【課題】 高kの金属誘電体スタックからなるゲート電極構造により、CMOSのゲートポリシリコンの空乏化を阻止する。

【解決手段】 本発明によると、nFETデバイス又はpFETデバイスの少なくとも一方が、薄膜化されたSi含有電極すなわちポリシリコン電極と、該Si含有電極上の第1の金属とを有するゲート電極スタックを含み、他方のデバイスが、薄膜化されたSi含有電極を有さず、少なくとも第1の金属ゲートを有するゲート電極スタックを含む、半導体構造が提供される。

(もっと読む)

炭化珪素ディンプル基板

第1主表面と、第1主表面に対向した第2主表面とを有する、高熱伝導性の基板を含むディンプル基板およびその製造方法。活性エピタキシャル層が、基板の第1主表面の上に形成される。ディンプルが、第2主表面から基板中を第1主表面に向かって延びるように形成される。低抵抗材料からなる電気コンタクトが、第2主表面の上とディンプルの中に形成される。低抵抗で低損失のバックコンタクトがこのように、基板を効果的なヒートシンクとして維持しながら形成される。  (もっと読む)

(もっと読む)

炭化珪素半導体装置、炭化珪素半導体装置の製造方法、炭化珪素半導体装置中の遷移金属シリサイドと金属膜との接合体及び炭化珪素半導体装置中の遷移金属シリサイドと金属膜との接合体の製造方法

【課題】シリサイド電極に被着させた上部導体膜の剥離を起こさない炭化珪素半導体装置、炭化珪素半導体装置の製造方法、炭化珪素半導体装置中の遷移金属シリサイドと金属膜との接合体及び炭化珪素半導体装置中の遷移金属シリサイドと金属膜との接合体の製造方法を提供すること。

【解決手段】n型SiC基板1に、Niなどのコンタクト母材を被着させ、n型SiC基板1と固相反応させてシリサイド電極を形成し、該シリサイド電極中に生成している炭素の少なくとも一部を該電極外部に排出させ、それを除去して、炭素含有量が、モル数で比較して、珪素含有量よりも少ない炭素低含有シリサイド電極52とし、炭素低含有シリサイド電極52上に上部導体膜3を被着させたことを特徴とする炭化珪素半導体装置を構成する。

(もっと読む)

異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造および方法

【課題】異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造、方法などを提示すること。

【解決手段】このMOSFET回路は、コンタクト線(500、1300)と、コンタクト線(500、1300)の近くに位置するゲート(310、1210)とを含む。コンタクト線(500、1300)は、ゲート(310、1210)の高さよりも低い高さを含む。このMOSFET回路はさらに、ゲート(310、1210)の近くに位置するゲート・スペーサ(710、715、1610、1615)を含み、コンタクト線(500、1300)とゲート(310、1210)との間のコンタクト線(500、1300)の近くに位置するコンタクト線スペーサを含まない。

(もっと読む)

半導体素子のリセスチャネル用トレンチ形成方法

【課題】半導体素子のリセスチャネル用トレンチ形成方法を提供する。

【解決手段】半導体基板上に、トレンチが形成される第1領域を露出させるハードマスク膜パターンを形成する段階と、ハードマスク膜パターンをマスクとした第1エッチング工程を行って第1トレンチを形成し、ハードマスク膜パターンは除去する段階と、第1トレンチを含む半導体基板上にバリア膜を形成する段階と、バリア膜上に第1トレンチを露出する感光膜を含むイオン注入マスク膜を形成する段階と、イオン注入マスク膜及びバリア膜を用いて第1トレンチ下部の半導体基板内にイオン注入層を形成する段階と、イオン注入マスク膜及びバリア膜をマスクとして第2エッチング工程を行って球状の第2トレンチを形成し、第1トレンチ及び第2トレンチからなるバルブタイプのリセスチャネル用トレンチを形成する段階と、イオン注入マスク膜及びバリア膜を除去する段階と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】ソース・ドレイン領域にシリサイド層が設けられたトランジスタの接合リーク電流を抑制する。

【解決手段】シリコン基板101の素子形成面にゲート電極105を形成した後、シリコン基板101に絶縁膜を形成する。絶縁膜をエッチバックしてゲート電極105の側壁を覆うサイドウォール107を形成するとともに、サイドウォール107の側方のソース・ドレイン領域109が形成される領域において、シリコン基板101の素子形成面をエッチング除去し、素子形成面に略水平な掘り下げ面を形成する。その後、ゲート電極105の周囲のシリコン基板101に不純物をイオン注入し、ソース・ドレイン領域109を形成する。そして、ゲート電極105が設けられたシリコン基板101の素子形成面にNi膜を形成し、Ni膜とシリコン基板101とを反応させて、Niシリサイド層111を形成する。

(もっと読む)

ゲートの頂部が拡張された半導体トランジスタ

【課題】ゲートの頂部が拡張された半導体トランジスタ(100)およびそれを形成するための方法を提供する。

【解決手段】ゲートの頂部が拡張された半導体トランジスタ(100)は、(a)チャネル領域ならびに第1および第2のソース/ドレイン領域(840および850)を含み、チャネル領域が、第1および第2のソース/ドレイン領域(840および850)の間に配置された半導体領域と、(b)チャネル領域と直接物理的に接触しているゲート誘電体領域(411)と、(c)頂部(512)および底部(515)を含むゲート電極領域(510)とを含む。底部(515)は、ゲート誘電体領域(411)と直接物理的に接触している。頂部(512)の第1の幅(517)は、底部(515)の第2の幅(516)より大きい。ゲート電極領域(510)は、ゲート誘電体領域(411)によってチャネル領域から電気的に絶縁されている。

(もっと読む)

高性能CMOS回路及びその製造方法

【課題】 ゲート誘電体及び金属ゲート導体を有するn−FETゲート・スタックと、ゲート誘電体層及びシリコン含有ゲート導体を有するp−FETゲート・スタックとを含むCMOS回路を提供する。

【解決手段】 本発明は、各々が少なくとも第1のゲート・スタック及び第2のゲート・スタックを含有する高性能相補型金属酸化膜半導体(CMOS)回路に関する。第1のゲート・スタックは、半導体基板内の第1のデバイス領域(例えば、n−FETデバイス領域のような)の上に配置され、少なくとも、下から上に、ゲート誘電体層、金属ゲート導体及びシリコン含有ゲート導体を含む。第2のゲート・スタックは、半導体基板内の第2のデバイス領域(例えば、p−FETデバイス領域のような)の上に配置され、少なくとも、下から上に、ゲート誘電体層及びシリコン含有ゲート導体を含む。第1のゲート・スタック及び第2のゲート・スタックは、本発明の種々の統合された方法で半導体基板の上に形成することができる。

(もっと読む)

プロセス変動に耐性を有するダイオード、同ダイオードを有するスタンダードセル、同ダイオードを含むタグ及びセンサ、並びに同ダイオードを製造する方法

【課題】プロセス変動に耐性を有するダイオード及びダイオード接続薄膜トランジスタ(TFT)を提供する。

【解決手段】ダイオード又はTFTを含む印刷又はパターニング構造(例えば、回路)、これらを製造する方法、並びに、これらの識別タグ及びセンサへの応用を開示する。相補型のダイオード対又はダイオード接続TFTを直列に含む印刷された構造は、印刷又はレーザ描画技術を用いて製造したダイオードの閾値電圧(Vt)を安定化することができる。NMOS TFTのVt(Vtn)とPMOS TFTのVt(Vtp)の間の分離を利用して、印刷又はレーザ描画のダイオードの順方向電圧降下の安定性を確立又は向上する。更なる応用は、参照電圧発生器、電圧クランプ回路、参照又は差動信号伝送ラインにおける電圧を制御する方法、並びにRFID及びEASタグ及びセンサに関する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、動作領域にSi/SiCのヘテロ接合を用い、SiCに依ってnチャネル・トランジスタ及びpチャネル・トランジスタそれぞれに好適な歪みを印加できるようにして超高速の半導体装置を実現しようとする。

【解決手段】 半導体装置に含まれるnチャネル絶縁ゲート型FETに於いては、Si層1上に形成されたSiC層2と、SiC層2上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成されたゲート電極4と、Si層1上に形成されたSiC層2のうちソース領域5及びドレイン領域6を覆う部分の上に形成されてSiに比較して格子定数が小さく且つSiCに近い格子定数をもつ物質で構成された層、即ち、3C−SiC層8とを備える。

(もっと読む)

半導体装置

【課題】トレンチゲート型の半導体装置において、ゲート電極内に発生するボイドによるオン抵抗の増加、耐圧や破壊耐量の低下等の問題を生じさせることを効果的に防止する。

【解決手段】トレンチゲート型のMOSトランジスタにおいて、トレンチ15が形成され、このトレンチにゲート絶縁膜16を介してゲート電極が埋め込まれる。ゲート電極は、ゲート絶縁膜16に沿ってトレンチ15内部に凹部を有するように形成される第1のゲート電極17Aと、この凹部側の表面に沿って形成される層間絶縁膜18と、凹部を埋め込むように形成され第1のゲート電極17と同一の材料からなる第2のゲート電極19Aとを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート絶縁膜に接するゲート電極の空乏化を抑制しながら、ゲート電極の仕事関数の調整を効率的に行うことが可能な半導体装置およびその製造方法を提供する。

【解決手段】 p型シリコン基板1、埋め込み酸化膜2、及び単結晶シリコン層3から構成されるSOI基板4において、単結晶シリコン層3にソース領域10およびドレイン領域11を備える。また、ソース領域10とドレイン領域11との間の単結晶シリコン層3の表面側はチャネル層3aとして機能する。単結晶シリコン層3(チャネル層3a)の上にはゲート絶縁膜5が形成される。ゲート絶縁膜5上には、窒化チタン(TiN)からなる金属粒子6a,6b、及びポリシリコン膜7から構成されるポリシリコンゲート電極8が設けられる。ここで、TiNからなる金属粒子は、ゲート絶縁膜5に接する部分6aと接しない部分6bからなる。

(もっと読む)

半導体装置

【課題】可及的に簡略な構成で、かつ高集積度、高性能の半導体装置を得ることを可能にする。

【解決手段】半導体基板1上に板状に設けられた第1導電型の第1半導体領域3と、第1半導体領域の第1側面に設けられた第1強誘電体絶縁膜4と、第1強誘電体絶縁膜の第1半導体領域と反対側の面に設けられた第1ゲート電極6と、第1半導体領域の第2側面に設けられた第2強誘電体絶縁膜5と、第2強誘電体絶縁膜の第1半導体領域と反対側の面に設けられた第2ゲート電極7と、第1及び第2ゲート電極に挟まれるように第1半導体領域に形成されるチャネル領域と、チャネル領域の両側の第1半導体領域に設けられた第2導電型の第1ソース・ドレイン領域8と、を備え、第1半導体領域の厚さが第1半導体領域の不純物濃度で決まる空乏層の最大厚さの二倍よりも薄い。

(もっと読む)

2,061 - 2,080 / 2,965

[ Back to top ]