Fターム[4M104BB06]の内容

Fターム[4M104BB06]に分類される特許

161 - 180 / 1,420

窒化ガリウム系半導体素子及び窒化ガリウム系半導体素子の製造方法

【課題】窒化ガリウム系半導体素子及びその製造方法を提供する。

【解決手段】導電性放熱基板(すなわち、熱伝導性基板)、放熱基板上に備わったGaN系多重層及びGaN系多重層上に備わったショットキー電極を含む窒化ガリウム系半導体素子である。該GaN系多重層は、放熱基板側に備わったAlGaN層及びショットキー電極側に備わったGaN層を含むことができる。かような窒化ガリウム系半導体素子の製造時、ウェーハボンディング(またはメッキ)及びレーザ・リフトオフ工程を利用することができる。

(もっと読む)

半導体装置の製造方法

【課題】Geをチャネル材料に用いても、素子特性の劣化を抑制することを可能にする。

【解決手段】Geを含むp型半導体領域上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、前記半導体領域の、前記ゲート電極の両側に位置する第1および第2領域に、有機金属錯体および酸化剤を交互に供給して金属酸化物を堆積する工程と、前記金属酸化物の上に金属膜を堆積する工程と、熱処理を行うことにより、前記半導体領域および前記金属酸化物と、前記金属膜とを反応させて前記第1および第2領域に金属半導体化合物層を形成するとともに前記金属半導体化合物層と前記半導体領域との界面に金属偏析層を形成する工程と、を備えている。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

半導体発光素子

【課題】正負一対の電極が半導体層を挟んで形成された半導体発光素子において、電極間の電流密度を均一にし、素子全体の発光分布を改善する。

【解決手段】半導体層2と、半導体層2の上面に互いに対向するようにかつ互い違いとなるように並列して配置された複数の第1電極3と、半導体層2の下面に配置された第2電極4と、を備える半導体発光素子10であって、第1電極3は、外部と接続するための外部接続部3aと、半導体層2の上面における中央領域の方向に延伸した第1延伸部3bと、第1延伸部3bとは反対方向であって、半導体層2の周縁内側まで延伸した第2延伸部3cと、を備え、半導体層2の上面で対向する第1電極3の第1延伸部3bのそれぞれは、中央領域において、その先端側が隣り合う方向で対向するように配置される。

(もっと読む)

化合物半導体装置

【課題】窒化物化合物半導体装置において、ゲートリーク電流を抑制する。

【解決手段】化合物半導体装置20は、基板21と、前記基板上方に形成された窒化物半導体よりなるキャリア走行層22を含む半導体積層構造と、前記半導体積層構造上方に形成されたゲート電極26、ソース電極27A、ドレイン電極27Bと、前記半導体積層構造上方であって、ゲート電極とソース電極の間、及び、ゲート電極とドレイン電極との間に形成された絶縁膜28と、前記絶縁膜のうち、ゲート電極とソース電極の間、及びゲート電極とドレイン電極の間に形成された開口と、前記開口に埋め込まれたアルミナ膜29と、を備える。

(もっと読む)

導電性の厚い金属電極を作成する方法

【課題】安定な金属ナノ粒子組成物を用いて、数μmの厚みを有し、高いアスペクト比と、低いアニーリング温度を有するような導電性構造を調製するのに適した方法を提供する。

【解決手段】基板の上に導電性部分を作成する方法であって、可とう性のスタンプを金属ナノ粒子組成物で満たすことと、金属ナノ粒子組成物を基板の上に堆積させることと、堆積させている間または堆積させた後に、堆積した金属ナノ粒子組成物を加熱して導電性部分を作成することとを含む、方法。

(もっと読む)

III族窒化物半導体発光素子を製造する方法、及びIII族窒化物半導体発光素子

【課題】良好なオーミック接触を有するIII族窒化物半導体発光素子が提供される。

【解決手段】このIII族窒化物半導体発光素子では、接合JCが窒化ガリウム系半導体層のc軸に直交する基準面に対して傾斜しており、電極がこの窒化ガリウム系半導体層の半極性面に接合する。しかしながら、この窒化ガリウム系半導体層における酸素濃度が、接合JCを形成するように成長された窒化ガリウム系半導体層における酸素濃度は低減される。この窒化ガリウム系半導体層の半極性面に電極が接合を成すので、金属/半導体接合は良好なオーミック特性を示す。

(もっと読む)

半導体整流装置

【課題】十分なサージ電流耐性を有し、かつ、信頼性の向上するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】第1導電型の第1のワイドバンドギャップ半導体領域16と、第1の半導体領域に挟まれて形成される第2導電型の第2のワイドバンドギャップ半導体領域18とを備えている。また、少なくとも一部が第2の半導体領域に接続され、第1の半導体領域に挟まれて形成され、第2の半導体領域より幅の狭い、複数の第2導電型の第3のワイドバンドギャップ半導体領域32を備えている。ここで、第3の半導体領域の長手方向を第1導電型の半導体層の表面に投影した方向が、第1導電型の半導体層の表面から裏面に向かう方向に対し、90±30度の角度を有している。また、第3の半導体領域の間隔が、第1導電型のワイドバンドギャップ半導体層の厚さをdとする場合に2d×tan18°以上である。

(もっと読む)

半導体発光素子及びその製造方法

【課題】高輝度化の半導体発光素子及びその製造方法を提供する。

【解決手段】半導体発光素子は、第1導電形の第1半導体層と、第2導電形の第2半導体層と、前記第1半導体層と前記第2半導体層との間に設けられた発光層と、第1電極層と、第2電極層と、を備える。第1電極層は、第2半導体層の第1半導体層とは反対側に設けられ、第2半導体層と接する金属部と、第1半導体層から第2半導体層に向かう方向に沿って金属部を貫通し前記方向に沿って見たときの形状の円相当直径が10ナノメートル以上5マイクロメートル以下である複数の開口部と、を有する。第2電極層は、第1半導体層と導通する。第2半導体層は、金属部に接する凸部と、開口部の底部において凸部よりも前記方向に沿って後退した凹部と、を有する。

(もっと読む)

成膜方法、半導体装置及びその製造方法、並びに基板処理装置

【課題】真空装置を使用せずに、トランジスタ等の半導体装置に適用できるMOS構造の積層膜を形成する。

【解決手段】成膜方法は、半導体膜3を有する基板に、ポリシラン溶液を塗布し、半導体膜3上にポリシラン膜5を形成する工程(STEP1)と、ポリシラン膜5上に、金属塩溶液を塗布し、金属イオン含有膜7を形成することにより、ポリシラン膜5をポリシロキサン膜5Aへ、金属イオン含有膜7を金属微粒子含有膜7Aへ、それぞれ改質する工程(STEP2)を備え、MOS構造の積層膜100を形成する。

(もっと読む)

半導体装置

【課題】ゲートパッド電極と裏面金属電極間のリーク電流を抑制し、ボンディング強度を向上させ、高性能化・高信頼化を図る。

【解決手段】基板10の第1表面上に配置され、それぞれ複数のフィンガーを有するゲート電極24・ソース電極20およびドレイン電極22およびオーム性電極層18と、ゲート電極・ソース電極およびドレイン電極ごとに複数のフィンガーをそれぞれ束ねて形成したゲート端子電極GE1〜4・ソース端子電極SE1〜4およびドレイン端子電極DEと、オーム性電極層上に配置され、ゲート端子電極と接続するゲートパッド電極30と、オーム性電極層と基板との界面に形成された反応層を覆うように基板内に形成された第1導電型半導体層16と、第1導電型半導体層16を覆うように、基板内に形成され、第1導電型と反対導電型の第2導電型半導体層とを備える半導体装置1。

(もっと読む)

半導体発光素子及びその製造方法

【課題】高輝度化を図ることができる半導体発光素子及びその製造方法を提供する。

【解決手段】実施形態に係る半導体発光素子は、第1導電形の第1半導体層と、第2導電形の第2半導体層と、前記第1半導体層と前記第2半導体層との間に設けられた発光層と、を有する構造体と、前記構造体の前記第2半導体層の側に設けられ、金属部と、前記金属部を貫通する複数の開口部と、を有する第1電極層と、前記第2半導体層と、前記第1電極層と、の間に設けられた中間層と、前記第1半導体層と導通する第2電極層と、を備える。前記複数の開口部のそれぞれの円相当直径は、10ナノメートル(nm)以上、5マイクロメートル(μm)以下である。前記中間層の厚さは、10nm以上、200nm以下である。

(もっと読む)

感光性ペースト組成物、金属配線の製造方法およびディスプレイ用部材の製造方法

【課題】微細パターン形成が可能であり、かつ、貴金属材料の使用量が少なくでき、低コスト化が可能な電極を形成できる感光性ペースト組成物を提供する。

【解決手段】樹脂粒子表面を金属で被覆した金属被覆樹脂粒子、反応性モノマー、カルボキシル基を含有するポリマーおよび光重合開始剤を含有する感光性ペースト組成物とする。

(もっと読む)

有機薄膜トランジスタ及びこれを備えた平板表示装置

【課題】有機薄膜トランジスタ及びこれを備えた平板表示装置を提供する。

【解決手段】基板の一面上に形成されるソース/ドレイン電極及び有機半導体層と、ソース/ドレイン電極及び有機半導体層と絶縁されるゲート電極と、ソース/ドレイン電極と前記ゲート電極との間に一層以上のゲート絶縁層と、を備え、ソース/ドレイン電極と前記ゲート電極との交差領域のうち少なくとも一部でのゲート絶縁層の厚さは、有機半導体層のチャンネル領域とゲート電極との交差領域のうち少なくとも一部でのゲート絶縁層の厚さ以上とした。

(もっと読む)

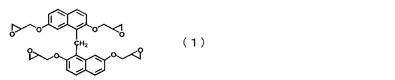

電子デバイス及びその製造方法、並びに、半導体装置及びその製造方法

【課題】従来よりも低い温度での形成が可能である絶縁層を備えた電子デバイスを提供する。

【解決手段】電子デバイスは、(A)制御電極12、(B)第1電極14及び第2電極14、並びに、(C)第1電極14と第2電極14との間であって、絶縁層13を介して制御電極12と対向して設けられた、有機半導体材料層15から成る能動層16を備えて成り、少なくとも能動層12と接触する絶縁層13の部分は、下記の式(1)にて示される材料を硬化して成る層から構成されている。 (もっと読む)

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、および電子機器

【課題】基板やゲート絶縁膜の露出表面と、ソース電極およびドレイン電極の露出表面とに、良好で均一な膜質の半導体薄膜を設けることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ1aは、有機材料または酸化物材料またはシリコン系材料からなるゲート絶縁膜(絶縁層)15上に、導電性酸化物材料からなる酸化物材料層17-aとこの上部の金属材料層17-bとからなるソース電極およびドレイン電極が設けられたものである。そしてゲート絶縁膜(絶縁層)15とソース電極17sおよびドレイン電極17dとにおける酸化物材料層17-aとの露出面が、自己組織化膜19で覆われており、この自己組織化膜19で覆われた上部のソース電極17s−ドレイン電極17d間にわたって半導体薄膜21が設けられている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置、ショットキーバリアダイオードの特性を向上させる。

【解決手段】禁制帯幅の異なる第1膜と第2膜とが積層されたヘテロ接合部を少なくとも一つ有する積層体Hと、積層体Hと同層の積層物よりなるダミー積層体Dと、積層体Hとダミー積層体Dとの間に設けられた溝Gと、溝内部を含み積層体Hの上部からダミー積層体Dの上部まで延在するように配置され、積層体Hの第1の側壁に接するように配置され、積層体Hとの間にショットキー接続される第1電極SEと、積層体Hの第1の側壁と対向する第2の側壁に接するように配置された第2電極OHEと、で半導体装置を構成する。このように、ダミー積層体Dを残存させ、積層体Hとの間に溝Gを設け、溝内部に充填された第1電極SEによって、側壁コンタクトを実現したので、積層体Hをエッチングする際の欠陥が溝底部に発生する確率を低減でき、逆リーク電流を低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】MPS構造又はJBS構造を有し、低い順方向降下電圧VF及び高い逆方向耐圧VRを両立させることが可能で、さらには、逆回復時間trrが短く、かつ、逆方向リーク電流IRが低い半導体装置を提供する。

【解決手段】n−型半導体層114と、n−型半導体層114の表面に選択的に形成されたp+型拡散領域120と、n−型半導体層114及びp+型拡散領域120の表面上に形成され、n−型半導体層114との間でショットキー接合を形成し、p+型拡散領域120との間でオーミック接合を形成するバリアメタル層130からなる電極層と、p+型拡散領域120の直下にのみライフタイムキラーが導入された局所ライフタイム制御領域160とを備える半導体装置100。

(もっと読む)

ヘテロ接合電界効果トランジスタ及びその製造方法

【課題】電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明に係るヘテロ接合電界効果トランジスタは、バリア層40及びバリア層40上に形成されたキャップ層50を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして前記窒化物半導体層上に設けられたゲート電極90と、前記窒化物半導体層上に形成されたSiを含まない絶縁膜からなる表面保護膜100とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】MPS構造又はJBS構造を有し、低い順方向降下電圧VF及び高い逆方向耐圧VRを両立させることが可能で、さらには、逆回復時間trrが短く、かつ、逆方向リーク電流IRが低い半導体装置を提供する。

【解決手段】n−型半導体層114と、n−型半導体層114の第1主面側表面に選択的に形成されたp+型拡散領域120と、n−型半導体層114の第1主面側表面上におけるp+型拡散領域120が形成されていない領域に形成され、n−型半導体層114との間でショットキー接合を形成するバリアメタル層130と、バリアメタル層130を覆うようにn−型半導体層114の第1主面側全面に形成され、p+型拡散領域120との間でオーミック接合を形成するオーミックメタル層140と、p+型拡散領域120の直下にのみライフタイムキラーが導入された局所ライフタイム制御領域150とを備える半導体装置100。

(もっと読む)

161 - 180 / 1,420

[ Back to top ]