Fターム[4M104BB06]の内容

Fターム[4M104BB06]に分類される特許

201 - 220 / 1,420

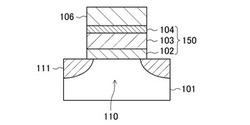

半導体装置及びその製造方法

【課題】工数を大幅に増加せず且つ高誘電体からなるゲート絶縁膜にダメージを与えることがない、仕事関数変更用金属不純物膜の効果を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたp型活性領域110と、p型活性領域110の上に形成されたゲート絶縁膜150と、ゲート絶縁膜150の上に形成されたゲート電極106とを有している。ゲート絶縁膜150は、二酸化シリコンよりも大きい誘電率を有する高誘電体膜103と、高誘電体膜103の上に形成され、炭素を含む炭素含有膜104とを有している。高誘電体膜103及び炭素含有膜104は、第1の金属としてランタン又はマグネシウムを含み、ゲート電極106は、第2の金属を含む。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】リフトオフ法を用いずに、簡易な手法で化合物半導体装置のゲート電極、ソース電極、及びドレイン電極を各種パターンに欠陥を生ぜしめることなく形成する。

【解決手段】AlGaN/GaN・HEMTを製造する際に、化合物半導体層上に保護絶縁膜8を形成し、保護絶縁膜8に開口を形成し、開口を埋め込む導電材料を保護絶縁膜8上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてゲート電極15(又はソース電極45及びドレイン46)を形成し、その後、保護絶縁膜8上に保護絶縁膜16を形成し、保護絶縁膜8,16に開口を形成し、開口を埋め込む導電材料を保護絶縁膜16上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてソース電極22及びドレイン23(又はゲート電極53)を形成する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて製造することが可能な電界効果トランジスタを提供する。

【解決手段】ソース領域144及びドレイン領域146並びにチャネル領域142を含む酸化物導電体層140と、チャネル領域142の導通状態を制御するゲート電極120と、ゲート電極120とチャネル領域142との間に形成され強誘電体材料からなるゲート絶縁層130とを備え、チャネル領域142の層厚は、ソース領域144の層厚及びドレイン領域146の層厚よりも薄い電界効果トランジスタ。酸化物導電体層140は、型押し成形技術を用いて形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において低抵抗なオーミック性を有し、酸・アルカリによる腐食に対し高い耐性を持つ電極を得ることを目的とする。

【解決手段】本発明に係る第1の半導体装置は、窒化物半導体層1と、窒化物半導体層上に設けられた電極とを備え、窒化物半導体層1は電極下に、それ以外の部分よりも高濃度にn型不純物を含む高濃度不純物領域2を備え、電極は、窒化物半導体層1上に設けられた第一金属層3と、第一金属層3上に設けられた第二金属層4と、第二金属層4上に設けられた第三金属層5と、を備え、第一金属層3は第二金属層4よりも窒化物半導体層1との高い密着性を有する金属を含み、第三金属層5は水素よりもイオン化傾向の小さい金属を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧向上や短チャンネル効果の抑制を可能とする半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、半導体基板であるSiC基板1上に形成された、バッファ層2と、バッファ層2上に形成された、バッファ層2よりもバンドギャップが小さいチャネル層3と、チャネル層3上に形成された、チャネル層3よりもバンドギャップが大きいバリア層4と、バリア層4上に互いに離間して形成された、ソース、ドレイン電極7、8と、ソース、ドレイン電極7、8下から、バリア層4を通ってチャネル層3中にそれぞれ達する、不純物領域5とを備え、不純物領域5の下端は、バッファ層2に達しない。

(もっと読む)

薄膜素子用基板の製造方法、薄膜素子の製造方法、薄膜トランジスタの製造方法、薄膜素子、および薄膜トランジスタ

【課題】本発明は、表面平滑性に優れ、薄膜素子の特性劣化を抑制することが可能な薄膜素子用基板が得られる新規な薄膜素子用基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、金属基材に薬液処理を施す金属基材表面処理工程と、上記金属基材上にポリイミド樹脂組成物を塗布して絶縁層を形成する絶縁層形成工程とを有し、上記絶縁層の表面粗さRaが30nm以下であることを特徴とする薄膜素子用基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

積層構造体及びその製造方法、並びに多層配線基板、アクティブマトリクス基板及び画像表示装置

【課題】インクジェット法を用いた場合でも高いスループットで微細な導電層を有する積層構造体を製造可能な積層構造体の製造方法、並びに積層構造体、多層配線基板、アクティブマトリクス基板及び画像表示装置を提供する。

【解決手段】基板上に、同一パターンの高表面エネルギー部40を一定の間隔で周期的に配列しておき、インクジェット装置の主走査方向(X軸方向)における吐出ノズル1,2の間隔を、高表面エネルギー部40のパターン間隔と一致させて選択的に機能液の液滴dを滴下してソース電極230、ソース電極線290、ドレイン電極240となる導電層を形成する。

(もっと読む)

半導体に直接電着する方法

【課題】 半導体の上に直接電着する方法を提供する。

【解決手段】 本開示は、半導体材料の少なくとも1つの表面上に金属又は金属合金を電着する方法を提供する。本発明の方法は、半導体材料の少なくとも1つの表面上の、電着された金属膜による完全な被覆を提供する。本開示の方法は、半導体材料を準備することを含む。半導体材料の少なくとも1つの表面上に、電着プロセスによって金属膜が付けられる。用いる電着プロセスには、最初に低電流密度を加え、所定の時間後に電流密度を高電流密度に変える電流波形が用いられる。

(もっと読む)

充填用基材及びそれを用いた充填方法

【課題】充填時の溶融温度が低く、凝固後は高い融点を確保することができ、しかも、作業操作性に優れた充填用基材及びそれを用いた充填方法を提供すること。

【解決手段】充填用基材5は、第1金属層21と第2金属層22とを含む金属層2を支持基体1の一面上に設けた構造になっている。第1金属層21は、その融点よりも低い温度で溶融可能なナノ金属粒子の集合したものでなり、第2金属層22は、その融点が第1金属層21の融点よりも低い金属粒子の集合したものでなる。充填用基材5の一面側を、微細空間30の開口する基板3の一面上に重ねる。そして、充填用基材5を加熱し、かつ、加圧F1して、金属層2の溶融物を微細空間30内に充填する。

(もっと読む)

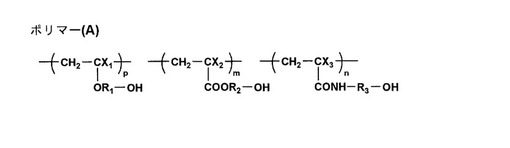

有機電子デバイス用電極

【課題】透明性、導電性且つ生産後のロール状態での保存性が良好な有機電子デバイス用電極の提供。

【解決手段】透明基材上に、導電性の金属細線パターンと、導電性ポリマー層を設けた有機電子デバイス用電極において、該金属細線パターンの金属細線の厚みをaとし、開口部における該導電性ポリマー層の厚みをbとしたとき、以下式1〜式3で表される条件を満たし、且つ、導電性ポリマー層がπ共役系導電性高分子とポリアニオンとを含んでなる導電性ポリマーおよび下記ポリマー(A)を有する有機電子デバイス用電極。0.2≦a≦2.0(式1)0.2≦b≦2.0(式2)−0.2≦b−a≦1.8(式3) (もっと読む)

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

薄膜トランジスタ、その製造方法、及びこれを含む表示装置

【課題】不完全結晶成長領域を含まない多結晶シリコンでゲート電極または遮光部材のような金属パターン上に位置する半導体層を形成することにより、駆動特性及び信頼性を向上させる薄膜トランジスタ、その製造方法、及びこれを含む表示装置を提供する。

【解決手段】多結晶シリコンで形成された半導体層142を含む薄膜トランジスタにおいて、前記半導体層と基板110との間に前記半導体層と絶縁するように位置する金属パターンをさらに含み、前記半導体層の多結晶シリコンは、結晶成長方向と平行な結晶粒界を含み、表面における波状線の最大ピークと最小ピークとの間の距離として定義される表面粗度が15nm以下である。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】ヘテロ接合バイポーラトランジスタのエミッタメサがより正確に形成できるようにする。

【解決手段】第1エミッタ電極107bの側部には、例えば酸化シリコンからなる庇部108が形成され、また、少なくともキャップ層106を含んで構成されたエミッタメサの露出している側面から庇部108の下部の領域のレッジ構造部105aにかけて形成された、例えば窒化シリコンからなる被覆層109が形成されている。被覆層109が、庇部108の側面,庇部108の下面,エミッタメサの側部,およびレッジ構造部105aの上にかけて形成されている。

(もっと読む)

半導体素子用エピタキシャル基板の製造方法、半導体素子用エピタキシャル基板、および半導体素子

【課題】簡便な手法によってエピタキシャル基板の障壁層表面の平坦性を向上させ、ショットキーコンタクト特性の優れたエピタキシャル基板を実現する方法を提供する。

【解決手段】半導体素子用のエピタキシャル基板を製造する方法が、下地基板の上に、少なくともGaを含む、Inx1Aly1Gaz1N(x1+y1+z1=1)なる組成の第1のIII族窒化物からなるチャネル層をエピタキシャル形成するチャネル層形成工程と、チャネル層の上に、少なくともInとAlを含む、Inx2Aly2Gaz2N(x2+y2+z2=1)なる組成の第2のIII族窒化物からなる障壁層をエピタキシャル形成する障壁層形成工程と、障壁層形成工程における加熱温度よりも100℃以上250℃以下高い加熱温度で障壁層が形成された下地基板を加熱することにより、障壁層の表面平坦性を向上させる平坦化処理工程と、を備える。

(もっと読む)

パターン形成体の製造方法、機能性素子の製造方法および半導体素子の製造方法

【課題】本発明は、高精細なパターニングが可能なパターン形成体の効率的な製造方法を提供することを主目的とする。

【解決手段】本発明は、基板上に形成され、表面が疎水性を示す疎水性層上にフォトレジストパターンを形成するフォトレジストパターン形成工程と、上記フォトレジストパターンが形成された上記疎水性層の表面にエネルギーを照射して親水化し、親水性領域を形成する親水化工程と、上記フォトレジストパターンを剥離し、上記疎水性層表面に、上記親水性領域と上記親水化工程にて上記フォトレジストパターンで覆われていた疎水性領域とがパターン状に形成された親疎水パターンを形成するフォトレジストパターン剥離工程とを有することを特徴とするパターン形成体の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体基板上の金属電極と半導体基板の界面に、現像残渣のない半導体装置を提供すること。

【解決手段】半導体基板上に、金属電極が設けられた半導体装置であって、金属電極は、半導体基板の上面視において、細線部と、細線部の電極の長手方向の両端に太線部と、細線部から太線部へ向けて線幅が漸増する線幅漸増部とからなり、細線部の側面と線幅漸増部の側面の境界領域に、曲率を有す円弧が付けられた形状であることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】コンタクト抵抗が小さいオーミック電極を備えたIII−V族窒化物半導体を用いた半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板11の上に順次形成された、第1のIII−V族窒化物半導体層12及び第1のIII−V族窒化物半導体12と比べてバンドギャップが大きい第2のIII−V族窒化物半導体層13と、p型の導電型を有する第3のIII−V族窒化物半導体層21と、第1のオーミック電極14とを備えている。第1のオーミック電極14は、下部が第2のIII−V族窒化物半導体層13及び第3のIII−V族窒化物半導体層21を貫通し且つ第1のIII−V族窒化物半導体層12における2次元電子ガス層よりも下側の領域に達するように形成されている。

(もっと読む)

III族窒化物半導体素子、III族窒化物半導体素子の製造方法、および電子装置

【課題】 アクセス抵抗およびオン抵抗が低いIII族窒化物半導体素子、III族窒化物半導体素子の製造方法、および電子装置を提供する。

【解決手段】

障壁層902は、チャネル層901上方にヘテロ接合され、

チャネル層901の上部の一部およびその上方の障壁層902が除去されて凹部が形成され、

チャネル層901および障壁層902の一部にn型導電層領域904が形成され、

n型導電層領域904は、前記凹部の表面を含み、

n型導電層領域904の深さTimpが、n型導電層領域904表面の各部から前記表面と垂直方向の測定値で15nm以上であり、

オーミック電極906および907は、前記凹部の表面を介して前記n型導電層領域にオーミック接触していることを特徴とする、III族窒化物半導体素子。

(もっと読む)

炭素ベース材料上の向上した結合界面を有する半導体構造体、その形成方法、及び、電子デバイス

【課題】 高密度で、構造部寸法がより小さく、より正確な形状の半導体構造体及び電子デバイスを提供する。

【解決手段】 炭素ベース材料の上面上に配置された少なくとも一層の界面誘電体材料を含む、半導体構造体及び電子デバイスが提供される。少なくとも一層の界面誘電体材料は、炭素ベース材料のものと同じである、典型的には六方晶短距離結晶結合構造を有し、従って、少なくとも一層の界面誘電体材料が、炭素ベース材料の電子構造を変えることはない。炭素ベース材料のものと同じ短距離結晶結合構造を有する少なくとも一層の界面誘電体材料の存在により、炭素ベース材料と、誘電体材料、導電性材料、又は誘電体材料及び導電性材料の組み合わせを含む、上にある任意の材料層との間の界面結合が改善される。その結果、改善された界面結合が、炭素ベース材料を含むデバイスの形成を容易にする。

(もっと読む)

高電圧スイッチング回路

【課題】高電圧処理能力および改善された実行能力を有する効率的なスイッチング回路を提供する。

【解決手段】第1および第2のIII−V族トランジスタを有し、第2のIII−V族トランジスタは、第1のIII−V族トランジスタよりも大きな降伏電圧を有する。さらに、第1のIII−V族トランジスタと並列に配置されるシリコンダイオードを有し、この並列配置は、第2のIII−V族トランジスタと直列に接続、効率的な3端子デバイスであり、第1端子は第2のIII−V族トランジスタのゲート、第1のIII−V族トランジスタのソースおよびシリコンダイオードのアノードに結合する。第2端子は第1のIII−V族トランジスタのゲートと結合し、第3端子は第2III−V族トランジスタのドレインと結合する。

(もっと読む)

201 - 220 / 1,420

[ Back to top ]