Fターム[4M104BB06]の内容

Fターム[4M104BB06]に分類される特許

1,401 - 1,420 / 1,420

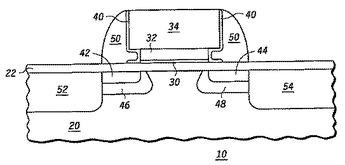

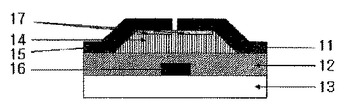

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

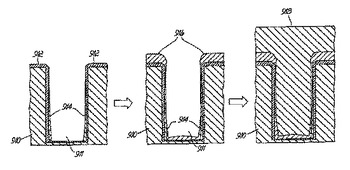

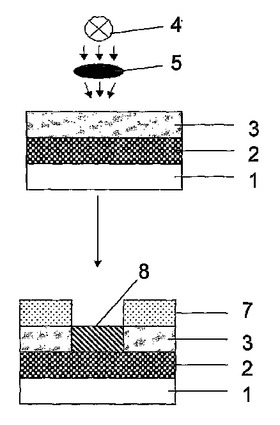

少なくとも1つの層の構造化方法並びに層から成る構造を備えた電気素子

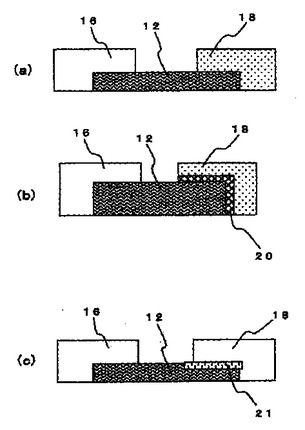

本発明は、少なくとも1つの構造化された層(10A)を作成するための方法を提供し、その際第1の構造(20A)および第2の構造(20B)を有するマスク構造(20)が基板(5)上に存在している層(10)に生成される。このマスク構造(20)を通して第1の構造(20A)は等方性構造化法を用いてかつ第2の構造(20B)は異方性構造化法を用いて層(10)に移される。本発明の方法により、少なくとも1つの層に唯一のマスク構造を用いて2つの構造(20A,20B)を生成することが可能になる。  (もっと読む)

(もっと読む)

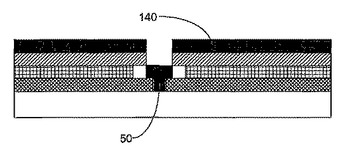

イオン化物理蒸着方法

iPVDシステム(200)は、真空チャンバー(30)内で突出部(14)を最小化または除去しながら、フィールド(10)と底部(15)被覆と比較して側壁(16)被覆性を向上させる処理を用いて、障壁層材料(912)のような均一な材料を半導体基板(21)上の高いアスペクト比のナノサイズの開口部(11)に蒸着するために調整される。そのiPVDシステム(200)は、そのターゲットから材料をスパッタするために、低いターゲットパワーと50mTより高い圧力で動作される。RFエネルギーは、高密度プラズマを生成するそのチャンバーに連結される。小さなRFバイアス(数ボルト未満)は、特に、底部における被覆性を高めることを助けるために印加されることができる。  (もっと読む)

(もっと読む)

窒化物半導体装置のオーム性電極構造

窒化物半導体を有する窒化物半導体装置のオーム性電極構造であって、窒化物半導体上に形成された第1の金属膜と、第1の金属膜上に形成された第2の金属膜とを有する。第1の金属膜は、V、Mo、Ti、Nb、W、Fe、Hf、Re、Ta、Zrから成るグループの中から選ばれた少なくとも一つの材料で構成されている。第2の金属膜は、第1の金属膜102と異なる、V、Mo、Ti、Nb、W、Fe、Hf、Re、Ta、Zr、Pt、Auから成るグループの中から選ばれた少なくとも一つの材料で構成されている。 (もっと読む)

デバイス製造方法および基板

電磁放射線を用いた一回の露光プロセスでT−ゲートを製造する方法が開示される。  (もっと読む)

(もっと読む)

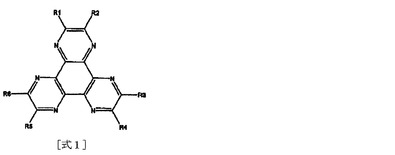

有機薄膜トランジスタ

本発明は、有機物層を有する有機トランジスタが提供される。本発明の前記有機物層は、下記式1で表される化合物のうち少なくともいずれか1種を含む。

(もっと読む)

(もっと読む)

金属被着

レーザによりパターン化された基板上に金属を無電解メッキする方法。基板上に熱画像形成層および触媒層がともに被着される。レーザ・ビームで露光すると、熱画像形成層において十分なレベルの放射が熱に変換され、それによって、隣接する触媒層の露光領域が不活性になる。次いで、レーザによりパターン化された基板を反応溶液に暴露し、それによって、触媒層の非露光領域上で金属被膜の成長が開始される。  (もっと読む)

(もっと読む)

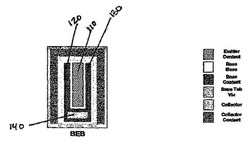

バイポーラ接合トランジスタジオメトリ

【課題】

【解決手段】 バイポーラ接合トランジスタ(100)に関連する方法、装置、デバイスの実施例が記載されている。

(もっと読む)

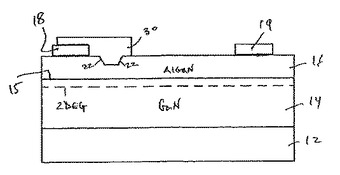

III族窒化物電流制御デバイスおよび製造方法

III族窒化物デバイスが、名目上オフ、すなわち、エンハンスメントモードのデバイスを作製するための凹部電極を含む。凹部電極を設けることによって、デバイス中の電流の流れを阻止するために、電極が非能動であるときに2つのIII族窒化物材料の境界面に形成された導電チャネルが中断される。電極はショットキー接点または絶縁金属接点であり得る。名目上オフの特性を有する整流器デバイスを形成するために、2つのオーム接点を設けることができる。電極が形成された凹部は傾斜側面を有することができる。電極は、デバイスの電流運搬電極と組み合わせて幾つもの幾何学配置で形成可能である。電極が凹部でないとき、名目上オンのデバイス、すなわち、ピンチ抵抗が形成される。ダイオードは、絶縁体を貫通してAlGaN層に達する非凹部のオーム接点およびショットキー接点を設けることによっても形成される。  (もっと読む)

(もっと読む)

整流素子およびそれを用いた電子回路、並びに整流素子の製造方法

一対の電極と、該一対の電極間に設けられた、1本または複数のカーボンナノチューブにより構成されるキャリア輸送体と、を備え、前記一対の電極のうち、一方の電極および前記キャリア輸送体の第1の界面と、他方の電極および前記キャリア輸送体の第2の界面と、が異なる障壁レベルとなるように、これら2つの接続構成を異なる構成とすることで、高周波応答性、耐熱性に優れたキャリア輸送体を備えた整流素子を提供し、併せて、それを用いた電子回路、並びに整流素子の製造方法を提供する。  (もっと読む)

(もっと読む)

半導体構造、二重仕事関数のCMOSデバイス、二重仕事関数のCMOS回路、および基板上に二重仕事関数のCMOSデバイスを形成する方法(炭化金属ゲート構造および形成方法)

【課題】 炭化金属を含むゲート電極を含む少なくとも1つのFETを含む相補型金属酸化膜半導体(CMOS)などの半導体デバイスおよび形成方法を提供することにある。

【解決手段】 このCMOSは、ある金属とある金属の炭化物によって二重仕事関数が与えられる、二重仕事関数の金属ゲート電極を含む。

(もっと読む)

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

窒化ガリウム材料デバイスおよびその形成方法を提供する。該デバイスは、電極規定層を包含する。電極規定層は典型的にはその内部に形成されたビアを有し、該ビア内に電極が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。 (もっと読む)

電極、その製造方法およびそれを用いた半導体素子

低接触抵抗を実現しつつ表面荒れの少ない電極が得られる技術を提供する。

半導体膜101の上部に設けられる電極であって、この半導体膜101の上部にこの半導体膜の側から順に積層された第一金属層102と第二金属層103とを有し、この第一金属膜102が、Alからなり、この第二金属膜103が、Nb、W、Fe、Hf、Re、TaおよびZrからなる群より選ばれる1種以上の金属からなることを特徴とする電極。

(もっと読む)

モノリシック集積型エンハンスメントモードおよびデプリーションモードFETおよびその製造方法

【課題】 製造コストを低減し品質の均一性および安定性を高めたモノリシック集積型エンハンスメントモード/デプリーションモードFETデバイスを提供する。

【解決手段】 単一の半導体多層構造でデプリーションモード(Dモード)FETをエンハンスメントモード(Eモード)FETとモノリシックに集積回路化する。上記多層構造にはチャネル層を設け、その上に障壁層をオーバーレイし、さらにその上にオームコンタクト層をオーバーレイする。これらDモードFETおよびEモードFETのソースコンタクトおよびドレーンコンタクトをオームコンタクト層に接続する。またDモードFETおよびEモードFETのゲートコンタクトを障壁層に接続する。障壁層の中のEモードゲートコンタクトの下に非晶質化領域を設ける。この非晶質化領域が障壁層との間の埋込みEモードSchottkyコンタクトを構成する。代わりに実施例ではDモードFETのゲートコンタクトを障壁層にオーバーレイした第1の層に接続し、その第1の層の中にDモード非晶質化領域を形成する。

(もっと読む)

high−kゲート誘電体と関連の構造を有するCMOSゲートを形成するための、異なる仕事関数を有する金属を統合する方法

1つの一般的な実施形態では、デュアルメタルのNMOSゲート(226)とPMOSゲート(228)を形成するために、基板(202)上に第1金属層(206)と第2金属層(208)を統合するための方法として、基板(202)のNMOS領域(210)とPMOS領域(212)上に誘電体層(204)を堆積する。更に、本方法は、誘電体層(204)上に第1金属層を堆積する。更に、方法は、第1金属層(206)上に第2金属層(208)を堆積する(150)。更に、本方法は、基板(202)のNMOS領域(210)に窒素を注入し(152)、第1金属層(206)の第1部分を金属酸化物層(220)に変え(154)、第1金属層(206)の第2部分を金属窒化物層(218)に変える。更に、本方法は、NMOSゲート(226)とPMOSゲート(228)を形成し(156)する。NMOSゲート(226)は金属窒化物層(218)のセグメント(234)を含み、PMOSゲート(228)は金属酸化物層(220)のセグメント(242)を含む。  (もっと読む)

(もっと読む)

無電解堆積のエンドポイントを検出するための装置および方法

基板の表面に向けて電磁放射を方向付けて、該基板の該表面上の部材から反射された該電磁放射の強度の変化を1つ以上の波長で検出することによって無電解堆積プロセスをコントロールするための装置および方法。一実施形態において、該基板が検出機構に対して移動されると、無電解堆積プロセスステップの検出された終了が測定される。別の実施形態において、多数の検出ポイントが、該基板の該表面にわたる該堆積プロセスの状態を監視するために使用される。一実施形態において、該検出機構は該基板上で無電解堆積流体に浸される。一実施形態において、コントローラは、記憶されたプロセス値、異なる時間に収集されたデータの比較、および種々の算出された時間依存データを使用して無電解堆積プロセスを監視、記憶および/またはコントロールするために使用される。 (もっと読む)

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

半導体基板上の、超臨界流体による物質の蒸着

集積回路デバイス製造のための半導体基板のような基板上への、超臨界流体を利用した物質の蒸着。蒸着は、基板表面に蒸着される物質の前駆体を含む、超臨界流体をベースとする組成物を使用して行われる。そのようなアプローチにより、気相蒸着工程に必要な揮発性および搬送性がないために、蒸着への適用には全く不適切であった前駆体の使用が可能になる。 (もっと読む)

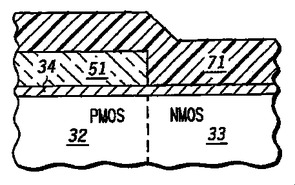

デュアルメタルゲートデバイスの形成方法

異種金属により形成されるデュアルメタルゲートを備えるMOSトランジスタ(10)を形成する方法を提供する。HfO2のようなゲート誘電体(34)を半導体基板(31)の上に堆積させる。次に、犠牲層(35)をゲート誘電体(34)を覆うように堆積させる。犠牲層(35)をパターニングして、基板(31)の第1領域(32)(例えばpMOS)の上のゲート誘電体(34)が露出し、かつ基板(31)の第2領域(33)(例えばnMOS)の上のゲート誘電体(34)が犠牲層(35)によって保護されたままになるようにする。第1ゲート導体材料(51)を残りの犠牲領域(35)の上に、かつ露出したゲート誘電体(34)の上に堆積させる。基板(31)の第2領域(33)の上の第1ゲート導体材料(51)がエッチングにより全て除去されるように第1ゲート導体材料(51)をパターニングする。第1ゲート導体材料(51)を取り除く際に、第2領域(33)上の犠牲層(35)は、下層の誘電体材料(34)にダメージが加わるのを防止するように機能することができる。  (もっと読む)

(もっと読む)

化合物半導体装置及びその製造方法

【課題】 電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置を実現する。

【解決手段】 本発明の化合物半導体装置は、GaAs等の第1の化合物半導体層上に、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にない、即ちタイプII構造のバンド構造を有する属元素と6属元素の化合物からなるアモルファス層、例えばアモルファスGaS層(a−GaS層)を有するものである。

(もっと読む)

1,401 - 1,420 / 1,420

[ Back to top ]