Fターム[4M104BB10]の内容

Fターム[4M104BB10]の下位に属するFターム

Au−Ge/Ni (56)

Fターム[4M104BB10]に分類される特許

1 - 20 / 48

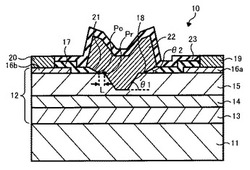

半導体装置および半導体装置の製造方法

【課題】性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、半導体層12、絶縁膜17、ゲート電極22、ドレイン電極19およびソース電極20、を具備する。半導体層12は、半絶縁性半導体基板11上に形成され、表面に、側壁が傾いたテーパ状のリセス領域18を有する。半導体層12は、活性層14を含む。絶縁膜17は、半導体層12上に形成されたものであり、リセス領域18を全て露出する貫通孔21を有する。貫通孔21は、側壁がリセス領域18の側壁の傾き角θ1より小さい角度θ2で傾いたテーパ状である。ゲート電極22は、リセス領域18および貫通孔21を埋めるように形成されたものである。ドレイン電極19およびソース電極20は、半導体層12上のうち、リセス領域18を挟む位置に形成されたものである。

(もっと読む)

半導体デバイス及びその製造方法

【課題】グラフェンの特性を生かしつつ、高耐圧デバイスや紫外発光・受光デバイスを実現する。

【解決手段】半導体デバイスを、2次元構造のグラフェン電極2、3と、グラフェン電極のグラフェン端に結合した2次元構造のボロンナイトライド半導体層5とを備えるものとする。

(もっと読む)

電界効果トランジスタ、半導体スイッチ回路、および通信機器

【課題】半導体スイッチのチップサイズを大きくすることなく、高調波特性を改善する。

【解決手段】FET1において、化合物半導体基板上に形成され、所定の間隔を隔てて互いに平行状に設けられる複数のソース電極6を有するソース配線3と、化合物半導体基板上に形成され、所定の間隔を隔てて互いに平行状に設けられて複数のソース電極6に対して並列方向に交互に配置される複数のドレイン電極7を有するドレイン配線4と、化合物半導体基板上に形成され、少なくとも前記並列方向に互いに隣り合うソース電極6とドレイン電極7との電極間に位置する部分を有するゲート配線5と、ゲート配線5が形成される領域にてゲート配線5下に形成され、複数のソース電極6と複数のドレイン電極7との各電極間に独立して設けられる複数の埋め込みゲート層8とを備えた。

(もっと読む)

発光素子

【課題】高輝度の発光素子を提供する。

【解決手段】本発明に係る発光素子1は、支持基板20と、支持基板20の側から第1導電型の第1導電型層と、光を発する活性層15と、第1導電型とは異なる第2導電型の第2導電型層とを有する発光部10と、支持基板20と発光部10との間に設けられ、光を発光部10の側に反射する反射部40と、反射部40と発光部10との間に設けられ、光を透過し、電気絶縁性を有する絶縁層50と、絶縁層50と発光部10との間の一部に設けられる界面電極60と、第2導電型層の活性層15の反対側の表面に設けられ、界面電極60の直上とは異なる領域に設けられる第1電極72と、第1電極72が設けられる側に第1電極72とは別に設けられ、第1電極72が接触している第2導電型層とは異なる発光部10の部分、又は界面電極60に電気的に接続する第2電極70とを備える。

(もっと読む)

半導体発光素子及びその製造方法

【課題】高輝度化の半導体発光素子及びその製造方法を提供する。

【解決手段】半導体発光素子は、第1導電形の第1半導体層と、第2導電形の第2半導体層と、前記第1半導体層と前記第2半導体層との間に設けられた発光層と、第1電極層と、第2電極層と、を備える。第1電極層は、第2半導体層の第1半導体層とは反対側に設けられ、第2半導体層と接する金属部と、第1半導体層から第2半導体層に向かう方向に沿って金属部を貫通し前記方向に沿って見たときの形状の円相当直径が10ナノメートル以上5マイクロメートル以下である複数の開口部と、を有する。第2電極層は、第1半導体層と導通する。第2半導体層は、金属部に接する凸部と、開口部の底部において凸部よりも前記方向に沿って後退した凹部と、を有する。

(もっと読む)

半導体装置

【課題】ゲートパッド電極と裏面金属電極間のリーク電流を抑制し、ボンディング強度を向上させ、高性能化・高信頼化を図る。

【解決手段】基板10の第1表面上に配置され、それぞれ複数のフィンガーを有するゲート電極24・ソース電極20およびドレイン電極22およびオーム性電極層18と、ゲート電極・ソース電極およびドレイン電極ごとに複数のフィンガーをそれぞれ束ねて形成したゲート端子電極GE1〜4・ソース端子電極SE1〜4およびドレイン端子電極DEと、オーム性電極層上に配置され、ゲート端子電極と接続するゲートパッド電極30と、オーム性電極層と基板との界面に形成された反応層を覆うように基板内に形成された第1導電型半導体層16と、第1導電型半導体層16を覆うように、基板内に形成され、第1導電型と反対導電型の第2導電型半導体層とを備える半導体装置1。

(もっと読む)

半導体トランジスタおよびその製造方法

【課題】FETの閾値電圧のばらつきのない半導体トランジスタおよびその製造方法を提供する。

【解決手段】半導体トランジスタ100は、基板1と、基板1の上方に形成された第1化合物半導体層103と、第1化合物半導体層103上に形成され、第1化合物半導体層103よりもバンドギャップの大きい第2化合物半導体層104と、第2化合物半導体層104内の少なくとも一部に、酸素がドープされた酸素ドープ領域105と、第2化合物半導体層104上に形成された第3化合物半導体層106と、第1化合物半導体層103に電気的に接続されたソース電極107およびドレイン電極109と、酸素ドープ領域105の上方に、酸素ドープ領域105に接するように形成されたゲート電極108とを有する。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗の低減を図ることができる電界効果トランジスタ(FET)を提供する。

【解決手段】FET101は、化合物半導体基板1と、化合物半導体基板1上に形成され、当該基板側から見て、n型キャリアが蓄積するチャネル層5、ショットキー層8、及びキャップ層9を順次含む半導体積層構造10と、ゲート電極20、ソース電極21、及びドレイン電極22とを備えている。キャップ層9は、ショットキー層8側から見て、自然超格子構造を有するアンドープの又はn型キャリアが添加された第1のInGaP層9Aと、自然超格子構造を有しないn型キャリアが添加された第2のInGaP層9Bとを順次含んでいる。

(もっと読む)

パターン形成方法および積層構造体

【課題】所望のパターンが形成でき、製造工程の迅速化を図ることが可能なパターン形成方法を提供する。

【解決手段】本実施形態のパターン形成方法は、下地10の上に第1の膜11を選択的に形成する工程と、前記第1の膜11および前記第1の膜に覆われていない前記下地10の上に、第2の膜13を形成する工程と、前記第2の膜13の平均結晶粒径を前記第2の膜13の膜厚以上に調整する工程と、前記第1の膜11のエッチャントを前記第2の膜13の表面に晒し、前記第1の膜11の上に形成された前記第2の膜13を前記下地上から選択的に除去する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の表皮効果の抑制と低抵抗化を図る。

【解決手段】第1配線部41と、その第1配線部41の周りを被覆する、高融点金属窒化物を含む第2配線部42とを含む配線40aを形成する。このような配線40aにおける第2配線部42は、第1配線部41側から外周に向かって窒素含有率が高くなる部分を有するように形成する。これにより、配線40aにおける表皮効果が抑制されると共に、配線40aの低抵抗化が図られるようになる。

(もっと読む)

半導体装置

【課題】半絶縁性基板に形成されたゲートパッドにマイナスの電圧が印加され、半絶縁性基板の裏面に形成された裏面電極にプラスの電圧が印加されても、リーク電流を抑制できる半導体装置を提供する。

【解決手段】裏面電極10が形成された半絶縁性基板11の表面上に並列に形成された、複数のゲート電極15がゲート電極接続部21に接続されるとともに、このゲート電極接続部21が複数に分割された半導体装置であって、ゲート電極接続部21間の半絶縁性基板11の表面に形成されたn型の抵抗層22と、このn型の抵抗層22の周囲を覆うように、p型不純物層23と、このp型不純物層23の周囲を覆うように、所望の濃度で形成されたn型不純物層24と、を具備し、ゲートパッド29は、ゲート電極接続部21と、このゲート電極接続部21に隣接するn型の抵抗層22上の引き出し電極25とを接続するように形成される。

(もっと読む)

半導体発光素子およびその製造方法

【課題】 光取出し側の電極部である上側電極部と、この電極部と対になる電極部である中間電極部とを適切な位置関係で配設することにより、大電流印加時の発光効率を維持させた半導体発光素子およびその製造方法を提供する。

【解決手段】 支持基板の上面側に、中間電極部を含む中間層、第2導電型半導体層、活性層、第1導電型半導体層および上側電極部を順次具え、支持基板の下面側に下側電極層を具える半導体発光素子であって、前記中間電極部を互いの中間電極部間の間隔が50μm以上100μm以下の均等に分散した島状または等間隔の縞状、格子状かつ上面から見た中間電極部の第2導電型半導体層に対する面積率が3〜9%となるように配置することにより、大電流での使用時でも発光効率の高い半導体発光素子を提供することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極からチャネル層までの距離のばらつきが低減されたHEMT半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、リセスエッチング工程後に酸化膜形成工程を行う。リセスエッチングを行った後に、HEMT構造基板の加熱や過酸化水素への浸漬によって、強制的に酸化膜6’’及び7’’を形成する。このような酸化膜6’’及び7’’は、面内均一性に優れ、かつ、ある厚さで安定するため、大気中に暴露してもそれ以上酸化は進まない。酸化膜6’’及び7’’は、例えば、濃度3%の過酸化水素水にHEMT構造基板を3分間浸漬させることや、120℃のホットプレート上で2分間HEMT構造基板を加熱させることにより形成することができる。

(もっと読む)

発光素子

【課題】高輝度の発光素子を提供する。

【解決手段】本発明に係る発光素子1は、第1導電型の第1半導体層と、第1導電型とは異なる第2導電型の第2半導体層と、第1半導体層と第2半導体層とに挟まれる活性層105とを有する半導体積層構造10と、半導体積層構造10の一方の面側に設けられる第1電極と、半導体積層構造10の他方の面側に設けられ、活性層105が発する光を反射する反射層132と、半導体積層構造10と反射層132との間の一部分に設けられ、半導体積層構造10にオーミック接触するコンタクト部120と、反射層132の半導体積層構造10側の面の一部の上に設けられ、コンタクト部120へ電流を供給する第2電極とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 二次元電子ガスを発生させるワイドギャップ半導体層をその下の半導体層の構成元素の化合物半導体により形成することにより、非常に立上り電圧が低く、かつ、逆方向耐圧が高いダイオードまたはHEMT構造のMIS型トランジスタを有する半導体装置およびその製造方法を提供する。

【解決手段】 GaAs基板1上に、GaAs基板1よりもバンドギャップおよびキャリア濃度が共に大きく、GaAs基板1の表面に二次元電子ガスを生じさせることが可能で、かつ、その二次元電子ガスの電子をトンネル可能な厚さに形成されるN型のGaN層2が設けられ、そのGaN層2と電気的に接続して第1電極3が、GaAs基板1に電気的に接続して第2電極4が設けられている。

(もっと読む)

基板構造及びその形成方法

【課題】薄膜特性及び接着性が改善が可能な基板構造形成方法及びこれを用いて形成された基板構造を提供する

【解決手段】基板構造を形成する方法は、基板10をエッチングして垂直面51を有するエッチング部50を形成する段階と、基板10の全面上にまたは基板10に部分的に拡散物質層60を形成する段階と、拡散物質層60を熱処理して、一部が上記エッチング部50の表面の下へと拡散したシード層60’を形成する段階、及びシード層60’上に金属層70を形成する段階とを含む。上記方法によれば、シード層60’によって基板10のエッチング部50の表面特性が改善されることもあるので、エッチング部50の垂直面51に接着性に優れ且つ均一な厚さの金属層70を形成することができる。

(もっと読む)

半導体発光素子及びその製造方法

【課題】発光素子の製造プロセスにおいて、あるいは又、発光素子の動作時、安定した挙動を示す第2電極を有する発光素子を提供する。

【解決手段】発光素子は、n型の導電型を有する第1化合物半導体層11、第1化合物半導体層11上に形成され化合物半導体から成る活性層12、活性層12の上に形成された、p型の導電型を有する第2化合物半導体層13、第1化合物半導体層11に電気的に接続された第1電極15、及び、第2化合物半導体層13上に形成された第2電極14を備えており、第2電極14は、チタン酸化物から成り、4×1021/cm3以上の電子濃度を有し、活性層で発光した光を反射する。

(もっと読む)

電極構造および半導体装置

【課題】Ga原子及びAs原子の電極表面への拡散を低減可能なn型GaAs系半導体の電極構造及びこの電極構造を備える半導体装置を提供する。

【解決手段】本発明に係る電極構造は、Au及びGeを含む化合物から成り、n型GaAs半導体基板10上に設けられたオーミック金属層11と、オーミック金属層11上に設けられた第1のPt層13と、第1のPt層13上に設けられたTi層14とを備える。Ti層14は、Ga原子及びAs原子の電極表面への拡散を防止する。第1のPt層は、Ti層14のTi原子が、Au電極層12及びオーミック金属層11へ拡散することを防止する。その結果、Ti層14の拡散防止機能が維持される。これらにより、電極表面へのGa原子及びAs原子の拡散を低減することが可能となる。

(もっと読む)

半導体装置とその製造方法

【課題】SGOI(110)基板上のp、n両領域で高移動度の半導体装置を実現する。

【解決手段】Si1-xGex(0.25≦x≦0.90)の(110)面を表面に有する半導体基板(1,2,3)と、(110)面上に形成されたn及びpチャネル型MISFETとを具備し、両MISFETは、[−110]方向が[001]方向より長い線状で、(311)若しくは(111)面のファセットを有する活性領域(5,6)を有し、活性領域の[−110]方向に、ソース領域・チャネル領域・ドレイン領域が形成され、nチャネル型MISFETのチャネル領域(5C)はSiで形成され、pチャネル型MISFETのチャネル領域(6C)はSi1-yGey(x<y≦1)で形成され、両MISFETのチャネル領域は、活性領域の[−110]方向に、一軸圧縮ひずみを有する。

(もっと読む)

寄生容量が減らされた半導体デバイス

【課題】高速ショットキーデバイス及びpn接合デバイスにおける寄生容量を低減すると共にボンディング強度を改善する。

【解決手段】基板303と、基板303の上に配置される半導体デバイス300、302、及び半導体デバイス300、302との電気的接触を行うボンディング用パッド307を有し、ベンゾシクロブテンの層304が半導体デバイスの周辺に設けられ、ボンディング用パッド307がベンゾシクロブテンの層304の頂面に設けられる。

(もっと読む)

1 - 20 / 48

[ Back to top ]