Fターム[4M104BB13]の内容

Fターム[4M104BB13]の下位に属するFターム

Fターム[4M104BB13]に分類される特許

241 - 260 / 1,522

化合物半導体装置の製造方法及び化合物半導体装置

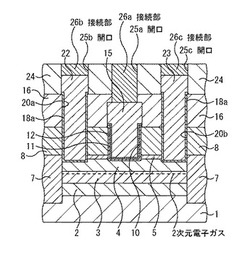

【課題】リフトオフ法を用いずに、簡易な手法で化合物半導体装置のゲート電極、ソース電極、及びドレイン電極を各種パターンに欠陥を生ぜしめることなく形成する。

【解決手段】AlGaN/GaN・HEMTを製造する際に、化合物半導体層上に保護絶縁膜8を形成し、保護絶縁膜8に開口を形成し、開口を埋め込む導電材料を保護絶縁膜8上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてゲート電極15(又はソース電極45及びドレイン46)を形成し、その後、保護絶縁膜8上に保護絶縁膜16を形成し、保護絶縁膜8,16に開口を形成し、開口を埋め込む導電材料を保護絶縁膜16上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてソース電極22及びドレイン23(又はゲート電極53)を形成する。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において低抵抗なオーミック性を有し、酸・アルカリによる腐食に対し高い耐性を持つ電極を得ることを目的とする。

【解決手段】本発明に係る第1の半導体装置は、窒化物半導体層1と、窒化物半導体層上に設けられた電極とを備え、窒化物半導体層1は電極下に、それ以外の部分よりも高濃度にn型不純物を含む高濃度不純物領域2を備え、電極は、窒化物半導体層1上に設けられた第一金属層3と、第一金属層3上に設けられた第二金属層4と、第二金属層4上に設けられた第三金属層5と、を備え、第一金属層3は第二金属層4よりも窒化物半導体層1との高い密着性を有する金属を含み、第三金属層5は水素よりもイオン化傾向の小さい金属を含む。

(もっと読む)

金属アミジナートを用いる原子層の析出

【課題】特定の金属先駆物質を用いたALD法により、基板表面に、均一で共形的な厚さと平滑な表面とを有する金属含有皮膜を形成する方法を提供する。

【解決手段】加熱基板を、一種以上の揮発性金属(I)、(II)あるいは(III)アミジナート化合物又はそのオリゴマーの蒸気に、次いで、還元性ガス、窒素含有ガス又は酸素含有ガスあるいはそれらの蒸気に交互に暴露して、当該基板表面に金属皮膜、金属窒化物皮膜又は金属酸化物皮膜を形成させることを含んでなる、金属を含む薄膜の形成方法。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧向上や短チャンネル効果の抑制を可能とする半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、半導体基板であるSiC基板1上に形成された、バッファ層2と、バッファ層2上に形成された、バッファ層2よりもバンドギャップが小さいチャネル層3と、チャネル層3上に形成された、チャネル層3よりもバンドギャップが大きいバリア層4と、バリア層4上に互いに離間して形成された、ソース、ドレイン電極7、8と、ソース、ドレイン電極7、8下から、バリア層4を通ってチャネル層3中にそれぞれ達する、不純物領域5とを備え、不純物領域5の下端は、バッファ層2に達しない。

(もっと読む)

トランジスタ

【課題】ソース電極(ドレイン電極)と、ゲート電極との重畳部に生じる寄生容量値を低減させても、オン電流値をほぼ維持できる新たな電極構造のトランジスタを提供することを課題の一とする。

【解決手段】トランジスタのソース電極及びドレイン電極の電極形状を櫛歯形状にすることによって寄生容量値を低減させる。また、櫛歯状電極の先端部の幅や、電極歯部間の間隔を制御することによって、電極歯部の側面から流れる曲線電流を発生させることができる。この曲線電流が、電極形状を櫛歯形状にすることにより減少する直線電流を補うため、寄生容量値を低減させても、低減させる前とほぼ変わらないオン電流値を維持させることができる。

(もっと読む)

薄膜素子用基板の製造方法、薄膜素子の製造方法、薄膜トランジスタの製造方法、薄膜素子、および薄膜トランジスタ

【課題】本発明は、表面平滑性に優れ、薄膜素子の特性劣化を抑制することが可能な薄膜素子用基板が得られる新規な薄膜素子用基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、金属基材に薬液処理を施す金属基材表面処理工程と、上記金属基材上にポリイミド樹脂組成物を塗布して絶縁層を形成する絶縁層形成工程とを有し、上記絶縁層の表面粗さRaが30nm以下であることを特徴とする薄膜素子用基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを目的の一とする。

【解決手段】酸化物半導体層を有するトランジスタにおいて、ゲート絶縁層を酸化ガリウム膜として、酸化物半導体層と接する構成とする。また、酸化物半導体層の上下を挟むように酸化ガリウム膜を配置することによって信頼性の向上を実現する。また、ゲート絶縁層は、酸化ガリウム膜と酸化ハフニウム膜の積層構造としてもよい。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置

を提供することを課題の一とする。また、同一基板上に複数種類の薄膜トランジスタの構

造を作製して複数種類の回路を構成し、増加する工程数が少ない半導体装置の作製方法を

提供することを課題の一とする。

【解決手段】絶縁表面上に金属薄膜を成膜した後、酸化物半導体層を積層し、その後、加

熱処理などの酸化処理を行うことで金属薄膜の一部または全部を酸化させる。また、論理

回路などの高速動作を優先する回路と、マトリクス回路とで異なる構造の薄膜トランジス

タを配置する。

(もっと読む)

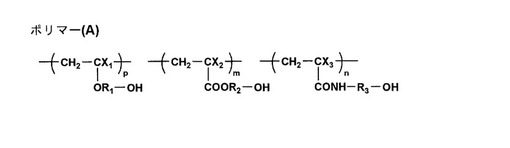

有機電子デバイス用電極

【課題】透明性、導電性且つ生産後のロール状態での保存性が良好な有機電子デバイス用電極の提供。

【解決手段】透明基材上に、導電性の金属細線パターンと、導電性ポリマー層を設けた有機電子デバイス用電極において、該金属細線パターンの金属細線の厚みをaとし、開口部における該導電性ポリマー層の厚みをbとしたとき、以下式1〜式3で表される条件を満たし、且つ、導電性ポリマー層がπ共役系導電性高分子とポリアニオンとを含んでなる導電性ポリマーおよび下記ポリマー(A)を有する有機電子デバイス用電極。0.2≦a≦2.0(式1)0.2≦b≦2.0(式2)−0.2≦b−a≦1.8(式3) (もっと読む)

(もっと読む)

半導体装置

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

充填用基材及びそれを用いた充填方法

【課題】充填時の溶融温度が低く、凝固後は高い融点を確保することができ、しかも、作業操作性に優れた充填用基材及びそれを用いた充填方法を提供すること。

【解決手段】充填用基材5は、第1金属層21と第2金属層22とを含む金属層2を支持基体1の一面上に設けた構造になっている。第1金属層21は、その融点よりも低い温度で溶融可能なナノ金属粒子の集合したものでなり、第2金属層22は、その融点が第1金属層21の融点よりも低い金属粒子の集合したものでなる。充填用基材5の一面側を、微細空間30の開口する基板3の一面上に重ねる。そして、充填用基材5を加熱し、かつ、加圧F1して、金属層2の溶融物を微細空間30内に充填する。

(もっと読む)

薄膜トランジスタ、その製造方法、及びこれを含む表示装置

【課題】不完全結晶成長領域を含まない多結晶シリコンでゲート電極または遮光部材のような金属パターン上に位置する半導体層を形成することにより、駆動特性及び信頼性を向上させる薄膜トランジスタ、その製造方法、及びこれを含む表示装置を提供する。

【解決手段】多結晶シリコンで形成された半導体層142を含む薄膜トランジスタにおいて、前記半導体層と基板110との間に前記半導体層と絶縁するように位置する金属パターンをさらに含み、前記半導体層の多結晶シリコンは、結晶成長方向と平行な結晶粒界を含み、表面における波状線の最大ピークと最小ピークとの間の距離として定義される表面粗度が15nm以下である。

(もっと読む)

薄膜のパターニング方法及び表示パネルの製造方法

【課題】コンタクトホールをより微細に形成することができる薄膜のパターニング方法及び表示パネルの製造方法を提供する。

【解決手段】所定の段差部を有した絶縁層25を形成する工程と、スパッタ法により前記段差部を覆うようにして前記絶縁層25上に犠牲層28を成膜する工程と、前記段差部に対応する領域における前記犠牲層28のうちの少なくとも一部の除去と、前記除去により前記犠牲層28から露出された領域における前記絶縁層25の除去とを、ドライエッチングにより連続して行う工程と、前記ドライエッチングで残存した前記犠牲層28の少なくとも一部をウェットエッチングにより除去する工程と、を有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を含むトランジスタにおいて、酸化物半導体膜に接し、且つソース電極およびドレイン電極を覆う帯電防止機能を有する金属酸化膜を形成し、該金属酸化膜を通過してハロゲン元素を導入(添加)し、加熱処理を行う。このハロゲン元素導入および加熱工程によって、水素、水分、水酸基または水素化物などの不純物を酸化物半導体膜より意図的に排除し、酸化物半導体膜を高純度化する。また、金属酸化膜を設けることで、トランジスタにおいて酸化物半導体膜のバックチャネル側に寄生チャネルが発生するのを防止する。

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

熱処理方法および熱処理装置、ならびに半導体装置の製造方法

【課題】従来技術よりも小さい熱エネルギーで、SiC基板上に低抵抗のオーミック電極を形成することができ、熱処理における半導体装置の素子部の損傷および特性の劣化を防止することができる熱処理方法および熱処理装置、ならびに前記熱処理方法を用いた半導体装置の製造方法を提供する。

【解決手段】熱処理装置1の電源部21によって、複数のパルスを含むパルス列で構成される複数パルス電流を発生させ、導線22および電流端子部23を介して、SiC基板11上の電極金属膜12に供給する。これによって電極金属膜12にジュール熱を発生させ、発生したジュール熱によって電極金属膜12を加熱する。

(もっと読む)

薄膜電界効果型トランジスタの製造方法

【課題】TFT特性が良好であり、しかも面内均一性等も良好な薄膜電界効果型トランジスタを低コストで提供すること。

【解決手段】基板上に、少なくともゲート電極、絶縁膜、活性層、ソース電極およびドレイン電極が形成され、活性層上にソース電極およびドレイン電極が設けられた薄膜電界効果型トランジスタの製造方法である。本発明の製造方法は、エッチング液として、りん酸、酢酸および硝酸を含む混酸水溶液を用いて、ソース電極およびドレイン電極を形成する工程を有する。この活性層は、In、GaおよびZnを含むアモルファス酸化物半導体で構成されるものであり、かつZn濃度が20%未満であり、In濃度が40%以上であり、Ga濃度が37%以上である。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】基板の表面粗度によらず膜表面が平坦であり、信頼性が高く、製造コストを低減させた薄膜トランジスタ及びその製造方法を提供する。

【解決手段】可撓性のプラスチック基板10上に、ゲート電極11、ゲート絶縁層12、半導体活性層13、ソース電極14、及びドレイン電極15を順次形成するボトムゲート型薄膜トランジスタ1の製造方法である。ゲート絶縁層12は、プラスチック基板10上に下部層12aと該下部層12a上に積層された少なくとも一層以上の上部層12bとがこの順で形成されてなり、下部層12aは、炭素含有酸化シリコンを含む材料からなり、下部層12aの炭素濃度が、15atm%以上40atm%以下となるように真空紫外光CVD法により形成される。

(もっと読む)

貫通孔配線基板の製造方法

【課題】めっき反応速度を調整することでめっき未着を防ぐことが可能な貫通孔配線基板の製造方法を提供することである。

【解決手段】微小デバイスを構成する貫通孔配線基板の製造方法であって、基板40の両表面を貫通する貫通孔41を形成する工程と、貫通孔41の少なくとも内表面にNiめっきを成長させる工程と、を備え、貫通孔41の少なくとも内表面にNiめっきを成長させる工程では、Niめっきの析出レートを50nm/min未満にしてめっきを成長させる。

(もっと読む)

241 - 260 / 1,522

[ Back to top ]