Fターム[4M104BB13]の内容

Fターム[4M104BB13]の下位に属するFターム

Fターム[4M104BB13]に分類される特許

301 - 320 / 1,522

金属及びシリコンの交互層を含むコンタクト構造体並びに関連デバイスの形成方法

半導体デバイスを形成する方法であって、この方法は、半導体層を準備するステップと、半導体層上に第1の金属の第1の層を準備するステップとを含む。第1の金属の第1の層上に第2の層を準備することができる。第2の層は、シリコン層及び第2の金属の層を含むことができ、第1の金属及び第2の金属は異なり得る。第1の金属はチタンとすることができ、第2の金属はニッケルとすることができる。関連するデバイス、構造体、及び他の方法もまた説明される。 (もっと読む)

電界効果トランジスタ、電子装置、電界効果トランジスタの製造方法及び使用方法

【課題】 チップ面積を大きくし過ぎることなく、過電圧、過電力が加わっても破壊されない電界効果トランジスタを提供する。

【解決手段】 本発明の電界効果トランジスタは、

半導体層上に、ゲート電極110と、ドレイン電極109と、ソース電極108と、保護ダイオード(保護ダイオード電極)111とが配置され、

ドレイン電極109が、保護ダイオード111の周囲の一部もしくは全部を囲む状態で形成されているか、または、

ドレイン電極109は、複数であり、複数のドレイン電極109の少なくとも一対のドレイン電極間に、保護ダイオード111が配置されるように形成されていることを特徴とする。

(もっと読む)

窒化物半導体素子および窒化物半導体素子のパッド電極の製造方法

【課題】p型窒化物半導体層上の透光性電極とn型窒化物半導体層との両方に好適に接続可能な構造のパッド電極を備える窒化物半導体素子を提供する。

【解決手段】窒化物半導体素子10は、基板1上に、n型窒化物半導体層2、活性層3、p型窒化物半導体層4を積層してなり、n型、p型窒化物半導体層2,4にそれぞれ電気的に接続するn側パッド電極7n、p側電極5をさらに備える。p側電極5は、p型窒化物半導体層4上に形成された導電性酸化物からなる透光性電極6と、透光性電極6上の一部の領域に形成されたp側パッド電極7pとからなる。そして、n側パッド電極7nおよびp側パッド電極7pは、n型窒化物半導体層2および透光性電極6のそれぞれに接触する側から、Cr層71a、Pt層71b、Ru層72、Au層73を積層してなり、Cr層71aの厚さは1nm以上9nm未満であることを特徴とする。

(もっと読む)

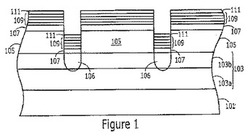

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

半導体装置

【課題】ボンディングメタル層の材料によるショットキ界面の劣化を抑制または防止して、デバイス特性を改善する。

【解決手段】ショットキダイオードは、半導体基板10と、この半導体基板10にショットキ接触するショットキ金属層15と、ショットキ金属層15上に形成されたボンディングメタル層16とを含む。ショットキ金属層15は、金属窒化物層32bを含む金属窒化物含有多結晶金属層32からなるバリア層と、これに積層された金属層31とを有している。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート閾値電圧を低下させることなく、チャネル移動度を向上できる炭化珪素MOSFETを提供する。

【解決手段】炭化珪素半導体装置200は、炭化珪素基板10と、炭化珪素基板10上に形成された炭化珪素層20と、炭化珪素層20上に形成されたゲート絶縁膜30と、ゲート絶縁膜30を介して炭化珪素層20上の所定位置に形成され、III族軽元素であるB、AlまたはGaをp型ドーパントとして含む多結晶シリコンからなるゲート電極40とを有する。そして、ゲート電極40中の上記p型ドーパントを、ゲート電極40直下の炭化珪素層20とゲート絶縁膜30との界面近傍に拡散させ、上記p型ドーパントによって界面近傍の不純物準位をパッシベーションする。

(もっと読む)

半導体装置およびその製造方法

【課題】CMPによるダミーゲート電極の頭出し工程およびCMPによるメタルゲート電極の形成工程を回避できる製造方法を提供する。

【解決手段】シリサイド膜24S,24D上に選択的に、シリコン膜25S,25Dを形成する工程と、側壁絶縁膜23WA,23WBの間にシリコン基板の表面を露出する凹部23Vを形成する工程と、側壁絶縁膜23WA,23WBの表面および露出されたシリコン基板表面を連続して覆うように、誘電体膜を形成する工程と、シリコン基板上に金属または導電性金属窒化物を含む導電膜を、凹部23Vに誘電体膜を介して充填するように形成する工程と、導電膜をエッチバックし、側壁絶縁膜23WA,23WBの間において凹部23Vを誘電体膜を介して充填するゲート電極を形成する工程と、を含む。

(もっと読む)

整流素子

【課題】定常損失を低減しつつ耐圧を向上することのできる整流素子を提供する。

【解決手段】ショットキー電極3は、SiCよりなるn-半導体層2とショットキー接触し、かつSiCよりなるp型半導体層5a,5bと電気的に接続している。ショットキー電極3とカソード電極4との電位差が変化することにより、ショットキー電極3とカソード電極4との間に電流を流す状態と、p型半導体層5a,5bに囲まれるn-半導体層2を空乏層化させてショットキー電極3とカソード電極4との間の電流経路を遮断する状態とを選択可能である。n-半導体層2とショットキー電極3との間のショットキー障壁φBn1が、0.68eV<φBn1<1.05eVであり、かつ250℃の温度でも、そのショットキー接触を確保できる。

(もっと読む)

III−V族半導体装置の導電性の改善

III-V族半導体装置における導電性の改善について示した。第1の改良は、チャネル層とは幅の異なるバリア層を有することである。第2の改良は、金属/Si、Ge、またはシリコン-ゲルマニウム/III-Vスタックの熱処理により、Siおよび/またはゲルマニウムドープIII-V層に、金属-シリコン、金属-ゲルマニウム、または金属-シリコンゲルマニウム層を形成することである。次に、金属層が除去され、金属-シリコン、金属-ゲルマニウム、または金属シリコンゲルマニウム層上に、ソース/ドレイン電極が形成される。第3の改良は、III-Vチャネル層上に、IV族元素および/またはVI族元素の層を形成し、熱処理し、III-Vチャネル層に、IV族および/またはVI族化学種をドープすることである。第4の改良は、III-V装置のアクセス領域に形成された、パッシベーション層および/またはダイポール層である。  (もっと読む)

(もっと読む)

電気光学装置用基板及びその製造方法、電気光学装置並びに電子機器

【課題】電気光学装置用基板において、製造コストを低減すると共に、アライメント精度を高める。

【解決手段】電気光学装置用基板は、基板上に設けられた第1の絶縁膜(310)と、複数の画素(20)と、複数の画素にわたって第1の絶縁膜に設けられた第1の凹部と、第1の凹部の底面に設けられた第2の凹部と、第2の凹部に設けられた有機半導体層(241)と、該有機半導体層の上に設けられたゲート絶縁膜(245)と、該ゲート絶縁膜の上に設けられたゲート電極と、を含み、複数の画素のうち一の画素に対応づけられた薄膜トランジスタ(24)と、ゲート絶縁膜の上層であって、複数の画素にわたって第1の凹部に設けられた走査線(40)と、薄膜トランジスタと電気的に接続されたデータ線(50)と、を備える。

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

電界効果トランジスタ

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

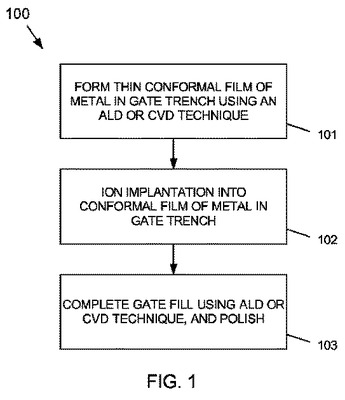

イオン注入を用いた圧縮金属ゲート応力の導入によるトライゲートMOSFETの駆動電流の増大化

半導体デバイスは、フィン及び金属ゲート膜を有する。フィンは半導体材料の表面に形成されている。金属ゲート膜は、フィン上に形成され、且つ金属ゲート内に圧縮応力を形成するために当該金属ゲート膜内に注入されたイオンを有する。典型的な一実施形態において、半導体材料の表面は(100)結晶格子方向を有し、フィンの方向は、半導体材料の結晶格子に関して<100>方向に沿っている。典型的な他の一実施形態において、半導体材料の表面は(100)結晶格子方向を有し、フィンの方向は、半導体材料の結晶格子に関して<110>方向に沿っている。フィンは、金属ゲート膜内の圧縮応力によって生成される面外圧縮を有する。  (もっと読む)

(もっと読む)

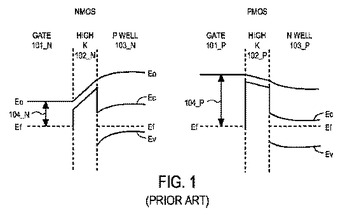

デュアル仕事関数ゲート構造

トランジスタを有する半導体チップが記載されている。前記トランジスタは、ゲート誘電体にわたって設けられたゲート電極を有する。前記ゲート電極は、前記ゲート誘電体上に設けられた第1ゲート材料、及び前記ゲート誘電体上に設けられた第2ゲート材料を有する。前記第1ゲート材料は前記第2ゲート材料とは異なる。前記第2ゲート材料はまた、前記ゲート電極のソース領域又はドレイン領域にも設けられている。  (もっと読む)

(もっと読む)

半導体装置、および、その製造方法

【課題】半導体素子の特性を向上させると共に、半導体素子の微細化を容易に実現する。

【解決手段】半導体素子101にてゲート電極111gが設けられる部分の表面を凹凸面に形成する。ここでは、凹凸面のうち凸部CVでは、一対のソース・ドレイン領域112s,112dの表面と同一の面を覆うようにゲート絶縁膜111zを形成し、そのゲート絶縁膜111zの上面にゲート電極111gを設ける。これに対して、凹部TRでは、一対のソース・ドレイン領域112s,112dの表面から内部へ向けて設けられた溝Mの面を覆うようにゲート絶縁膜111zを形成し、その溝Mの内部を埋め込むようにゲート電極111gを設ける。

(もっと読む)

半導体素子、半導体装置及びそれらの作製方法

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

半導体装置の製造方法

【課題】最近の多層メタルスパッタリング成膜プロセスにおいては、従来のマルチチャンバ型の装置に代わって、単一チャンバ&マルチ成膜サイト型の装置が広く使用されるようになっている。しかし、本願発明者が検討したところによると、このような単一チャンバ&マルチ成膜サイト型スパッタリング成膜装置は、磁性メタル膜と非磁性メタル膜を積層形成する場合は、被処理ウエハを別の成膜サイトに移送して成膜する必要があり、スループットを大きく低下させていることが明らかとなった。

【解決手段】本願発明は、単一チャンバ&マルチ成膜サイト型多層スパッタリング成膜装置を用いた半導体装置の製造方法において、少なくとも一つの成膜サイトにおいて、磁性および非磁性ターゲットの両方を切り替えて用い、磁性および非磁性膜の両方の膜を成膜するものである。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたpチャネル型トランジスタを提供することを目的の一とする。また、酸化物半導体を用いたnチャネル型トランジスタとpチャネル型トランジスタとのCMOS(相補型金属酸化物半導体)構造を提供することを目的の一とする。

【解決手段】ゲート電極層と、ゲート絶縁層と、酸化物半導体層と、前記酸化物半導体層と接するソース電極層及びドレイン電極層とを含み、前記酸化物半導体層に用いる酸化物半導体の電子親和力をχ(eV)、バンドギャップをEg(eV)とすると、前記ソース電極層及び前記ドレイン電極層に用いる導電体の仕事関数φmは、φm>χ+Eg/2を満たし、かつ、χ+Eg−φmで表される正孔に対する障壁φBPは0.25eV未満である、酸化物半導体を用いたpチャネル型トランジスタを提供する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

301 - 320 / 1,522

[ Back to top ]