Fターム[4M104BB20]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | CoSi (1,014)

Fターム[4M104BB20]に分類される特許

201 - 220 / 1,014

半導体装置とその製造方法

【課題】

メタルゲートを有するpチャネルMISトランジスタとメタルゲートを有するnチャネルMISトランジスタとを、少ない工程数で形成する。

【解決手段】

半導体装置は、シリコン層を有する半導体基板と、半導体基板に画定されたn型活性領域とp型活性領域と、n型活性領域の上方に形成され、酸化シリコンより高い誘電率を有し、表面にAlを含有する第1高誘電率ゲート絶縁膜と、p型活性領域の上方に形成され、酸化シリコンより高い誘電率を有する第2高誘電率ゲート絶縁膜と、第1高誘電率ゲート絶縁膜および第2高誘電率ゲート絶縁膜の各々の上に形成され、nチャネルトランジスタに適した仕事関数を有する金属又は金属化合物を含む材料で形成された、第1ゲート電極および第2ゲート電極と、を有することを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクト抵抗を低くし、かつ半導体装置が大型化することを抑制する。

【解決手段】能動素子は、第1電極210(ゲート電極)及び第2電極220(拡散層領域)を有している。ゲート電極210の表面には第1金属化合物層212(シリサイド層)が形成されており、拡散層領域220の表面には第2金属化合物層222(シリサイド層)が形成されている。ゲート電極210には第1コンタクト310が接続しており、拡散層領域220には第2コンタクト320が接続している。第1コンタクト310は、基板200に平行な方向の断面形状が長方形又は楕円であり、かつ下端が第1金属化合物層212に入り込んでいるが、突き抜けていない。第2コンタクト320は、基板200に平行な方向の断面形状が円である。

(もっと読む)

半導体装置

【課題】ゲートパルスストレスによる耐圧劣化およびしきい値電圧の変動を抑制できる半導体装置を提供する。

【解決手段】ゲート電極GEは、ソース領域およびドリフト領域DRに挟まれる領域上に絶縁層FOを介在して形成されている。フィールドプレートFPは、ゲート電極GEおよびドリフト領域DR上を延在し、かつゲート電極GEに電気的に接続されている。ダミー導電層DCは、フィールドプレートFPとドリフト領域DRとの間において絶縁層FO上に形成され、かつソース領域に電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】平坦性に優れ、リーク電流低減効果の高いコバルトシリサイドを提供する。

【解決手段】半導体基板上のトランジスタの拡散層上にコバルトシリサイドを形成する工程を含む半導体装置の製造方法であって、少なくとも拡散層上に基板加熱を行うことなく第1のコバルト膜9をスパッタ成膜した後、200〜350℃で第2のコバルト膜10を積層し、シリサイド化を行う。

(もっと読む)

半導体装置の製造方法および製造装置

【課題】王水等の薬液によるシリサイド膜表面における腐食発生を抑制し、良好なPt含有シリサイド膜を形成する半導体装置の製造方法と、それを実現する半導体装置の製造装置とを提供する。

【解決手段】半導体装置の製造方法は、半導体層を有する基板上または基板上に形成された導電膜上に、貴金属を含む合金膜を形成する工程(a)と、基板に対して熱処理を行って貴金属とシリコンとを反応させ、基板上または導電膜上に貴金属を含むシリサイド膜を形成する工程(b)と、工程(b)の後、第1の薬液を用いて未反応記合金膜を除去する工程(c)と、基板を酸化性雰囲気に曝すことによって、貴金属の残渣の下に位置する部分を含むシリサイド膜の上面上にシリコン酸化膜を形成する工程(d)と、第2の薬液を用いて貴金属の残渣を溶解する工程(e)とを備えている。

(もっと読む)

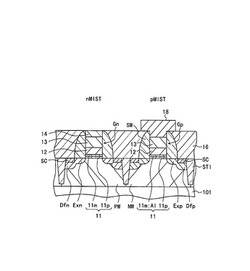

MISトランジスタ

【課題】ゲート電極とソース/ドレイン電極間で電気的短絡を起こし難いMISトランジスタを得る。

【解決手段】サイドウォール15を二重構造とする。バッファ層13は窒化酸化シリコンで形成され、バッファ層13の上に窒化シリコン層14が形成される。このサイドウォール15をマスクとしてシリサイド膜10を形成する。バッファ層13は窒化酸化シリコンのみならず、酸化シリコンで形成されてもよい。シリサイド膜はコバルトシリサイドでも、ニッケルシリサイドでもよい。窒化シリコン層14はバッファ層13よりも大きい応力を持つ。

(もっと読む)

半導体装置の製造方法

【課題】消費電力の少ない半導体装置の製造方法を提供する。

【解決手段】ゲート電極13の多結晶シリコン領域と、ゲート電極13下のチャネル領域11Cを挟んで配置された一対の単結晶シリコン領域11S,11Dとが形成されたシリコン基板11に対して、単結晶シリコン領域11S,11D上に単結晶のSiGe混晶層領域14A,14Bを成長させ、且つ多結晶シリコン領域13上に多結晶のSiGe混晶層領域14Cを成長させる工程と、Clを含むガスを用いて、一対の単結晶シリコン領域11S,11D上に成長したSiGe混晶層領域14A,14Bの表面側の一部を取り除くと共に、多結晶シリコン領域13上に成長したSiGe混晶層領域14Cを取り除く工程と、一対の単結晶シリコン領域上のSiGe混晶層領域14A,14B上に単結晶のシリコン層15A,15Bを成長させる工程と、シリコン層15A,15Bをシリサイド化する工程と、を有する。

(もっと読む)

高アスペクト比プラグの充填方法

【課題】高アスペクト比を有するプラグを充填する方法を提供する。

【解決手段】高アスペクト比を有するプラグを充填する本発明の方法においては、核形成層を、バイアの側壁上ではなく、バイアの底に形成する。プラグ充填はバイアの底からトップへの方向であり、側壁から内側へではない。得られるプラグは、無ボイドであり、継ぎ目無しである。

(もっと読む)

半導体装置

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】酸化珪素膜上の第1及び第2のシリサイド、チャネル形成領域、ソース領域及びドレイン領域を有する結晶性珪素膜と、チャネル形成領域上のゲイト絶縁膜と、ゲイト絶縁膜上のゲイト電極と、ゲイト電極の側面に設けられた側壁と、第1のシリサイドに接して設けられた第1の金属配線と、第2のシリサイドに接して設けられた第2の金属配線と、を有し、第1のシリサイドは、ソース領域の上面の一部及び側面に設けられ、第2のシリサイドは、ドレイン領域の上面の一部及び側面に設けられ、第1の金属配線と第2の金属配線は同一金属膜をエッチングして形成された構造であり、第1及び第2のシリサイドは、金属膜に用いられる金属を用いて形成されたシリサイドである。

(もっと読む)

半導体装置及びその製造方法

【課題】前記従来のエアーギャップを有するMISトランジスタ及びその製造方法では、ゲート電極の周囲にエアーギャップを設けるため、ゲート電極に近接して応力絶縁膜を形成することができない。

【解決手段】半導体装置は、ゲート絶縁膜13と、ゲート電極14と、ソースドレイン領域19と、コンタクトプラグ22と、応力絶縁膜23とを備えている。ゲート電極14の側方のうちゲート電極14とコンタクトプラグ22との間に位置する領域のみに空洞24が形成されており、応力絶縁膜23は半導体基板10上にゲート電極14を覆うように形成されており、半導体基板10におけるゲート電極14の直下に位置するチャネル領域に対して応力を生じさせる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜を表面研磨する工程を経て形成される半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に、高耐圧ゲート絶縁膜IG1および高耐圧ゲート電極EG1からなる高耐圧ゲートG1を形成した後、サリサイドブロック膜SAB、層間絶縁膜ILを順に形成し、その層間絶縁膜ILをCMPにより研磨する。サリサイドブロック膜SABは、下層から順に酸化シリコンを主体とする絶縁膜である保護酸化膜t1と、窒化シリコンを主体とする絶縁膜である保護窒化膜t2とによって形成する。また、層間絶縁膜ILの研磨は、高耐圧ゲートG1上面のサリサイドブロック膜SABに達するまで研磨する。

(もっと読む)

ゲート・スタックを形成する方法

【課題】 電界効果トランジスタのためのゲート・スタックを形成する方法を提供すること。

【解決手段】 方法は、第1及び第2の型の電界効果トランジスタに対して指定された半導体基板の領域を覆う第1の窒化チタン(TiN)層の上に直接、金属含有層を形成することと、金属含有層の上に第2のTiN層のキャッピング層を形成することと、第1の型の電界効果トランジスタに対して指定された領域を覆う第1のTiN層の第1の部分のみを覆うように、第2のTiN層及び金属含有層をパターン形成してすることと、第1のTiN層の第1の部分をパターン形成された金属含有層の厚さの少なくとも一部で覆うことによりエッチングから保護する一方で、パターン形成によって露出された第1のTiN層の第2の部分をエッチング除去することと、第2の型の電界効果トランジスタに対して指定された半導体基板の領域を覆う第3のTiN層を形成することとを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極上にシリサイド層を安定して形成すること。

【解決手段】メモリセル100は、シリコン基板10と、シリコン基板10上に互いに隣り合って配置されたゲート電極12、13と、シリコン基板10とゲート電極12間に形成された絶縁層30と、シリコン基板10とゲート電極12間に形成された電荷蓄積層26と、を備え、ゲート電極12は、シリコン基板10から離間するに従って少なくとも部分的に幅広になる。シリコン基板10から離間するに従って少なくとも部分的に幅広となるようにゲート電極12を形付けることで、シリサイド層45を安定して形成することが実現可能になる。

(もっと読む)

光起電力素子を形成するための組成物と方法

シリコン太陽電池を含む光電池と、このような光電池を作製するための方法と組成物が提供される。p型シリコンベースとn型シリコン層を有するシリコン基板に、窒化シリコン層、窒化シリコン層と接触する交換金属および、交換金属と接触する非交換金属が提供される。このアセンブリを焼成して、シリコン基板上に金属シリサイドの接点と、金属シリサイドの接点と接触する導電性金属電極を形成する。交換金属はニッケル、コバルト、鉄、マンガニーズ、モリブデンおよびそれらの組み合わせからのものであり、非交換金属は銀、銅、錫、ビスマス、鉛、アンチモン、ヒ素、インジウム、亜鉛、ゲルマニウム、金、カドミウム、ベリリウムおよびそれらの組み合わせからのものである。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】半導体集積回路装置の集積度の向上を図ることのできる技術を提供する。

【解決手段】セルの高さ方向に隣接して配置されるセルrow上段の2入力NAND回路6とセルrow下段のインバータ回路1との間の結線に、2層目以上の配線を用いずに、1層目の配線M1よりも下層に位置し、2入力NAND回路6またはインバータ回路1を構成するMISFETのゲート電極7N2,7P2と一体化した導電体膜からなる配線8を用いる。

(もっと読む)

半導体装置

【課題】トランジスタの集積化を妨げることなく、トランジスタの駆動力を向上させる半導体装置を提供する。

【解決手段】所定の結晶からなる半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、ゲート幅方向に凸部を有して前記半導体基板内に形成され、前記所定の結晶とは異なる格子定数を有するエピタキシャル結晶が埋め込まれたソース・ドレイン領域と、を具備するトランジスタと、前記凸部以外の前記ソース・ドレイン領域に接続されたコンタクトプラグと、を備えた半導体装置を提供する。

(もっと読む)

ショットキーバリア量子井戸共振型トンネルトランジスタ

【課題】ショットキーバリア量子井戸のトンネルトランジスタを提供する。

【解決手段】素子構造は、一つ或は複数の導電ベースリージョン33、第一半導体バリアーリージョン、第二半導体バリアーリージョン、導電エミッタリージョン31、導電コレクタリージョン35などを含み、第一半導体バリアーリージョン或は第二半導体バリアーリージョンのサイズは100Åより小く、第一ショットキーバリアの接合を第一半導体バリアーリージョンと導電ベースリージョンのインターフェイスで生じ、第二ショットキーバリアの接合を第二半導体バリアーリージョンと導電ベースリージョンのインターフェイスで生じ、第三ショットキーバリアの接合を導電エミッタリージョンと第一半導体バリアーリージョンのインターフェイスで生じ、第四ショットキーバリアの接合を導電コレクタリージョンと第二半導体バリアーリージョンのインターフェイスで生じる。

(もっと読む)

相補型半導体装置とその製造方法

【課題】 マルチゲートMISFETからなる高移動度のnFET及びpFETの双方の移動度を向上させる相補型半導体装置とその製造方法を提供する。

【解決手段】

基板10上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された相補型半導体装置であって、nチャネルMISトランジスタ及びpチャネルMISトランジスタが、基板10の主面に平行な面内に引っ張り歪みを有する第一の半導体層と圧縮歪みを有する第二の半導体層とが交互に積層され、基板10の主面に対して突出した積層構造と、積層構造の対向する両側面を覆うように形成されたゲート絶縁膜80と、ゲート絶縁膜80を介して前記積層構造を覆って形成されたゲート電極30と、ゲート絶縁膜80とゲート電極30をはさんで対向し、積層構造の両端に形成されたソース/ドレイン領域20と、を有することを特徴とする相補型半導体装置。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

201 - 220 / 1,014

[ Back to top ]