Fターム[4M104BB22]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | PtSi (542)

Fターム[4M104BB22]に分類される特許

121 - 140 / 542

半導体装置及びその製造方法

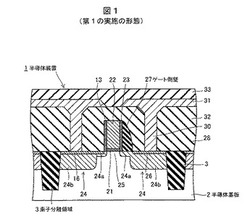

【課題】製造プロセスにおいてフォトレジスト構造等の追加工程を必要としない、非対称なDSS構造の半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2上にゲート絶縁膜21を介して形成されたゲート電極22と、ゲート電極22の側面に形成されたオフセットスペーサ13、23と、一方のオフセットスペーサ23の側面に形成されたゲート側壁27と、半導体基板2中のゲート絶縁膜21下に形成されたチャネル領域25と、半導体基板2内のチャネル領域25を挟む領域に形成され、チャネル領域25側に導電型不純物が偏析して形成されたエクステンション領域24aを有するソース・ドレイン領域24と、ソース・ドレイン領域24上にオフセットスペーサ13に接して形成されたシリサイド層16、及び、ゲート側壁27に接して形成されたシリサイド層26と、を有した半導体装置1とする。

(もっと読む)

コンタクト形成方法、半導体装置の製造方法、および半導体装置

【課題】 低抵抗率のコンタクトを実現した半導体装置の製造方法を提供する。

【解決手段】半導体と接した第1の金属層を酸化防止用の第2の金属層で覆った状態で、第1の金属層のみをシリサイド化し、酸素混入のないシリサイド層を形成する。第1の金属層の材料として、半導体との仕事関数の差が所定の値となるような金属が用いられ、第2の金属層の材料として、アニール温度で第1の金属層と反応しない金属が用いられる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ショットキー接触を発生させることなく、炭素の析出を抑制することにより配線の密着性を向上したオーミック電極を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】

SiC半導体装置においてオーミック電極を形成する際に、SiC層11の一方の主表面上には、1種の第1の金属元素からなる、第1の金属層12を形成する。また、第1の金属層の、SiC層11と対向する表面とは反対側の表面上(図1における上側)に、SiからなるSi層13を形成する。このようにして形成した積層構造10Aに対して熱処理を行なう。以上により、電極の表面層への炭素原子の析出や、SiとSiCとによるショットキー接触の形成が抑制された、配線との良好な密着性を示すオーミック電極を有する炭化珪素半導体装置を得ることができる。

(もっと読む)

トランジスタにおいて進歩したシリサイド形成と組み合わされる凹型のドレイン及びソース区域

【解決手段】

洗練されたトランジスタ要素を形成するための製造プロセスの間、それぞれの金属シリサイド領域を形成するのに先立つ共通のエッチングシーケンスにおいて、ゲート高さが減少させられてよく、そして凹型のドレイン及びソース構造もまた得られてよい。対応する側壁スペーサ構造はエッチングシーケンスの間に維持され得るので、ゲート電極におけるシリサイド化プロセスの可制御性及び均一性を高めることができ、それにより、低減された程度のスレッショルドばらつきを得ることができる。更に、凹型のドレイン及びソース構造が、全体的な直列抵抗の低減及び応力転移効率の増大をもたらすことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】SRAMにおいてNMOS及びPMOSトランジスタのバランスを確保して、PMOSトランジスタの閾値電圧を高くできる半導体装置及びその製造方法を提供する。

【解決手段】メモリ領域において、基板の第1半導体領域(12,13)の第1チャネル形成領域上に第1ゲート絶縁膜(20,21)を介して第1ゲート電極が形成され、第1半導体領域に第1ソースドレイン領域(16,17)が形成されて第1トランジスタが形成され、ロジック領域において、基板の第2半導体領域(14,15)の第2チャネル形成領域上に第2ゲート絶縁膜(22,23)を介して第2ゲート電極が形成され、第2半導体領域に第2ソースドレイン領域(18,19)が形成されて第2トランジスタが形成され、第1ゲート電極の第1ゲート絶縁膜に接する部分が金属(40,41)からなり、第2ゲート電極の第2ゲート絶縁膜に接する部分が半導体(26,27)からなる。

(もっと読む)

半導体装置およびフォトマスク

【課題】シェアードコンタクトホールの開口不良を抑制できる半導体装置およびフォトマスクを提供する。

【解決手段】シェアードコンタクトホールSC1、SC2は、ゲート電極層GE1、GE2とドレイン領域PIRとの双方に達している。平面視において、ゲート電極層GE1、GE2の一方側壁E2が、一方側壁E1の仮想延長線E1aよりも他方側壁E4側にずれて位置している。平面視において、ゲート電極層GE1、GE2のシェアードコンタクトホールSC1、SC2が達する部分の線幅D1の中心線(C2−C2)が、ゲート電極層GE1、GE2のチャネル形成領域CHN1、CHN2上に位置する部分の線幅D2の中心線(C1−C1)に対してずれて位置している。

(もっと読む)

半導体装置、およびその製造方法

【課題】製造工程におけるエピタキシャル結晶層への熱的負荷を低減することのできる半導体装置、およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板上に第1のゲート絶縁膜を介して形成された第1のゲート電極、前記半導体基板中の前記第1のゲート絶縁膜下に形成された第1のチャネル領域、前記半導体基板中の前記第1のチャネル領域の両側に形成された第1の結晶からなる第1のエピタキシャル結晶層、を含む第1のトランジスタと、前記半導体基板上に第2のゲート絶縁膜を介して形成された第2のゲート電極、前記半導体基板中の前記第2のゲート絶縁膜下に形成された第2のチャネル領域、前記半導体基板中の前記第2のチャネル領域の両側に形成された第2の結晶からなる第2のエピタキシャル結晶層、前記第2のエピタキシャル結晶層上に形成された前記第1の結晶からなる第3のエピタキシャル結晶層、を含む、前記第1のトランジスタと異なる導電型を有する第2のトランジスタと、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】極浅接合の深さが精密制御された半導体装置およびその製造方法を提供する。

【解決手段】主面が第1面方位である第1導電型の第1半導体層11と、第1半導体層11上に直接接合され、主面が第1面方位と異なる第2面方位である第1導電型の第2半導体層12と、第2半導体層12に連接して第1半導体層11上に形成され、主面が第1面方位である第3半導体層13a、13bと、第2半導体層12上にゲート絶縁膜を介して形成されたゲート電極15と、ゲート電極15をゲート長方向に挟むように第2半導体層12に形成され、第1半導体層11と第2半導体層12との接合面16に至る第2導電型の第1不純物拡散領域17a、17bと、第1不純物拡散領域17a、17bをゲート長方向に挟むように第3半導体層13a、13bから第1半導体層11の上部にかけて形成された第2導電型の第2不純物拡散領域18a、18bと、を具備する。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低減に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板11と、前記半導体基板上にゲート絶縁膜12を介して設けられるゲート電極13と、前記半導体基板中に前記ゲート電極を挟むように隔離して設けられるエクステンション領域LDDと、前記エクステンション領域の両側を挟むように前記半導体基板中に設けられ、前記半導体基板とは異なる格子定数有し、前記半導体基板に歪みを付与する歪み付与層22と、前記エクステンション領域の両側の前記半導体基板中に前記ゲート電極を挟むように隔離して設けられるソース/ドレインS/Dと、前記ソース/ドレイン上に設けられるシリサイド層SS/Dとを具備し、前記歪み付与層と前記半導体基板との界面Si-Siは、少なくとも前記シリサイド層の底面の一部に一致する。

(もっと読む)

ショットキーバリアダイオードとその製造方法

【課題】ショットキーバリア金属として白金を用いた場合でも、酸化膜に接触して覆う金属層の剥がれを抑制することのできるショットキーバリアダイオードを提供する。

【解決手段】ショットキーバリア金属層と外部接続用金属電極との間にバナジウム、クロム、ジルコニウムおよびタンタルから選ばれるいずれかの金属を主成分として含む中間金属層を少なくとも一層は挟む構成とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】金属微粒子と半導体基板の反応を利用して電極を形成する、高性能な半導体装置の製造方法およびグレイン粒径の小さい電極を有する高性能な半導体装置を提供する。

【解決手段】直径20nm以下の金属微粒子を溶媒中に分散した溶液を、半導体基板上に塗布する工程と、溶媒を蒸発させる工程と、金属微粒子と半導体基板を反応させ、半導体基板表面に金属半導体化合物薄膜を形成する工程とを有することを特徴とする半導体装置の製造方法。半導体基板上に金属半導体化合物薄膜を有する半導体装置であって、金属半導体化合物薄膜は膜厚方向に単グレインで形成され、単グレインの粒径が40nm以下であることを特徴とする半導体装置。

(もっと読む)

固体撮像装置、その製造方法および撮像装置

【課題】本発明は、画素部のMOSトランジスタ上で異なる2層のシリサイドブロック膜の一部が重なるように形成して、白傷、暗電流を低減することを可能にする。

【解決手段】半導体基板11に、光電変換部21を備えた画素部12とその周辺に形成された周辺回路部13を有し、画素部12のゲート電極32の側壁にサイドウォール形成膜で形成された第1サイドウォール33と、周辺回路部13のゲート電極52の側壁にサイドウォール形成膜で形成された第2サイドウォール53と、光電変換部21上および画素部12のMOSトランジスタ30の一部上にサイドウォール形成膜で形成された第1シリサイドブロック膜71と、画素部12のMOSトランジスタ30上に、第1シリサイドブロック膜71の一部上に重なる第2シリサイドブロック膜72を有し、第1、第2シリサイドブロック膜71、72で画素部12のMOSトランジスタ30上が被覆されている。

(もっと読む)

成膜方法

【課題】結晶粒径が均一な金属シリサイド膜、特にチタンシリサイド膜を形成することができる成膜方法を提供すること。

【解決手段】被処理体1のSi含有部分上の自然酸化膜を除去する工程と、被処理体1の自然酸化膜が除去されたSi含有部分上に金属シリサイド膜4を形成する工程とを具備し、金属シリサイド膜4を形成する工程は、最初にプラズマを生成せずに、成膜しようとする金属シリサイド中の金属を含有する金属含有原料ガスを所定時間供給して金属−シリコン結合を生じさせ(ii)、次いで金属含有原料ガスを供給しつつプラズマを生成して当該金属からなる金属膜を成膜し、その際の金属膜とSi含有部分との反応により金属シリサイド膜を形成する(iii)。

(もっと読む)

半導体装置の製造方法

【課題】急峻な不純物濃度のプロファイルを有するソース領域およびドレイン領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板の表面近傍に不純物を注入して不純物注入領域を形成する工程と、前記半導体基板にエッチングを施すことにより前記不純物注入領域の底部よりも深い溝を形成し、前記不純物注入領域を分断してソース領域およびドレイン領域を形成する工程と、前記溝の内部にSi系単結晶をエピタキシャル成長させてエピタキシャル結晶層を形成する工程と、前記エピタキシャル結晶層の上部にゲート絶縁膜およびゲート電極を形成する工程と、を含む。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ソース・ドレインの寄生抵抗の低減及び短チャネル効果の抑制と共にリーク電流の低減をはかる。

【解決手段】チャネル領域を構成する第1の半導体領域12と、第1の半導体領域12上にゲート絶縁膜15を介して形成されたゲート電極16と、第1の半導体領域12をチャネル長方向から挟んで形成された金属シリサイドからなるソース・ドレイン電極14と、を具備してなる電界効果トランジスタであって、ソース・ドレイン電極14は、チャネル領域の平均的な不純物濃度よりも高い不純物濃度を有し、且つチャネル領域との界面又は界面近傍に前記不純物濃度のピークを持ち、チャネル領域は、ソース・ドレイン電極との界面又は界面近傍に前記不純物濃度のピークを持つ。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極型であって、かつ簡素な構造によりオン抵抗を抑制することができる半導体装置、およびその製造方法を提供する。

【解決手段】p型領域2、4は第1のn型領域1上に設けられている。第2のn型領域3は、p型領域2、4によって第1のn型領域1と隔てられ、p型領域2、4上に設けられている。ゲート電極8は第1および第2のn型領域1、3の間にnチャネルを形成するためのものである。第1の電極6は、p型領域4と第2のn型領域3との各々に電気的に接続されている。第2の電極11は、第1のn型領域1によってp型領域2と隔てられかつ少なくとも一部が第1のn型領域1に接するように第1のn型領域1上に設けられている。第2の電極11は、金属および合金のいずれかからなり、第1のn型領域1にホールを注入するためのものである。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに異なる金属膜厚からなるゲート電極を有するn型及びp型MISトランジスタを備えた半導体装置において、ゲートリークによる劣化を抑制する。

【解決手段】半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備える。第1のMISトランジスタは、第1の活性領域12a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1の金属膜14a、及び、第1の金属膜14a上に形成された第1のシリコン膜17aを含む第1のゲート電極24Aとを備える。第2のMISトランジスタは、第2の活性領域12b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜上に形成された第1の金属膜14b、第1の金属膜14b上に形成された第2の金属膜15b、及び、第2の金属膜15bの上に形成された第2のシリコン膜17bを含む第2のゲート電極24Bとを備えている。

(もっと読む)

半導体基板の製造方法および半導体装置の製造方法

【課題】性能劣化を招く金属元素の半導体基板への侵入及び拡散を防ぐことのできる半導体基板の製造方法および半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体基板の製造方法は、半導体基板1の両面および側面に窒化膜2を形成する工程と、前記窒化膜2上の全面に、シリコンを含む酸化膜3および所定の金属を含む前駆体膜4Aを積層する工程と、前記酸化膜3と前記前駆体膜4Aとを反応させることにより、前記シリコンおよび前記所定の金属を含む自己形成バリア膜4を自己整合的に形成する工程と、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

121 - 140 / 542

[ Back to top ]