Fターム[4M104BB22]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | PtSi (542)

Fターム[4M104BB22]に分類される特許

101 - 120 / 542

半導体装置

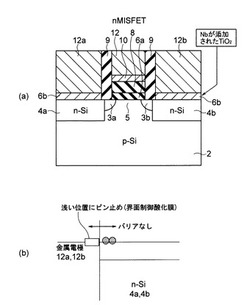

【課題】半導体または誘電体と、金属との界面において、接合する金属の実効仕事関数を最適化することを可能にするとともに、抵抗を可及的に低くすることを可能にする。

【解決手段】半導体膜4aと、半導体膜上に形成された酸化膜6bと、酸化膜上に形成された金属膜12aと、を備え、酸化膜がTi酸化膜であって、酸化膜に、V、Cr、Mn、Fe、Co、Ni、Nb、Mo、Tc、Ru、Rh、Pd、Ta、W、Re、Os、Ir、Ptから選ばれた少なくとも一つの元素が添加されている。

(もっと読む)

半導体装置の製造方法

【課題】配線層に銅配線を使用する半導体装置において、半導体基板の裏面に付着した銅原子が半導体基板の裏面から内部へと拡散することを抑制し、半導体基板の主面に形成されているMISFETなどの半導体素子の特性劣化を抑制できる技術を提供する。

【解決手段】半導体基板1Sの主面に形成される銅拡散防止膜を銅拡散防止膜DCF1aとし、半導体基板1Sの裏面に形成される銅拡散防止膜を銅拡散防止膜DCF1bとする。本実施の形態1の特徴は、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成する点にある。このように、銅配線の形成工程の前に、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成することにより、半導体基板1Sの裏面から銅原子(銅化合物を含む)が拡散することを防止できる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極との短絡を抑えたセルフアラインコンタクトを有する、製造コストの低い半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、それぞれ半導体基板2上に形成され、それぞれゲート電極4a、4bを有し、互いの間のソース・ドレイン領域8aを共有する隣接したトランジスタ1a、1bと、ゲート電極4a上に形成された絶縁膜11aと、ゲート電極4b上に形成された絶縁膜11aよりも厚さの厚い領域を有する絶縁膜11bと、ソース・ドレイン領域8aに接続され、その中心位置がゲート電極4a、4bの間の中心位置よりもゲート電極4b側に位置するSAC14と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物層が浅く形成された場合にも接合リーク電流の増大を抑制できるようにすると共に、コンタクトホール形成時に位置合わせずれが生じた場合にもコンタクト抵抗の上昇を抑制できるようにする。

【解決手段】基板100上に素子分離領域102及び不純物層103が互いに隣接するように形成されている。不純物層103上にシリサイド層106Bが形成されており、シリサイド層106B上に形成されたコンタクト109が形成されている。不純物層103とシリサイド層106Bとの界面は、素子分離領域102の上面よりも低く、シリサイド層106Bは素子分離領域102の上部コーナーを覆っている。

(もっと読む)

半導体装置の製造方法および製造装置

【課題】王水等の薬液によるシリサイド膜表面における腐食発生を抑制し、良好なPt含有シリサイド膜を形成する半導体装置の製造方法と、それを実現する半導体装置の製造装置とを提供する。

【解決手段】半導体装置の製造方法は、半導体層を有する基板上または基板上に形成された導電膜上に、貴金属を含む合金膜を形成する工程(a)と、基板に対して熱処理を行って貴金属とシリコンとを反応させ、基板上または導電膜上に貴金属を含むシリサイド膜を形成する工程(b)と、工程(b)の後、第1の薬液を用いて未反応記合金膜を除去する工程(c)と、基板を酸化性雰囲気に曝すことによって、貴金属の残渣の下に位置する部分を含むシリサイド膜の上面上にシリコン酸化膜を形成する工程(d)と、第2の薬液を用いて貴金属の残渣を溶解する工程(e)とを備えている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクト抵抗を低くし、かつ半導体装置が大型化することを抑制する。

【解決手段】能動素子は、第1電極210(ゲート電極)及び第2電極220(拡散層領域)を有している。ゲート電極210の表面には第1金属化合物層212(シリサイド層)が形成されており、拡散層領域220の表面には第2金属化合物層222(シリサイド層)が形成されている。ゲート電極210には第1コンタクト310が接続しており、拡散層領域220には第2コンタクト320が接続している。第1コンタクト310は、基板200に平行な方向の断面形状が長方形又は楕円であり、かつ下端が第1金属化合物層212に入り込んでいるが、突き抜けていない。第2コンタクト320は、基板200に平行な方向の断面形状が円である。

(もっと読む)

半導体装置及びその製造方法

【課題】前記従来のエアーギャップを有するMISトランジスタ及びその製造方法では、ゲート電極の周囲にエアーギャップを設けるため、ゲート電極に近接して応力絶縁膜を形成することができない。

【解決手段】半導体装置は、ゲート絶縁膜13と、ゲート電極14と、ソースドレイン領域19と、コンタクトプラグ22と、応力絶縁膜23とを備えている。ゲート電極14の側方のうちゲート電極14とコンタクトプラグ22との間に位置する領域のみに空洞24が形成されており、応力絶縁膜23は半導体基板10上にゲート電極14を覆うように形成されており、半導体基板10におけるゲート電極14の直下に位置するチャネル領域に対して応力を生じさせる。

(もっと読む)

半導体装置

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】酸化珪素膜上の第1及び第2のシリサイド、チャネル形成領域、ソース領域及びドレイン領域を有する結晶性珪素膜と、チャネル形成領域上のゲイト絶縁膜と、ゲイト絶縁膜上のゲイト電極と、ゲイト電極の側面に設けられた側壁と、第1のシリサイドに接して設けられた第1の金属配線と、第2のシリサイドに接して設けられた第2の金属配線と、を有し、第1のシリサイドは、ソース領域の上面の一部及び側面に設けられ、第2のシリサイドは、ドレイン領域の上面の一部及び側面に設けられ、第1の金属配線と第2の金属配線は同一金属膜をエッチングして形成された構造であり、第1及び第2のシリサイドは、金属膜に用いられる金属を用いて形成されたシリサイドである。

(もっと読む)

半導体装置

【課題】トランジスタの集積化を妨げることなく、トランジスタの駆動力を向上させる半導体装置を提供する。

【解決手段】所定の結晶からなる半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、ゲート幅方向に凸部を有して前記半導体基板内に形成され、前記所定の結晶とは異なる格子定数を有するエピタキシャル結晶が埋め込まれたソース・ドレイン領域と、を具備するトランジスタと、前記凸部以外の前記ソース・ドレイン領域に接続されたコンタクトプラグと、を備えた半導体装置を提供する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】半導体集積回路装置の集積度の向上を図ることのできる技術を提供する。

【解決手段】セルの高さ方向に隣接して配置されるセルrow上段の2入力NAND回路6とセルrow下段のインバータ回路1との間の結線に、2層目以上の配線を用いずに、1層目の配線M1よりも下層に位置し、2入力NAND回路6またはインバータ回路1を構成するMISFETのゲート電極7N2,7P2と一体化した導電体膜からなる配線8を用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられるNiPtSi電極の熱安定性を向上させる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板と、この半導体基板中のチャネル領域と、チャネル領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、チャネル領域の両側に形成され、NiおよびPtを主成分とする金属半導体化合物層からなるソース/ドレイン電極とを備え、金属半導体化合物層と半導体基板との界面において、金属半導体化合物層の単一の結晶粒と半導体基板との境界部の最大Pt濃度が、界面の平均Pt濃度よりも高いことを特徴とする半導体装置および半導体装置の製造方法。

(もっと読む)

ヘテロ接合電界効果トランジスタおよびその製造方法

【課題】ソース電極およびドレイン電極のn+層領域と2DEGチャネルとの接触抵抗を低減したヘテロ接合電界効果トランジスタを提供する。

【解決手段】基板上に設けられた電子走行層と、電子走行層の上に設けられた電子供給層と、ソース電極およびドレイン電極のそれぞれに対応して電子供給層に設けられたトレンチと、を有し、トレンチの底面が電子走行層と電子供給層の界面であるヘテロ接合から所定の距離だけ離れている構成である。

(もっと読む)

相補型半導体装置とその製造方法

【課題】 マルチゲートMISFETからなる高移動度のnFET及びpFETの双方の移動度を向上させる相補型半導体装置とその製造方法を提供する。

【解決手段】

基板10上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された相補型半導体装置であって、nチャネルMISトランジスタ及びpチャネルMISトランジスタが、基板10の主面に平行な面内に引っ張り歪みを有する第一の半導体層と圧縮歪みを有する第二の半導体層とが交互に積層され、基板10の主面に対して突出した積層構造と、積層構造の対向する両側面を覆うように形成されたゲート絶縁膜80と、ゲート絶縁膜80を介して前記積層構造を覆って形成されたゲート電極30と、ゲート絶縁膜80とゲート電極30をはさんで対向し、積層構造の両端に形成されたソース/ドレイン領域20と、を有することを特徴とする相補型半導体装置。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御でき、短チャネル効果を効果的に抑制できる半導体装置を提供する。

【解決手段】シリコン基板1と接してショットキー接合を形成するソース領域10,ドレイン領域11と、上記シリコン基板1とソース領域10との境界が露出する部分およびシリコン基板1とドレイン領域11との境界が露出する部分を被覆するように設けられた絶縁層を備える。上記絶縁層は、シリコン基板1とソース領域10との境界およびシリコン基板1とドレイン領域11との境界を跨ぐように、シリコン基板1とソース領域10に接すると共にシリコン基板1とドレイン領域11に接する固定電荷を含む領域8を有する。上記固定電荷は、熱平衡状態において荷電している。

(もっと読む)

半導体装置及びその製造方法

【課題】配線層間の正常な電気的導通が取れている半導体装置を提供することを課題とする。

【解決手段】基板上又は基板の表面層に少なくとも2層の配線層を備え、前記2層の配線層の内、下層配線層がシリコンからなる際に、前記下層配線層と上層配線層間に炭化珪素層を備えたことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスにおいてフォトレジスト構造等の追加工程を必要としない、非対称なDSS構造の半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2上にゲート絶縁膜21を介して形成されたゲート電極22と、ゲート電極22の側面に形成されたオフセットスペーサ13、23と、一方のオフセットスペーサ23の側面に形成されたゲート側壁27と、半導体基板2中のゲート絶縁膜21下に形成されたチャネル領域25と、半導体基板2内のチャネル領域25を挟む領域に形成され、チャネル領域25側に導電型不純物が偏析して形成されたエクステンション領域24aを有するソース・ドレイン領域24と、ソース・ドレイン領域24上にオフセットスペーサ13に接して形成されたシリサイド層16、及び、ゲート側壁27に接して形成されたシリサイド層26と、を有した半導体装置1とする。

(もっと読む)

101 - 120 / 542

[ Back to top ]