Fターム[4M104BB22]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | PtSi (542)

Fターム[4M104BB22]に分類される特許

21 - 40 / 542

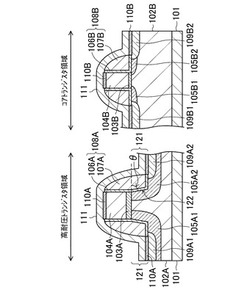

半導体装置及びその製造方法

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

トランジスタ

【課題】耐圧特性に優れた高電子移動度トランジスタ(HEMT)を提供する。

【解決手段】基板12上に形成された複数の活性半導体層16、18を含むHEMT10。ソース電極20、ドレイン電極22、およびゲート24は、複数の活性層16、18と電気的に接触して形成される。スペーサ層26は、複数の活性層16、18の表面の少なくとも一部の上に形成され、ゲート24を覆っている。フィールドプレート30が、スペーサ層26上に形成されて、ソース電極22に電気的に接続され、このフィールドプレート30はHEMT10内の最高動作電界を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

(もっと読む)

窒化ガリウム半導体素子

【課題】高出力の窒化ガリウムショットキー・ダイオード素子を提供する。

【解決手段】1〜6μmの厚さを有するn+型ドープしたGaNダイオードから製造した窒化ガリウムベースの半導体ショットキー・ダイオードをサファイア基板の上に配設する。1μmを超える厚さを有するn−型ドープしたGaNダイオードを、複数の細長形の指にパターン化した前記n+型ドープGaNダイオード上に配設し、金属層をn−型ドープGaN層上に配設し、それとの間にショットキー接合を形成する。細長形の指の層厚、長さおよび幅は、降伏電圧が500Vを超え、電流容量が1アンペアを超え、かつ順方向電圧が3V未満である素子を得るように最適化される。

(もっと読む)

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことが可能な半導体装置、および半導体装置の製造方法を提供する。

【解決手段】サリサイド構造の半導体装置の高濃度ソース・ドレイン領域とゲート電極表面に形成される金属シリサイドを複数のアイランド状金属シリサイドからなる構成とする。これにより、全面に形成された金属シリサイド層よりも、シリコンと金属シリサイド層間の応力を緩和することができ、シリコンと金属シリサイド層間の応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことができる。

(もっと読む)

半導体整流装置

【課題】小数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1および第2の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

(もっと読む)

半導体整流装置

【課題】少数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1の半導体領域に挟まれ、接合深さが第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、第1、第2および第3の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

(もっと読む)

炭化ケイ素パワーデバイスを有する半導体ウェハを処理する方法

【課題】

ドーパントが注入されたSiC基板がオーミックコンタクトの形成前に薄くされる場合には、オーミックコンタクトを形成するために堆積された金属は、基板上に堆積されたときにオーム特性を持たないことがある。

【解決手段】

炭化ケイ素半導体デバイスを形成する方法は、第1の厚さを有する炭化ケイ素基板の第1の表面に半導体デバイスを形成するステップと、前記第1の表面にキャリア基板を取り付けるステップとを含む。さらに、前記炭化ケイ素基板を、前記第1の厚さ未満の厚さまで薄くするステップ、前記第1の表面とは反対側の前記薄くされた炭化ケイ素基板の表面に金属層を形成するステップ、前記金属層を局所的にアニールするステップを含む。前記炭化ケイ素基板は、個片化された半導体デバイスを提供するために、個片化される。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】簡単な工程でニッケル含有シリサイドを形成する。

【解決手段】シリコン基板を用いた場合であって、ゲート絶縁膜、ゲート電極、ゲート電極側面のサイドウォールを形成し、不純物イオンをドープしてソース領域及びドレイン領域を形成し、表面酸化膜を除去し、シリコン基板を450℃以上に加熱しながら、ニッケル含有膜を10nm〜100nmの膜厚で形成することにより、ソース領域、ドレイン領域、及びゲート電極上にニッケル含有シリサイドを形成することができる。その後、未反応のニッケルを除去する。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

21 - 40 / 542

[ Back to top ]