Fターム[4M104BB35]の内容

Fターム[4M104BB35]に分類される特許

21 - 40 / 40

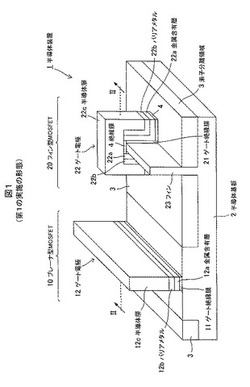

半導体装置

【課題】それぞれが適した閾値を有するフィン型MOSFETとプレーナ型MOSFETが混載され、且つ少ない工程で製造することができる半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、第1のゲート電極と、前記第1のゲート電極にフェルミレベルピニングを発生させない第1のゲート絶縁膜と、を有するプレーナ型MOSFETと、第2のゲート電極と、前記第2のゲート電極にフェルミレベルピニングを発生させる第2のゲート絶縁膜と、を有するフィン型MOSFETと、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】対称フラットバンド電圧、同一ゲート電極材料かつ高誘電率誘電体層を有するCMISFETを提供する。

【解決手段】nMISFETは、半導体基板10の表面上に配置された第1ゲート絶縁膜16と、第1ゲート絶縁膜16上に配置されたM1xM2yO(M1=Y,La,Ce,Pr,Nd,Sm,Gd,Tb,Dy,Ho,Er,Tm,YbまたはLu,M2=Hf,Zr,Ta,x/(x+y)>0.12)で表される組成比を有する第1金属酸化物層20と、第2金属酸化物層24と、第2金属酸化物層24上に配置された第1導電層28とを備え、pMISFETは、半導体基板10表面上に配置された第2ゲート絶縁膜18と、第2ゲート絶縁膜18上に配置されたM3zM4wO(M3=Al,M4=Hf,Zr,Ta,z/(z+w)>0.14)で表される組成比を有する第3金属酸化物層22と、第4金属酸化物層26と、第4金属酸化物層26上に配置された第2導電層30とを備える半導体装置およびその製法。

(もっと読む)

半導体装置およびその製造方法

【課題】従来のCMISデバイスにおいては、価電子帯端近くの高い仕事関数を有する金属は、還元雰囲気アニール後に実効仕事関数が低下する。

【解決手段】半導体装置は、ソースとドレイン間のN型半導体層上に形成された金属元素を含むゲート絶縁膜と、ゲート絶縁膜上に形成され、膜厚が3nm以下であるカーボン層と、カーボン層上に形成されたゲート電極とを有し、ゲート電極/ゲート絶縁膜界面へのカーボン層による仕事関数の上昇効果により、還元雰囲気アニール耐性のない価電子帯端近くの高い仕事関数を有する金属を用いずとも、PMISFETに必要な実効仕事関数を得ることができ、低い閾値電圧を実現する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極層の除去に伴うトランジスタの性能の低下を抑制すること。

【解決手段】第1及び第2導電型のトランジスタをそれぞれ基板上の第1及び第2領域に形成する半導体装置の製造方法であって、前記第1及び第2領域にわたってゲート絶縁膜と犠牲層とを堆積し、前記第1領域から前記犠牲層を除去し、前記第1領域に露出した前記ゲート絶縁膜上及び前記第2領域に残存する前記犠牲層上に第1のゲート電極層を堆積し、前記第2領域から前記第1のゲート電極層と前記犠牲層とを除去し、前記第2領域に露出した前記ゲート絶縁膜上に第2のゲート電極層を堆積し、前記ゲート絶縁膜と前記第1のゲート電極層とを含む前記第1導電型のトランジスタを形成し、前記ゲート絶縁膜と前記第2のゲート電極層とを含む前記第2導電型のトランジスタを形成することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜上にpMOS電極材料として金属電極を形成する際に金属膜中からゲート絶縁膜へ拡散する炭素成分を抑制し、固定電荷要因を下げることができる半導体装置及びその製造方法を提供することである。

【解決手段】半導体装置の製造方法は、半導体基板100上にゲート絶縁膜101を形成する工程と、ゲート絶縁膜上に薄いシリコン層102を形成する工程と、この薄いシリコン層上にゲート絶縁膜界面での仕事関数が所定範囲内の値となる金属膜103を形成する工程と、を備えたものである。

(もっと読む)

半導体装置

【課題】ランタンアルミニウム酸化物を絶縁膜として用いた半導体装置において、この絶縁膜に積層する電極として必要な特性を満たすと共に、各種半導体装置製造過程を経てもその絶縁膜特性を劣化させることのないゲート電極を見出し、微細化に対応可能なスタック構造を有する半導体装置を提供する。

【解決手段】本発明の一実施形態に係るCMOS回路は、nMISは、ランタンアルミニウム酸化物を用いたゲート絶縁膜19、LaxAl1−x(但し0.21≦x≦0.33)で表されるランタンアルミニウム合金を用いたゲート電極21、及びソース及びドレイン領域35とを具備し、pMISは、ランタンアルミニウム酸化物を用いたゲート絶縁膜19、LaxAl1−xNyHz(但し0.21≦x≦0.33、0.15≦y≦0.5、0≦z≦0.1)で表されるランタンアルミニウム合金を用いたゲート電極21を具備する。

(もっと読む)

半導体装置の製造方法

【課題】P型MOSFETの閾値のバラつきを抑制して高品質の半導体装置を形成することができ、また、製品開発のコストを抑制することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板上100にゲート絶縁膜102を形成する第1の工程と、ゲート絶縁膜102上に、ゲート電極104を構成する導電体膜103を、有機材料を用いた形成法によって形成する第2の工程と、導電体膜103が形成されたシリコン基板100を、酸化性雰囲気である水蒸気と、還元性雰囲気である水素との混合雰囲気中で加熱する第3の工程と、を備えた半導体装置の製造方法であって、第3の工程における水蒸気に対する水素の分圧比が、炭素が酸化され、かつ、導電体膜104を構成する金属材料が還元される分圧であることを特徴とする。

(もっと読む)

薄膜トランジスタ装置およびその製造方法、ならびに、該薄膜トランジスタ装置を備えた表示装置

【課題】 TFTの層間絶縁膜の下層にあって膜厚が薄いポリシリコン膜からなるソース領域やドレイン領域に到達するコンタクトホールを開口する際に、ポリシリコン膜を突き抜けてしまうとコンタクトホール底部にポリシリコン膜が残存しないため、接続抵抗が増大してしまう。また、保持容量の下部電極がポリシリコン膜からなる場合、該膜を低抵抗化するために高ドーズのドーピングプロセスが必要であるため、生産性を著しく低下させていた。

【解決手段】 基板1上で島状に形成されたポリシリコン膜3におけるソース領域3aおよびドレイン領域3bの少なくとも一部を覆う金属膜4を形成してから、ゲート絶縁膜5、ゲート電極6、層間絶縁膜7を形成し、金属膜4の上部にコンタクトホール8を開口する。さらに、金属膜4を形成する際に、保持容量の位置まで延在させることにより、金属膜4を保持容量の下部電極となす。

(もっと読む)

半導体装置およびその製造方法

【課題】 nMISおよびpMIS形成領域の高誘電率ゲート絶縁膜上に設けられたデュアルメタルゲート電極の仕事関数の変化を抑制して、信頼性の高い半導体装置を製造する方法を提供する。

【解決手段】 単結晶シリコン基板100のnMISおよびpMIS形成領域に高誘電率ゲート絶縁膜102を形成し、ゲート絶縁膜102上にシリコンおよびゲルマニウムを含まない第一の金属膜103を形成し、pMIS形成領域のゲート絶縁膜上に第一の金属膜103を残して、nMIS形成領域の第一の金属膜103を除去する。次に、nMIS形成領域のゲート絶縁膜102および第一の金属膜103上にシリコンまたはゲルマニウムを含む第二の金属膜104を形成し、第一および第二の金属膜103、104を加工してゲート電極Gn、Gpをそれぞれ形成する。また、第一の金属膜103と第二の金属膜104に含まれる主の金属元素は周期律表における同族金属元素とする。

(もっと読む)

電極の破壊電圧を抑制するためのダイヤモンド電極構造を備えたデバイス及びその製造方法

【課題】絶縁破壊電界が高く、熱伝導率が極めて良好で放熱性に優れ、化学的にも安定であり、またバンドギャップが大きいというダイヤモンド半導体の特性を最大限に活用するために、ダイヤモンドデバイスの電界集中による電極の破壊電圧を抑制するためのダイヤモンド電極構造を備えたデバイス及びその製造方法を提供する。

【解決手段】半導体ダイヤモンドの表面と電極の表面が同一面となるように、半導体ダイヤモンドに設けた溝に電極が埋め込まれた構造を有することを特徴とするダイヤモンドデバイスの電界集中による電極の破壊電圧を抑制するためのダイヤモンド電極構造を備えたデバイス。

(もっと読む)

圧電素子、液滴吐出ヘッド、液滴吐出装置

【課題】良好な電極能を有しつつ低コストで、且つ圧電体に対する充分な吸着性を有する圧電素子、及びそれを備える液滴吐出ヘッドを提供することを目的とする。

【解決手段】共通電極46(下部電極)、圧電体48、及び信号電極50(上部電極)がこの順で積層して構成された圧電素子34において、共通電極46及び/又は信号電極50の構成層の少なくとも1層として、Ta,V,Nb,Mo,W,Ti,Zr,及びHfの金属、前記金属の元素を1種以上含む合金、前記金属の元素を1種以上含む窒化物、前記金属の元素を1種以上含む珪化物、並びに、前記金属の元素を1種以上含む硼化物から選択される少なくとも1種で構成される電気伝導層の少なくとも1層を適用する。これにより、良好な電極能を有しつつ低コストで、且つ剥がれ難い電極を持つ圧電素子34となる。

(もっと読む)

半導体装置及びその製造方法

【課題】 2種類以上の電源電圧に対応するように複数のMOSFETを同一半導体基板上に混載する半導体装置において、微細化を進めても高性能を維持することが可能なゲート構造を提供する。

【解決手段】 半導体基板1に形成され、高誘電体材料を用いたゲート絶縁膜9を備えたMOSFETと高誘電体材料を含まないゲート絶縁膜10を備えたMOSFETを有し前記高誘電体材料を用いたゲート絶縁膜を備えたMOSFETのゲート電極がシリサイドもしくは金属で構成され、前記高誘電体材料を含まないゲート絶縁膜を備えたMOSFETのゲート電極が多結晶又は非晶質シリコンもしくはシリコンゲルマニウムから構成されている。1つの半導体基板に混載された低電圧動作MOSFET及び高電圧動作MOSFETの各々に最適なゲート電極を提供することが可能となり微細化を進めて素子性能低下を避ける。

(もっと読む)

半導体装置およびその製造方法

【課題】 簡便な方法で製造することができ、しきい値電圧が適正な範囲に設定された半導体装置を提供する。

【解決手段】 第一の発明の半導体装置は、相補型であり、半導体基板、p型半導体装置およびn型半導体装置を具備する。p型半導体装置は、半導体基板上のn型半導体層と、n型半導体層上面に形成され、n型半導体層上面から下方に向けてp型ドーパントが補誤差関数で分布するp型ドーパント拡散領域と、p型ドーパント拡散領域上に形成され、Hfを含む第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成され、p型半導体化合物を有する第1のゲート電極と、p型ドーパント拡散領域をゲート長方向に挟み、p型ドーパント拡散領域に比して深くn型半導体層上面に形成された第1のソース・ドレイン領域と、を備えることを特徴とする。

(もっと読む)

CMOS半導体装置

【課題】

従来のメタルゲート技術では、nMOSFET及びpMOSFETのゲート電極が異なる金属で形成さ

れ、製造プロセスが複雑化するという問題があった。本発明では、nMOSFETとpMOSFETで同

一のメタルゲート有し、集積化容易なCMOS半導体装置を提供する。

【解決手段】

nMOSFET、pMOSFETから形成される半導体装置において、nMOSFET、pMOSFETの前記金属ゲ

ート電極は、Ti、Zr、Hf、Ta及びLa等の希土類金属元素、もしくはこれら金属のボライド

、シリサイド、ジャーマナイド化合物のいずれか一つの同一の金属材料からなり、nMOSFE

T及びpMOSFETの前記絶縁膜の少なくとも金属電極側は異なる絶縁膜材料としたことを特徴

とする。

(もっと読む)

不動態化された金属層を形成する方法及びシステム

後に酸素含有環境に晒されるときに下地の金属層の特性及び形態を維持する不動態化された金属層を形成する方法が提供される。当該方法は、処理チャンバー(1)内に基板(50、302、403、510)を設置する工程、化学的気相堆積法にて基板(50、302、403、510)上にレニウム金属層(304、408、580)を堆積するために、レニウム−カルボニル前駆体を含有する処理ガスに基板(50、302、403、510)を晒す工程、及びレニウム金属表面でのレニウム含有ノジュール(306)の酸素誘起成長を抑制するために、レニウム金属層(304、408、580)上にパッシベーション層(414、590)を形成する工程を有する。  (もっと読む)

(もっと読む)

バリア膜の形成方法

【課題】低温プロセスで、アスペクト比の高い微細なホール、トレンチ等の上部でオーバーハングが発生することなく、カバレージ良くZrB2膜等のバリア膜を形成する方法の提供。

【解決手段】基板を50〜450℃に加熱し、Zr(BH4)4ガスを0.1〜10秒の間、0.5〜200sccmの流量で導入し、真空チャンバー内の圧力がZr(BH4)4の導入時の圧力に比べ1/5以下になった時点で原料の吸着工程を終了し、チャンバー内へ触媒室で励起されたH2ガス及び/又はNH3ガスからなる反応ガスを0.1〜10秒の間、20〜1000sccmの流量で導入し、チャンバー内の圧力が、反応ガス導入時の圧力に比べ1/5以下になった時点で反応工程を終了させて、バリア膜を得る。

(もっと読む)

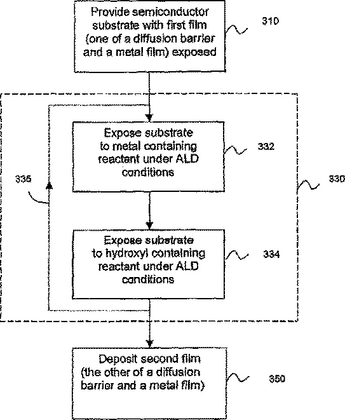

酸素架橋構造及び方法

拡散バリア膜と金属膜との間の接着性を改善するための方法が提唱される。拡散バリア膜及び金属膜の両方は、いずれかのシークエンスで、半導体基板上へ堆積される。拡散バリア膜又は金属膜のいずれか一方である第一膜(第一膜は、基板の表面領域の少なくとも一部で暴露される)を有する基板は、酸素含有リアクタントに暴露され、第一膜の露出部分に酸素含有基又は酸素原子の約1の単層の表面終端を生成する。次いで、第二膜(これは、拡散バリア膜及び金属膜のうち他方である)が基板上に堆積される。さらに、酸素架橋構造が提唱され、該構造は、拡散バリア膜及び該拡散バリア膜との界面を有する金属膜を含む(ここで、界面は、酸素原子の単層を含有する)。

【課題】

【解決手段】  (もっと読む)

(もっと読む)

真空成膜装置

【課題】 吸着及び反応工程のプロセス条件を独立して設定でき、膜質のよい薄膜を得ることができ、成膜プロセスのサイクルタイムを早くできるように構成され、その上、製作コストの低い成膜装置の提供。

【解決手段】 基板ステージと、ベルジャー形容器と、成膜対象物搬送手段と、ガス導入手段とを備え、成膜プロセス実施時に、基板ステージと容器とで真空チャンバーを形成し、真空チャンバーの空間内にガス導入手段を介して原料ガス、反応ガスが導入され、成膜対象物上に原料ガスを吸着させる吸着工程及び吸着された原料ガスと反応ガスとを反応させる反応工程のいずれかを行うことができるように構成してなる。

(もっと読む)

金属からなるゲート電極を形成するための方法

一の実施形態では、ゲート誘電体層(18)を基板(10)の上に形成し、次に第1金属層(26)を、ゲート誘電体層(18)の内、第1素子タイプが形成される予定の部分の上に選択的に堆積させる。第1金属層(26)とは異なる第2金属層(28)は、ゲート誘電体層(18)の内、第2素子タイプが形成される予定の露出部分の上に選択的に形成される。第1及び第2素子タイプの各々は異なる仕事関数を有することになる、というのは、第1及び第2素子タイプの各々が、ゲート誘電体と直接コンタクトする異なる金属を含むことになるからである。一の実施形態では、第1金属層(26)の選択的堆積は、ALDにより、かつ阻止層(24)を使用することにより行なわれ、阻止層は、第1金属層(26)を、ゲート誘電体層(18)の内、阻止層(24)によって覆われない部分の上にのみ選択的に堆積させることができるようにゲート誘電体層(18)の上に選択的に形成される。 (もっと読む)

バリヤ物質の原子層堆積

1以上の物質層のバリヤ層を原子層堆積により堆積させるために基板を処理する方法が提供される。一態様においては、金属含有化合物の1以上のパルスと窒素含有化合物の1以上のパルスを交互に導入することにより基板表面の少なくとも一部上に金属窒化物バリヤ層を堆積させるステップと、金属含有化合物の1以上のパルスと還元剤の1以上のパルスを交互に導入することにより金属窒化物バリヤ層の少なくとも一部上に金属バリヤ層を堆積させるステップとを含む基板を処理する方法が提供される。金属窒化物バリヤ層及び/又は金属バリヤ層の堆積前に基板表面上で浸漬プロセスが行われてもよい。 (もっと読む)

21 - 40 / 40

[ Back to top ]