Fターム[4M104BB40]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 不純物を含むもの(上層部を含む) (1,693) | n型、p型不純物 (963)

Fターム[4M104BB40]に分類される特許

201 - 220 / 963

半導体装置及び半導体装置の製造方法

【課題】微細化が進んだトランジスタにおいて、他の問題を生じさせずに抵抗を低減する。

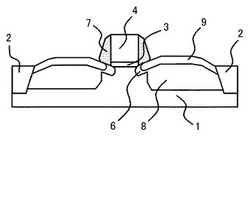

【解決手段】シリサイド層9は、ソース・ドレイン領域8の表層及びソース・ドレイン拡張領域6に形成されている。シリサイド層9は、半導体基板1に垂直かつゲート幅方向に対して平行な断面でみたときに、ソース・ドレイン領域8の中央部からチャネル領域に近づくにつれて半導体基板1の内側(図中下側)に近づいており、かつチャネル領域側の端部がソース・ドレイン拡張領域6に延在している。

(もっと読む)

ドープされたシリコン層の製造方法、該方法によって得られるシリコン層およびその使用

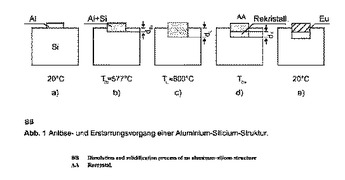

本発明は、基板上のドープされたシリコン層の製造方法であって、次の工程(a)液体シラン配合物および基板の準備、(b)該基板に該液体シラン配合物を塗布、(c)電磁エネルギーおよび/または熱エネルギーの導入、(d)少なくとも1種の、アルミニウムを含有する金属錯体化合物を有する液体調製物の準備、(e)前記工程(c)によって得られたシリコン層に該調製物を塗布、そして引き続き(f)電磁エネルギーおよび/または熱エネルギーの導入によって、前記工程(e)によって得られた被覆の加熱、そして引き続き(g)前記工程(f)によって得られた被覆の冷却、を含むドープされたシリコン層の製造方法、該法によって得られるドープされたシリコン層ならびに感光性素子および電子素子を製造するための該シリコン層の使用に関する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】デュアルメタルゲートプロセスを用いることなく、p型MISトランジスタ及びn型MISトランジスタ双方の特性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型半導体領域10Aの上に順次形成された第1の界面シリコン酸化膜105、アルミニウムを含む第1のゲート絶縁膜106A及び第1のゲート電極119Aと、n型半導体領域10Bの上に順次形成された第2の界面シリコン酸化膜105、実効仕事関数を低下させる効果を有する元素を含む第2のゲート絶縁膜106B及び第2のゲート電極119Aとを備えている。第1のゲート絶縁膜106Aの上部におけるアルミニウムの濃度は、1×1020/cm3以上である。第2のゲート絶縁膜106Bの上部におけるアルミニウムの濃度は、1×1019/cm3以下である。第1の界面シリコン酸化膜105の膜厚と第2の界面シリコン酸化膜105の膜厚との差は0.2nm以下である。

(もっと読む)

半導体装置の製造方法

【課題】p型MISトランジスタ及びn型MISトランジスタの特性を向上した相補型MISトランジスタを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、p型半導体領域10A及びn型半導体領域10Bを有する半導体基板101の上に、高誘電率膜106、アルミニウムからなる第1のキャップ膜107及びハードマスク108を順次形成する。次に、第1のキャップ膜107及びハードマスク108におけるn型半導体領域10Bの上に形成された部分を除去する。その後、半導体基板101の上に、実効仕事関数を低下させる効果を有する元素を含む第2のキャップ膜109を形成する。

(もっと読む)

薄膜トランジスタ、発光装置、電子機器、及び、薄膜トランジスタの形成方法

【課題】ソース−ドレイン間等の電圧−電流特性を改善することができる薄膜トランジスタ、発光装置、電子機器、及び、薄膜トランジスタの形成方法を提供する。

【解決手段】薄膜トランジスタ100は、半導体膜119と、半導体膜119の上方に形成されたソース電極層140と、半導体膜119の上方に形成されたドレイン電極層142と、ソース電極層140とドレイン電極層142との間、かつ、半導体膜119の上方に形成されたチャネル保護膜113と、を備える薄膜トランジスタであって、ソース電極層140とドレイン電極層142の少なくとも何れか一方は、チャネル保護膜113と接し、その上面がチャネル保護膜113の上面を超えない接触領域を有して、チャネル保護膜113の上面と重なっていない。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

半導体素子

LDMOS(横方向拡散金属酸化物半導体)構造は、ソースを基板及びゲートシールドへと接続させ、この際、このような接点のためにより小さな面積が用いられる。前記構造は、導電性基板層と、ソースと、ドレイン接点とを含む。少なくとも1つの介在層により、前記ドレイン接点が前記基板層から分離される。導電性のトレンチ状のフィードスルー要素が前記介在層を通過し、前記基板及び前記ソースと接触することで、前記ドレイン接点及び前記基板層を電気的に接続する。 (もっと読む)

半導体装置の製造方法

【課題】n型SiC領域とp型SiC領域との両方と接触可能であり、かつ酸化による接触抵抗の増加を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、炭化珪素からなるn−SiC層12を準備する工程と、n−SiC層12の主表面上にソースコンタクト電極16を形成する工程とを備えるMOSFET1の製造方法である。ソースコンタクト電極16を形成する工程は、ソースコンタクト電極16となるべき導電体層をn−SiC層12の主表面上に形成する工程と、導電体層をソースコンタクト電極16とするため熱処理する工程とを含む。熱処理する工程の後、ソースコンタクト電極16の表面を酸素含有雰囲気に曝露するときのソースコンタクト電極16の温度を100℃以下にする。ソースコンタクト電極16を形成する工程の後、表面電極パッド27を形成する工程の前に、上記ソースコンタクト電極16の一方の主面上に形成された高抵抗層を除去する工程を含むことがより好ましい。

(もっと読む)

半導体装置の製造方法

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置

【目的】ラッチアップ耐量が高く、低抵抗な縦型半導体装置を提供する。

【解決手段】n型ソース領域4の上面にp型第1ベース領域2aおよびp型第2ベース領域2bが形成され、該n型ソース領域4の下面にソース電極5が設けられ、p型第2ベース領域2bの上面に絶縁膜を介してドレイン電極9が形成されている。該p型第2ベース領域2bの上面にはゲート電極用トレンチと、該第1ベース領域2aと第2ベース領域2bおよびn型ソース領域4を短絡する短絡用トレンチが並設されている。該ゲート電極用トレンチの側壁にはn型ドリフト領域6とn型ドレイン領域8がRESURF状に形成され、短絡用トレンチには短絡用導電体12が形成されて該導電体12は該ドレイン電極9と絶縁されている。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置の製造方法を提供することにある。

【解決手段】側壁にサイドウォール絶縁膜が形成されたゲート配線20を形成する工程と、第1の応力膜38を形成する工程と、第1の応力膜上にエッチングストッパ膜40を形成する工程と、エッチングストッパ膜をエッチングし、第1の応力膜のうちのサイドウォール絶縁膜を覆う部分上にエッチングストッパ膜を選択的に残存させる工程と、第2の領域4を露出する第1のマスクを用いて第2の領域内の第1の応力膜をエッチングする工程と、第2の応力膜42を形成する工程と、第1の領域2を露出する第2のマスクを用いて第1の領域内の第2の応力膜をエッチングする工程と、第1の領域と第2の領域との境界部におけるゲート配線に達するコンタクトホール46aを形成する工程とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】フィンの下部に適切に不純物が導入された半導体装置及びその製造方法を提供する。

【解決手段】半導体装置としてのFinFET1は、基体としての半導体基板10と、半導体基板10上に形成された複数のフィン20とを有し、複数のフィン20は、第1の間隔と第1の間隔よりも間隔が狭い第2の間隔とを繰り返して形成され、第1の間隔を形成する側に面した第1の側面221の下部の不純物濃度が、第2の間隔を形成する側に面した第2の側面222の下部の不純物濃度よりも高い半導体領域を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗の低い半導体装置およびその製造方法を提供する。

【解決手段】複数の層を有する半導体層37の第1の面37aに形成されたソース電極12およびゲート取り出し電極14と、第1の面37aと対向する第2の面37bに形成されたドレイン電極16と、ソース電極12上に分散して形成された複数の第1柱状電極13と、ゲート取り出し電極14上に形成された第2柱状電極15と、ドレイン電極16上に分散して形成された複数の第3柱状電極17と、複数の第1柱状電極13の間、および第2柱状電極15と隣接する第1柱状電極13との間を埋めて、ソース電極12、ゲート取り出し電極14、および半導体層37を覆う第1樹脂層18と、複数の第3柱状電極17の間を埋めて、ドレイン電極16を覆い、第1樹脂層18に連接した第2樹脂層19と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】溝側面に側壁膜を形成する際に、側壁膜表面にエッチングダメージを受けることなく、側壁膜上面の溝開口部からの深さのばらつきを抑制して形成可能な方法を提供する。

【解決手段】半導体基板主表面に形成された溝の側壁に第1の層を形成する工程、溝を保護膜で埋設する工程、保護膜の表面の高さが溝の開口部よりも低い位置になるようにドライエッチング法でエッチバックし、該エッチバックにより露出した第1の層をエッチング除去する工程、とを含む半導体装置の製造方法。

(もっと読む)

有機FETアレイ

【課題】pチャネルとnチャネルに共通の有機半導体層とソース、ドレイン電極材料の好適な組合せにより、実用上十分に良好な伝達特性を得ることが可能な有機FETアレイを提供する。

【解決手段】有機半導体層を用いたpチャネル電界効果トランジスタ(p型有機FET)と、有機半導体層を用いたnチャネル電界効果トランジスタ(n型有機FET)とを備えた有機FETアレイ。有機半導体層5はpチャネルとnチャネルに共通の材料の有機半導体単結晶により形成される。p型有機FETのソース及びドレイン電極は、仕事関数に基づいて制御される有機半導体層中の多数キャリアが正孔になるように選択されたpチャネル金属電極6により形成され、n型有機FETのソース及びドレイン電極は、仕事関数に基づいて制御される有機半導体層中の多数キャリアが電子になるように選択されたnチャネル金属電極7により形成される。

(もっと読む)

半導体装置の製造方法

【課題】外部から印加される電源電圧の仕様に対応した、半導体装置の製造方法を提供する。

【解決手段】チャネルイオン注入工程、ゲート酸化膜形成工程、および、ゲート電極パターニング工程の少なくとも1つの工程を、外部から第1の電源電圧が供給されて動作する第1の半導体装置を製造する場合には第1の電源電圧で動作する素子を形成する工程で行い、外部から第2の電源電圧が供給されて動作する第2の半導体装置を製造する場合には第2の電源電圧で動作する素子を形成する工程で行い、また、第1の半導体装置の製造の場合と第2の半導体装置の製造の場合とで少なくとも拡散領域形成工程を共通に行うものである。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体ゲート絶縁膜/メタルゲート電極のMOSトランジスタ構造において、メタルゲート電極側壁の酸化層を抑制し、トランジスタ駆動能力を改善する。

【解決手段】基板101上に、金属含有膜110を形成する工程(a)と、反応室内において金属含有膜にアンモニアラジカルを曝露する工程(b)と、反応室内に不活性ガスを供給し、工程(b)において生じたガスを排気する工程(c)と、工程(b)及び工程(c)を所定の回数繰り返した後に、大気曝露することなく、反応室内において金属含有膜110を覆うシリコン窒化膜100aを形成する工程(d)とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート構造としてメタル電極/High−k膜構造を用いた半導体装置において、仕事関数の制御とEOTの薄膜化とを両立させる。

【解決手段】半導体基板101におけるnチャネルMISトランジスタ形成領域の上に、ゲート絶縁膜として、第1の高誘電率絶縁層202、アルミニウム含有層203、ランタン含有層204及び第2の高誘電率絶縁層205を順次形成する。その後、ゲート電極形成を行う。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、通常のコンタクトとシェアードコンタクトとを同時に形成することが難しくなり、接合リーク不良やコンタクト抵抗の上昇が発生する等の課題があった。

【解決手段】ロジックSRAM部のゲート配線6の側壁に形成するサイドウォール9と、拡散層11の表面に形成するシリサイド層13とゲート配線6のシリサイド層15とを電気的に接続するドープトポリシリコン18と、ドープトポリシリコン18と第1層アルミ配線とを電気的に接続するWプラグ26と、ロジックSRAM部の拡散層11の表面のシリサイド層と第1層アルミ配線とを電気的に接続するWプラグ25とを備えるものである。

(もっと読む)

有機発光表示装置及びその製造方法

【課題】酸化物半導体層と多結晶シリコン半導体層を共に用い得る有機発光表示装置及びその製造方法を提供する。

【解決手段】基板本体と、基板本体上に形成された第1ゲート電極及び第2半導体層と、第1ゲート電極及び第2半導体層の上に形成されたゲート絶縁膜と、ゲート絶縁膜を介在して第1ゲート電極及び第2半導体層上にそれぞれ形成された第1半導体層及び第2ゲート電極と、第1半導体層と少なくとも一部が相接して重畳した複数のエッチングストッパ層と、複数のエッチングストッパ層をそれぞれ露出する複数のコンタクトホールを有し、第1半導体層及び第2ゲート電極上に形成された層間絶縁膜と、層間絶縁膜上に形成され、複数のエッチングストッパ層を通じて第1半導体層とそれぞれ直接的/間接的に接続された第1ソース電極及び第1ドレイン電極と、層間絶縁膜上に形成され、第2半導体層と接続された第2ソース電極及び第2ドレイン電極とを含む。

(もっと読む)

201 - 220 / 963

[ Back to top ]