Fターム[4M104BB40]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 不純物を含むもの(上層部を含む) (1,693) | n型、p型不純物 (963)

Fターム[4M104BB40]に分類される特許

121 - 140 / 963

トレンチゲート型トランジスタの製造方法

【課題】トレンチゲート型トランジスタの製造方法において、ゲート容量の低減、結晶欠陥の発生の抑止、及びゲート耐圧の向上を図る。

【解決手段】N−型半導体層12の表面にトレンチ14を形成し、該表面とトレンチ14内に、熱酸化によりシリコン酸化膜15Aを形成し、これを覆うホトレジスト補強膜16、及びホトレジスト補強膜16を覆うホトレジスト層R2を形成する。そしてホトレジスト層R2及びホトレジスト補強膜16をエッチバックしてトレンチ14内にのみに残す。このホトレジスト層R2及びホトレジスト補強膜16をマスクとして、トレンチ14の側壁の上方のシリコン酸化膜15Aをエッチングして除去する。上記マスクを除去した後、熱酸化により、トレンチ14の側壁の上方にシリコン酸化膜15Aより薄いシリコン酸化膜15Bを形成する。その後、シリコン酸化膜15A,15B上にゲート電極18を形成する。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

表示装置及びその作製方法

【課題】デジタル階調と時間階調とを組み合わせた駆動方法において、アドレス期間よりも短いサステイン期間を有する場合にも正常に画像(映像)の表示が可能であり、EL駆動用トランジスタが、劣化によりノーマリーオンとなった場合にも、信号線の電位を変えて動作を補償することの出来る画素を提供することを課題とする。

【解決手段】消去用TFT105のソース領域とドレイン領域とは、一方は電流供給線108に接続され、残る一方はゲート信号線106に接続されている。この構造により、EL駆動用TFT102のしきい値のシフトにより、ノーマリーオンとなった場合にも、ゲート信号線106の電位を変えることで、EL駆動用TFT102が確実に非導通状態となるように、EL駆動用TFT102のゲート・ソース間電圧を変えることを可能とする。

(もっと読む)

有機薄膜トランジスタ及びその製造方法

【課題】大気雰囲気下であっても酸化されにくく、機能的にも劣化しにくい電荷注入層を備えた有機薄膜トランジスタを提供する。

【解決手段】ゲート電極20Aと、第1のソース/ドレイン電極60Aと、第2のソース/ドレイン電極60Bと、前記第1および第2のソース/ドレイン電極と前記ゲート電極との間に設けられる有機半導体層40と、前記第1および第2のソース/ドレイン電極と前記有機半導体層の間において、前記第1および第2のソース/ドレイン電極に接して配置される電荷注入層50とを備える有機薄膜トランジスタ10において、前記電荷注入層は、電荷注入特性を有するイオン性ポリマーを含有する、有機薄膜トランジスタ。

(もっと読む)

半導体装置およびその制御方法

【課題】リカバリ損失の低減が図れ、かつ、ノイズによるセルフターンオンが生じ難い構造の半導体装置を提供する。

【解決手段】ゲート電極8を深さの異なる第1、第2ゲート電極8a、8bを備えたダブルゲート構造とする。このような構造では、第1、第2ゲート電極8a、8bのうちの第1ゲート電極8aのみをオンさせることで、p型ベース領域3に対して反転層を形成しながらも、その反転層がn-型ドリフト層2とn+型不純物領域4とを繋ぐ深さまでは形成されないようにすることができる。この第1ゲート電極8aを過剰キャリア注入抑制ゲートとして機能させる。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体装置の製造方法

【課題】イオン注入で所定の元素をゲート電極に導入して、異なる仕事関数を有するゲート電極のMOSトランジスタを形成する際に、製造工程の増加を抑制して低コストの半導体装置を提供する。

【解決手段】半導体装置の製造方法では、導電膜上5a,5bにおいて、第1の領域1aから第2の領域1bまでを覆う第1のマスク6b、第2の領域の上方にスペース部7b、及び第2の領域1bから第3の領域1cまでを覆う第2のマスク6cを有するマスクパターンを設ける。スペース部内、並びに第1及び第2のマスクの第1の側面にサイドウォール膜7aを設ける。第1の側面に接するサイドウォール膜の下に位置する導電膜の領域内に不純物を注入する。サイドウォール膜をマスクに用いて異方性エッチングを行うことによりゲート絶縁膜及びゲート電極を形成してMOSトランジスタ。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

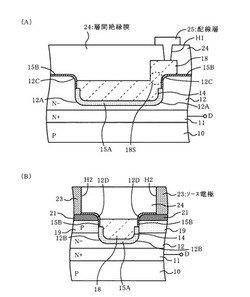

シリコンデバイス構造、及びその形成に用いるスパッタリングターゲット材

【課題】シリコンデバイスの飽和移動度特性を向上する。

【解決手段】シリコン半導体膜上に、Pドープn+型アモルファスシリコン膜と、該Pドープn+型アモルファスシリコン膜上に形成された配線とを有するシリコンデバイス構造において、前記配線が、前記Pドープn+型アモルファスシリコン膜の表面に形成されたシリコン酸化膜と、銅合金膜とからなり、前記銅合金膜は、1原子%以上5原子%以下のMn及び0.05原子%以上1.0原子%以下のPを含む銅合金をスパッタリングにより形成した膜である。

(もっと読む)

半導体装置

【課題】トレンチゲート構成のパワートランジスタを有する半導体装置のオン抵抗を低減する。

【解決手段】トレンチゲート構成のパワーMIS・FETQにおいて、ソース用の半導体領域3の上面の層間絶縁層12の端部(位置P1)と上記ソース用の半導体領域3の上面の上記ゲート電極9Eから遠い端部(溝16の外周の位置P2)との間の長さをaとし、上記層間絶縁層12と上記ソース用の半導体領域3の上面との重なり部の長さ(位置P1から溝5aの外周の位置P3までの長さ)をbとすると、0≦b≦aとする。これにより、ソースパッドSPとソース用の半導体領域3の上面との接触面積が増大する上、ソースパッドSPとチャネル形成用の半導体領域4との距離を短くすることができるので、トレンチゲート構成のパワーMIS・FETQのオン抵抗を下げることができる。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

炭化珪素半導体装置

【課題】微細化してもソース領域およびベース領域に繋がるコンタクト領域とソース電極とのコンタクトが十分に取れるようにする。

【解決手段】コンタクトホール12aの長手方向、つまりソース電極11とn+型ソース領域4およびp+型ボディ層5とのコンタクト領域の長手方向とn+型ソース領域4およびp+型ボディ層5の長手方向も直交させる。これにより、n+型ソース領域4やp+型ボディ層5それぞれのソース電極11へのコンタクト幅をコンタクトホール12aの幅分とすることが可能となる。このため、コンタクトを広く取ることが可能となる。これにより、素子を微細化してもn+型ソース領域4やp型ベース領域3に繋がるp+型ボディ層5とソース電極11とのコンタクトが十分に取れるようにすることが可能となる。

(もっと読む)

薄膜トランジスタ及びこれを用いた表示装置、並びに、薄膜トランジスタの製造方法

【課題】オフ電流を抑制するとともにオン電流を確保することができる薄膜トランジスタを提供する。

【解決手段】基板10と、基板の上方に形成されたゲート電極11及びゲート絶縁膜12と、ゲート絶縁膜を介して配置されたチャネル層13と、チャネル層に接続されたバッファ層14と、バッファ層に接続され、不純物が添加された第1コンタクト層15a(15b)と、第1コンタクト層に接続され、第1コンタクト層よりも不純物濃度が高い第2コンタクト層16a(16b)と、第2コンタクト層に接続されたソース電極17S及びドレイン電極17Dとを備える。ソース電極とドレイン電極との間におけるキャリアの移動経路は、チャネル層、バッファ層、第1コンタクト層及び第2コンタクト層を経由してキャリアが移動する第1経路と、チャネル層及び第2コンタクト層を経由してキャリアが移動する第2経路とを含む。

(もっと読む)

垂直型トランジスタと埋め込みビットラインとを有する半導体メモリ素子及びその製造方法

【課題】垂直型トランジスタのドレイン領域と埋め込みビットラインとの間に抵抗接点(ohmic contact)を形成しつつも、その製造工程が簡単な半導体メモリ素子及びその製造方法を提供すること。

【解決手段】基板に形成されたトレンチによって上部へ突出した形のアクティブ領域と、アクティブ領域の上部に配置される第1の不純物領域と、アクティブ領域の下部に配置される第2の不純物領域と、第1の不純物領域と第2の不純物領域との間のアクティブ領域の側面に沿って配置されるゲート絶縁膜と、ゲート絶縁膜上に配置されるゲート電極膜と、そして、トレンチの下部でライナー膜によって第2の不純物領域と離隔するように配置される金属膜と、金属膜上で前記第2の不純物領域と直接接触されるように配置されるポリシリコン膜とからなる埋め込みビットラインとを備えることを特徴とする。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】異なるチャネル長のトランジスタを有し、かつ、コンタクト抵抗の増加およびオン電流の減少を防止できる半導体装置の提供。

【解決手段】ピラートランジスタTr1と、前記ピラートランジスタTr1の下部拡散層7aへ信号または電源を供給するとともに、ポリシリコン層10aからの固相拡散し、下部拡散層7aを形成することにより、前記ピラートランジスタTr1のチャネル長d1を厚みにより制御する前記ポリシリコン層10aと、を具備してなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

半導体装置、光学装置及びセンサ装置

【課題】ソース電極及びドレイン電極と有機半導体材料層との間の接触抵抗を低下させることができ、これを簡便な製造プロセスで実現できる半導体装置、光学装置及びセンサ装置を提供すること。

【解決手段】ソース電極5と、ドレイン電極6と、少なくともこれらの電極間に設けられた有機半導体材料層7とを有し、有機半導体材料層7を介してソース電極5とドレイン電極6との間で電荷を移動させるように構成された有機電界効果トランジスタにおいて、ソース電極5及びドレイン電極6が、導電性高分子材料と電荷移動錯体との混合物からなる、有機電界効果トランジスタ1a。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

オフセット構造の薄膜トランジスタ

【課題】オフセット構造の薄膜トランジスタを提供する。

【解決手段】ゲート電極と、それぞれゲート電極と一部重畳する第1活性領域及び第2活性領域を備える活性層と、ゲート電極と活性層との間のゲート絶縁膜と、第1活性領域とそれぞれ電気的に連結された第1ソース/ドレイン電極及び第2ソース/ドレイン電極、第2活性領域とそれぞれ電気的に連結された第3ソース/ドレイン電極及び第4ソース/ドレイン電極を備えるソース/ドレイン電極層と、を備えるが、第1ソース/ドレイン電極ないし第4ソース/ドレイン電極のいずれか二つは、ゲート電極と一部重畳し、他の二つは、ゲート電極とオフセットされており、ソース/ドレイン電極の配置は、ソース/ドレイン電極層の中心に対称である薄膜トランジスタである。

(もっと読む)

121 - 140 / 963

[ Back to top ]