Fターム[4M104BB40]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 不純物を含むもの(上層部を含む) (1,693) | n型、p型不純物 (963)

Fターム[4M104BB40]に分類される特許

161 - 180 / 963

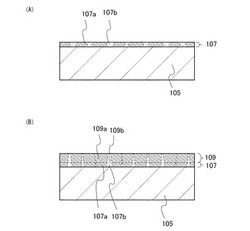

薄膜トランジスタ及びその作製方法

【課題】電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供する。

【解決手段】第1のゲート電極と、第1のゲート電極とチャネル領域を挟んで対向する第2のゲート電極とを有するデュアルゲート型の薄膜トランジスタのチャネル領域の形成方法において、結晶粒の間に非晶質半導体が充填される微結晶半導体膜を形成する第1の条件で第1の微結晶半導体膜を形成した後、結晶成長を促進させる第2の条件で、第1の微結晶半導体膜上に第2の微結晶半導体膜を形成する。

(もっと読む)

トランジスタおよびその製造方法

【課題】高い電流駆動力と高いカットオフ特性を備えたトランジスタおよびその製造方法を提供する。

【解決手段】本発明の一態様に係るトランジスタ100は、導体領域10aと表面に原子が結合した半導体領域10bとを有し、チャネルとして機能するグラフェン膜10と、グラフェン膜10上にゲート絶縁膜11を介して形成されたゲート電極12と、を有し、導体領域10aと半導体領域10bが形成するショットキー接合のトンネル電流をスイッチング動作に用いる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極に注入された不純物に起因するゲートリークを低減させる。

【解決手段】ゲート電極14が形成されたアクティブ領域による被覆率が50%以上かつその面積が0.02mm2以上の領域において、多結晶シリコン膜14´に炭素15を導入してから、多結晶シリコン膜14´にリン16を導入し、多結晶シリコン膜14´をパターニングすることにより、ゲート絶縁膜13上にゲート電極14を形成する。

(もっと読む)

高電圧印加のための改善された終端構造を備えるトレンチDMOSデバイス

Pチャネル型パワーMOSFET

【課題】PチャネルパワーMOSFETにおいて、同手法に従い、トレンチ内にP+ポリシリコンゲート電極とP+フィールドプレート電極を有するトレンチ内ダブルゲート型PチャネルパワーMOSFETを製作して、種々の特性を測定したところ、高温状態で、基板に対してゲートに負のバイアスを印加し続けると、PチャネルパワーMOSFETの閾値電圧の絶対値がストレス印加時間と共に次第に大きくなってゆく現象があることが明らかとなった。

【解決手段】本願の一つの発明は、N型ポリシリコン線状フィールドプレート電極およびN型ポリシリコン線状ゲート電極を各トレンチ部に有するPチャネル型パワーMOSFETである。

(もっと読む)

半導体トランジスタの製造方法

【課題】プロセスの自由度を高めつつ、活性層とオーミックコンタクトをとるオーミック電極を形成できる半導体トランジスタの製造方法を提供する。

【解決手段】GaN系の半導体からなる活性層上に、オーミック電極を形成する半導体トランジスタの製造方法であって、活性層3上に、タンタル窒化物からなる第1の層11と、第1の層11上に積層されたAlからなる第2の層12とを形成する工程と、第1及び第2の層11,12を、520℃以上、600℃以下の温度で熱処理することにより、活性層3とオーミックコンタクトをとるオーミック電極9s,9dを形成する工程とを備える。

(もっと読む)

有機電極を用いた有機薄膜トランジスタとその製造方法

【課題】少なくとも2種類以上の同じ有機化合物を用いてp型、n型両方の有機薄膜トランジスタを作り分けることができ、かつ、有機電極も同時に作製可能となるプロセスアビリティーの高い有機半導体素子およびそれを使った電気回路を提供することにある。さらに、有機電導体、有機超電導体、有機磁性体、有機熱電素子、有機エレクトロクロミック素子、有機エレクトロルミネセンス素子等への応用が可能であること。

【解決手段】少なくとも2種類以上の有機化合物からなる有機電極と、少なくとも1種類以上の有機電極構成成分から選ばれた有機化合物を主成分とする有機半導体活性層から構成された有機半導体素子膜を有する有機薄膜トランジスタ。

(もっと読む)

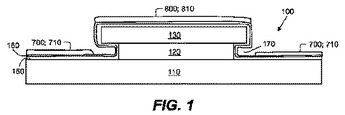

半導体装置及び電子機器

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極またはドレイン電極は、第1の導電層と、第1の導電層の端面よりチャネル長方向に伸長した領域を有する第2の導電層と、を含み、第2の導電層の伸長した領域の上に、前記伸長した領域のチャネル長方向の長さより小さいチャネル長方向の長さの底面を有するサイドウォール絶縁層を有する半導体装置である。

(もっと読む)

パワー素子を備えた半導体装置の製造方法

【課題】電子線照射等の後に行う水素アニール時に水素が十分にデバイスを構成する半導体のダメージ部分まで到達し、ダメージ回復が行えるようにすると共に、表面電極の劣化を抑制することができるようにする。

【解決手段】IGBTが形成されたセル領域全面に形成された表面電極11に含まれるバリアメタル12の第1金属膜12aをチタン(Ti)ではなく、ニッケル(Ni)やコバルト(Co)等のVIII族の金属材料により構成する。これにより、水素アニールの際に、電子線照射等によってダメージを受けたシリコン表面に水素が到達するようにできる。また、バリアメタル12の第1金属膜12aを構成する金属材料が水素と結合しないようにできる。したがって、水素アニール時に水素が十分にシリコン表面のダメージ部分まで到達し、ダメージ回復が行えるようにすることができると共に、表面電極11の劣化を抑制することができる。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】活性層―電極間の寄生抵抗に起因する素子特性のばらつきの少ないIGZO系電界効果型トランジスタを製造する。

【解決手段】基板B上に、IGZO系アモルファス酸化物からなる半導体層11、ソース電極22、ドレイン電極23、ゲート電極21およびゲート絶縁膜31とを備えてなる電界効果型トランジスタ1の製造方法において、半導体層11上にIGZO系アモルファス酸化物層20をスパッタ成膜により成膜し、その後アニール処理を行って、ソース電極22およびドレイン電極23の少なくとも半導体層11に接触する面側を構成する導電層を形成する。スパッタ成膜における背圧は1×10−5Pa未満とし、アニール処理におけるアニール温度を100℃以上、300℃以下とする。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに表示装置

【課題】 ソース・ドレイン電極と半導体膜との接触抵抗を低減し、移動度特性を向上した薄膜トランジスタを提供する。さらに、それを用いた高性能の表示装置を提供する。

【解決手段】 板上に形成されたゲート電極と、前記ゲート電極を覆うようにして前記基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体膜と、少なくとも各々の一部が前記半導体膜上に形成され、ソース電極及びドレイン電極として機能する一対の電極と、を具備する薄膜トランジスタであって、前記半導体膜は、GeあるいはSi及びGeを含有し、前記一対の電極の各々は、ボロンあるいはV族元素を含有する金属膜で形成され、前記一対の電極の各々と前記半導体膜との間に、ジャーマノシリサイドあるいは金属−Ge間化合物が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ソース・ドレイン電極と半導体膜とのコンタクト不良を抑制することが可能な半導体装置等を提供する。

【解決手段】両端部30s、30dの膜厚が平坦部30cの膜厚よりも厚い半導体膜30を形成する。ゲート絶縁膜40は、両端部30s、30dが露出されるように形成される。両端部30s、30dには、ソース・ドレイン電極50s、50dとソース・ドレイン領域とを接続する中間電極50s、50dが形成され、この中間電極50s、50dまで開口するコンタクトホールが形成される。

(もっと読む)

電極構造体及びその製造方法、並びに半導体装置

【課題】精度良く形成された小型化された電極を備えた電極構造体及びその製造方法、並びに半導体装置を提供する。

【解決手段】第1の層間絶縁膜13に、第1の方向に延在する複数の第1の溝16を形成し、第1の溝16の対向する2つの側面及び底面を覆うように第1の導電膜32を形成し、第1の導電膜32が形成された複数の第1の溝16を第1の絶縁膜19で充填し、第1の層間絶縁膜13、第1の絶縁膜19、及び第1の導電膜32の上面に、第2の方向に延在する複数の開口部を有したハードマスク層33を形成し、異方性エッチング法により、複数の開口部から露出された部分の第1の絶縁膜19及び第1の導電膜32を除去することで、第1の溝16に第1の導電膜32よりなる電極を形成すると共に、第1の層間絶縁膜13に第1の溝16と交差する第2の溝17を複数形成し、ハードマスク層33を除去した後、第2の溝17を第2の絶縁膜21で充填する。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

半導体装置

【課題】シリサイドプロセス前にイオン注入を行う半導体装置であって、より確実にMISFETにおけるリーク電流の抑制が図れるものを実現する。

【解決手段】マスク層RMによりPチャネル型MISFETを覆いつつ、Nチャネル型MISFETのN型ソース領域およびN型ドレイン領域に、イオン(F,Si,C,Ge,Ne,Ar,Krのうち少なくとも一種類を含む)を注入する。その後、Nチャネル型MISFETおよびPチャネル型MISFETの各ゲート電極、ソース領域およびドレイン領域にシリサイド化(Ni,Ti,Co,Pd,Pt,Erのうち少なくとも一種類を含む)を行う。これにより、Pチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流を劣化させること無く、Nチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流(基板リーク電流)の抑制が図れる。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程により半導体基板表面がアモルファス化されるため、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に高濃度不純物を含有する導電性膜を設ける。高濃度不純物のイオン注入を行う必要がないことから、この領域の半導体基板表面がアモルファス化することがない。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極及びドレイン電極は、第1の導電層と、第1の導電層の端部よりチャネル長方向に伸長した領域を有する第2の導電層と、を含む半導体装置である。

(もっと読む)

161 - 180 / 963

[ Back to top ]