Fターム[4M104CC05]の内容

半導体の電極 (138,591) | 電極の種類(発明部分) (8,574) | MISゲート電極 (3,643)

Fターム[4M104CC05]に分類される特許

201 - 220 / 3,643

半導体装置

【課題】動作特性に対する信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコンを含む基板7と、前記基板7上に設けられた積層体6と、を有する半導体装置1であって、前記積層体6は、少なくとも前記積層体6の側壁の前記基板側にフッ素を含む抑制領域13を有している。前記抑制領域13は、基板7上に設けられた絶縁膜2の前記側壁側に設けられ、フッ素濃度は、チャネル領域11のフッ素濃度よりも高い。

(もっと読む)

半導体装置およびその製造方法

【課題】より良質なゲート電極を有する半導体装置およびその製造方法を提供することである。

【解決手段】実施形態の半導体装置は、ドレイン層と、前記ドレイン層の上に設けられたドリフト領域と、前記ドリフト領域の上に設けられたベース領域と、前記ベース領域の表面に選択的に設けられたソース領域と、前記ソース領域から前記ベース領域を貫通し、前記ドリフト領域に到達するトレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、前記ドレイン層に接続された第1主電極と、前記ソース領域および前記ベース領域に接続された第2主電極と、を備える。前記ゲート電極は、第1導電層と、前記第1導電層と前記ゲート絶縁膜との間に介在する第2導電層と、を含み、前記第2導電層の不純物濃度は、前記第1導電層の不純物濃度よりも低い。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート動作に関与する結晶表面における表面電荷蓄積を大幅に低減し、ピンチオフ特性が得られる、高性能のInN系FETを提供すること。

【解決手段】チャネル層としてInN系半導体を含む電界効果トランジスタである半導体装置であって、InN系半導体でなるチャネル層2の表面(c面)に、段差を形成して窒化物半導体の六方晶結晶のa面もしくはm面でなる側壁面2aを形成し、この側壁面2aにゲート電極6が配置され、ゲート電極6を挟むようにソース電極3とドレイン電極4がc面上に形成されている。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

トレンチゲート型半導体装置

【課題】本発明は、アバランシェ耐量と主耐圧を向上させることができるトレンチゲート型半導体装置を提供することを目的とする。

【解決手段】本願の発明に係るトレンチゲート型半導体装置は、基板と、該基板上の第1導電型のエピタキシャル成長層と、該エピタキシャル成長層上の第2導電型の拡散層と、該拡散層を貫通し、先端が該エピタキシャル成長層に達するトレンチゲートと、該トレンチゲートの先端に接するように該エピタキシャル成長層に形成された、該エピタキシャル成長層よりもキャリア濃度の低い、第1導電型の低キャリア濃度部と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】半導体の表面の酸化物を含む不純物を、エッチングあるいは、他の層を積層する前に除去する。

【解決手段】第1の半導体層110の少なくとも一部に接し、第1の半導体層110に含まれる不純物の固溶度が、第1の半導体層110より高い第1の犠牲層を形成する第1犠牲層形成工程と、第1の犠牲層および第1の半導体層をアニールするアニール工程と、第1の犠牲層をウェットプロセスで除去する除去工程と、第1の半導体層の少なくとも一部を覆う絶縁層120を形成する工程および第1の半導体層の一部をエッチングする工程の少なくとも一の工程と、第1の半導体層に電気的に接続された電極層126を形成する電極形成工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

半導体不揮発性メモリ装置

【課題】 占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】 ドレイン領域内のトンネル領域と微細穴に埋め込まれる形で形成されたフローティングゲート電極の側面との間にはトンネル絶縁膜を設け、微細穴に接するドレイン領域の表面付近には、電気的にフローティング状態である第1導電型のトンネル防止領域を設けた。

(もっと読む)

ダイオードを含む半導体装置

【課題】ダイオードを含む半導体装置において、ダイオードの逆回復挙動とオン状態特性とのトレードオフを改善する。

【解決手段】半導体装置200は陰極216と陽極218を含む。陽極は第1のp型半導体陽極領域204と第2のp型半導体陽極領域206を含む。第1のp型半導体陽極領域204は陽極接触領域218に電気的に接続される。第2のp型半導体陽極領域206は、第2のp型陽極領域と陽極接触領域218間を電気的に接続または切断するように構成された、MOSFET228等のスイッチを介し陽極接触領域218に電気的に接続される。

(もっと読む)

半導体装置および電力変換装置

【課題】低損失と高耐圧を保持しながら、ターンオンスイッチング期間中におけるdv/dtのゲート駆動回路による制御性を向上できる半導体装置を提供する。

【解決手段】第1導電型の第1半導体層4と、その表面付近に形成された第2導電型の第2半導体層2と、これに電気的に接続する第1主電極11と、第1半導体層4に隣接し第2半導体層2とは逆側の表面付近に形成された第2導電型の第3半導体層6と、この上部に選択的に設けられた第1導電型の第4半導体層7と、第3半導体層6及び第4半導体層7に電気的に接続する第2主電極14と、側面が第4半導体層7と第3半導体層6に接し第1半導体層4に達するトレンチ17と、この側面に沿ってポリシリコンのサイドウオールにより形成されたゲート電極9と、トレンチ17内でゲート電極9から離れて設けられ第2主電極14と電気的に接続するポリシリコン電極18が設けられている。

(もっと読む)

半導体装置

【課題】 縦型MOSFETのオン抵抗及びスイッチング損失の低減。

【解決手段】 封止体と、前記封止体内に位置する半導体チップと、前記封止体の内外に亘って延在する複数のリードと、前記半導体チップの電極と前記封止体内に位置するリードの内端を電気的に接続する導電性のワイヤとを有し、前記半導体チップには縦型電界効果トランジスタセルが並列接続状態で複数組み込まれ、半導体チップの表面にはゲート電極とソース電極が交互に並んでそれぞれ複数配置されるとともに、前記各電極に対応してリードが並び、前記各電極と前記対応した各リードは前記ワイヤによって接続されていることを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

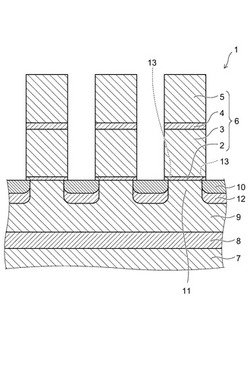

半導体装置及びその製造方法

【課題】包囲型ゲート電極付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に設けられた第1の半導体層5間に、第2の絶縁膜3が設けられていない部分上に設けられた第2の半導体層6が挟まれた構造からなる半導体層が島状に絶縁分離されて設けられ、第2の半導体層6の周囲にはゲート絶縁膜12を介して包囲型ゲート電極13が設けられ、第1の半導体層5には概略高濃度ソースドレイン領域(8、11)及び低濃度ソースドレイン領域(9、10)が設けられ、第2の半導体層6には概略チャネル領域が設けられ、高濃度のソースドレイン領域(8、11)及び包囲型ゲート電極13には配線体(17、18、20、21)が接続されているMISFET。

(もっと読む)

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高いゲート絶縁膜を備えたSiC半導体装置を提供する。

【解決手段】8度以下のオフ角度を有する炭化珪素基板(1)と、この基板上に形成された第1導電型の第1炭化珪素領域(2)と、この領域の表面に形成された第2導電型の第2炭化珪素領域(3)と、この領域の表面に形成され、不純物濃度が第2の炭化珪素領域と同程度に調整された第1導電型の第3炭化珪素領域(4)と、この領域の表面に選択的に形成された第1導電型の第4炭化珪素領域(5)と、第2炭化珪素領域の表面に形成された第2導電型の第5炭化珪素領域(6)と、第1炭化珪素領域から第3炭化珪素領域の少なくとも端部までを覆うように形成されたゲート絶縁膜(7)と、この上に形成されたゲート電極(8)とを具備し、第3炭化珪素領域の表面における、第3と第4炭化珪素領域の境界面は、オフ角度方向と90°以外の角度で交差するように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】リーク電流を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】MOSFET100の製造方法は、炭化珪素基板1を準備する工程と、炭化珪素基板1上に活性層7を形成する工程と、活性層7上にゲート酸化膜91を形成する工程と、ゲート酸化膜91上にゲート電極93を形成する工程と、活性層7上にソースコンタクト電極92を形成する工程と、ソースコンタクト電極92上にソース配線95を形成する工程とを備える。ソース配線95を形成する工程は、ソースコンタクト電極92上に導電体膜を形成する工程と、導電体膜を反応性イオンエッチングによりエッチングすることにより導電体膜を加工する工程とを含む。そして、MOSFET100の製造方法は、導電体膜を加工する工程よりも後に、炭化珪素基板1を50℃以上の温度に加熱するアニールを実施する工程をさらに備える。

(もっと読む)

201 - 220 / 3,643

[ Back to top ]