Fターム[4M104CC05]の内容

半導体の電極 (138,591) | 電極の種類(発明部分) (8,574) | MISゲート電極 (3,643)

Fターム[4M104CC05]に分類される特許

141 - 160 / 3,643

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

二重仕事関数金属ゲート構造体及びその製造方法

【課題】二重金属ゲートを有する構造体において金属膜の仕事関数を調整する為の改善した方法および半導体素子を提供する。

【解決手段】半導体素子は単一金属膜に対し、NMOSにおいてはフッ素、PMOSにおいては炭素をそれぞれ選択的にドーピングすることによって形成される二重仕事関数の金属ゲート電極108’、109’を有する。

(もっと読む)

半導体装置、半導体装置の製造方法、基板処理システムおよびプログラム

【課題】閾値電圧が上昇するのを防止または抑制でき、フラットバンド電圧が低下するのを防止または抑制できる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜30と、ゲート絶縁膜上に形成されたTiN膜41と、TiN膜41上に形成されたTiAlN膜43と、TiAlN膜43上に形成されたシリコン膜45と、を有する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】さらなる微細化に対しても適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現する。

【解決手段】ゲート電極120bは、第1の仕事関数を有する第1の金属含有膜114bと、第1の金属含有膜114b上に形成されており且つ第2の仕事関数を有する第2の金属含有膜117bとを含む。ゲート電極120aは、第1の金属含有膜114を含まないと共に第2の金属含有膜117aを含む。ゲート電極120bにおける第1の金属含有膜114bと第2の金属含有膜117bとの間に拡散防止層115bが形成されている。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置の製造方法

【課題】水素を用いた熱分解において、水素濃度を規定してエッチング速度を制御することで、半導体装置の製造方法の加工精度を向上させる。

【解決手段】半導体装置1の製造方法は、基板10に窒化物半導体で形成された第1層(障壁層25)および第2層(キャップ層26)を順に堆積させる堆積工程と、窒素および水素の混合雰囲気中で加熱して第2層をエッチングする熱エッチング工程とを備える。熱エッチング工程では、水素濃度が1%以上20%以下であることが望ましい。

(もっと読む)

トレンチ絶縁ゲート型半導体装置

【課題】セル領域が接する平行トレンチ部分と接しない平行トレンチ部分の表面間隔が異なるトレンチ表面パターンを有していても、耐圧低下がなく、低オン電圧が得られるトレンチ絶縁ゲート型半導体装置を提供すること。

【解決手段】トレンチ9の表面間隔の異なる平行トレンチ部分9a同士は斜行トレンチ部分9bによって交差すること無く連結されるトレンチ表面パターンを備え、前記平行トレンチ部分9aの側壁面の面方位が、前記主面の面方位(100)と直交する等価な面方位{100}であるトレンチ絶縁ゲート型半導体装置。

(もっと読む)

配線膜、薄膜トランジスタ、ターゲット、配線膜の形成方法

【課題】信頼性の高い薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ20のゲート電極15、ソース、ドレイン電極33、34のうち、いずれか一つ以上の電極はバリア膜25を有し、バリア膜25が成膜対象物21又は半導体層30に密着している。NiとMoを100原子%としたときに、バリア膜25は、Moを7原子%以上70原子%以下含有し、ガラスからなる成膜対象物21や半導体層30に対する密着性が高い。また、バリア膜25表面にCuを主成分とする金属低抵抗層26が形成された場合に、Cuが半導体層30に拡散しない。

(もっと読む)

表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(もっと読む)

高電力マイクロ電子デバイスのための金属化構造

【課題】高電力で高性能なデバイスによって生成される熱応力に耐えることができる金属相互接続システムを提供する。

【解決手段】半導体デバイス構造であって、炭化ケイ素およびIII族窒化物からなる群から選択される広バンドギャップの半導体部分と、該半導体部分に対する相互接続構造であって、それぞれ2つの高導電性層と互い違いに、少なくとも2つの拡散バリア層を含む、相互接続構造とを備え、該拡散バリア層は、該高導電性層とは異なる熱膨張係数を有し、該高導電性層よりも低い熱膨張係数を有し、該それぞれの熱膨張係数の差異は、該高導電性層の膨張を抑えるために十分な大きさであるが、層間の接着強度を超える歪みを隣接層間に生じさせる差異よりも小さい、半導体デバイス構造。

(もっと読む)

プラズマ窒化処理方法、プラズマ窒化処理装置および半導体装置の製造方法

【課題】選択的に窒化物膜を形成する。

【解決手段】処理容器2内に窒素含有ガスを供給し、処理容器2内の圧力を133Pa以上1333Pa以下の範囲内に設定して、処理容器2内に窒素含有プラズマを生成し、該窒素含有プラズマによって、シリコンを含有する第2の部分100Bの表面100Baを窒化させずに、タングステンを含有する第1の部分100Aの表面100Aaを選択的に窒化して、第1の部分100Aの表面100Aaに窒化タングステン膜107を形成する。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

絶縁ゲート型半導体装置

【課題】 MOSFETのゲート電極を基板の周囲において引き出すゲート引き出し配線の引き出し部は、素子領域内と同等の効率で機能するMOSFETのトランジスタセルCを配置することができない非動作領域となる。つまり、ゲート引き出し配線を、例えばチップの4辺に沿って配置すると、非動作領域が増加し、素子領域の面積拡大や、チップ面積の縮小に限界があった。

【解決手段】 ゲート引き出し配線と、ゲート引き出し配線と保護ダイオードとを接続する導電体とを、チップの同一辺に沿って曲折しない一直線状に配置する。又これらの上に重畳して延在し、これらと保護ダイオードを接続する第1ゲート電極層の曲折部を1以下とする。更に保護ダイオードを導電体またはゲート引き出し配線と隣接して配置し、保護ダイオードの一部をゲートパッド部に近接して配置する。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】ゲート電極140は素子形成領域104に形成されている。サイドウォール層160は、ゲート電極140の側壁を覆っている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、及びゲート電極140上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。ゲート電極140のうちコンタクト210と隣に位置する部分は、サイドウォール層160より低く形成されている。絶縁層200は、ゲート電極140のうちコンタクト210と隣に位置する部分上かつ、サイドウォール層160同士の間に形成されている間隙に埋設される。

(もっと読む)

プラズマ処理方法およびプラズマ処理装置

【課題】段差を有する膜構造を高精度にエッチングするプラズマ処理装置またはドライエッチング方法を提供する。

【解決手段】真空容器107と、この真空容器内部の処理室内に配置されその上面にエッチング対象のウェハ112が載せられる下部電極113と、下部電極113にバイアス電位を形成するための高周波電力を供給するバイアス印加装置118,120と、前記処理室内に反応性ガスを導入するガス供給手段111と、前記処理室内にプラズマを生成するための電界を供給する電界供給手段101〜103と、前記高周波電力により前記ウェハ112に入射する前記プラズマ中のイオンのエネルギーの分布を調節する調節装置127とを備えたプラズマ処理装置。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法を提供する。

【解決手段】本発明は、基板上に薄膜トランジスタを製造する製造装置であり、基板に関する基板情報を取得する取得部と、取得部で得られた基板に関する基板情報に基づいて、基板の伸縮強度が高い方向を特定し、伸縮強度が高い方向と薄膜トランジスタのチャネル領域を挟んでソース電極およびドレイン電極が配置される配置方向とが直交するように薄膜トランジスタを形成する向きを設定する設定部とを有する。

(もっと読む)

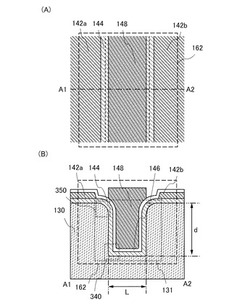

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

141 - 160 / 3,643

[ Back to top ]