Fターム[4M104DD22]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 析出面の前処理 (2,098) | 表面処理 (1,044)

Fターム[4M104DD22]の下位に属するFターム

Fターム[4M104DD22]に分類される特許

41 - 60 / 634

半導体装置の製造方法

【課題】炭化珪素単結晶基板を用いた半導体装置の製造方法において、炭化珪素表面の金属汚染を十分除去することにより、製造された炭化珪素半導体素子の初期特性を改善する。また、金属汚染を低減し、半導体装置の長期信頼性を向上する方法を提供する。

【解決手段】炭化珪素単結晶基板を用いた半導体装置の製造方法において、炭化珪素表面を酸化するステップと、該ステップにより炭化珪素表面に形成された二酸化シリコンを主成分とする膜を除去するステップとからなる炭化珪素表面の金属汚染除去工程を適用する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

半導体上の銅のめっき

【課題】前面電流トラックを形成したドープ半導体ウェハの銅めっきに関する改善された銅めっき方法を提供する。

【解決手段】前面、裏面およびPN接合を含む半導体を提供し、下層を含む導電トラックのパターンを前記前面が含み、かつ前記裏面が金属接点を含んでおり;前記半導体を一価銅めっき組成物と接触させ;並びに導電トラックの下層上に銅をめっきする。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

薄膜トランジスタ基板の製造方法およびトップゲート構造薄膜トランジスタ基板

【課題】本発明は、簡便な工程で製造可能な、電荷注入効率に優れた薄膜トランジスタ基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、基板上に金属電極層を形成する金属電極層形成工程と、上記金属電極層の上面に、電子吸引性または電子供与性の官能基を有する表面処理剤で表面処理を行うことにより、表面処理層積層体を形成する表面処理工程と、上記表面処理層積層体をパターニングし、ソース電極およびドレイン電極を形成するパターニング工程と、上記ソース電極および上記ドレイン電極上に有機半導体層を形成する有機半導体層形成工程と、上記有機半導体層上にゲート絶縁層を形成するゲート絶縁層形成工程と、上記ゲート絶縁層上にゲート電極を形成するゲート電極形成工程と、を有することを特徴とする薄膜トランジスタ基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

Ni膜の形成方法

【課題】 成膜温度、成膜圧力、還元ガスの使用量・使用割合等の成膜条件を設定することにより、所望の物性を有する利用範囲の広いNi膜の形成方法を提供すること。

【解決手段】 真空槽の中でSi基板を一定温度に保持してニッケルアルキルアミジナート(但し、アルキルは、メチル基、エチル基、ブチル基及びプロピル基から選ばれる。)とH2とNH3とをこの真空槽内に導入し、CVD法でNi膜を形成する方法であって、成膜温度が280℃より高く350℃以下であること。

(もっと読む)

半導体装置の製造方法

【課題】本実施形態は、コンタクトプラグの抵抗の低減を行うことができる半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板にコンタクトホール又はコンタクトトレンチを形成し、コンタクトホール又はコンタクトトレンチの底に、アモルファスシリコン層又は多結晶シリコン層を形成し、アモルファスシリコン層又は多結晶シリコン層を覆うように不純物を含むニッケル膜を形成し、加熱することによりニッケル膜とアモルファスシリコン層又は多結晶シリコン層とを反応させて、ニッケルシリサイド膜を形成し、コンタクトホール又はコンタクトトレンチを埋め込むようにコンタクト金属膜を形成する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】コンタクト抵抗を低減しつつ、イオン注入したp+層の消失を低減できる炭化珪素半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる炭化珪素半導体装置の製造方法は、(a)炭化珪素半導体基体表面にマスクとしての酸化膜マスク層21、酸化膜マスク層22を形成し、室温でイオン注入する工程と、(b)イオン注入を行った炭化珪素半導体基体表面を活性化アニールする工程と、(c)活性化アニール後の炭化珪素半導体基体表面を、ドライエッチングする工程と、(d)ドライエッチング後の炭化珪素半導体基体表面を犠牲酸化し、犠牲酸化膜5を形成する工程と、(e)犠牲酸化膜5を濃度10%以下の希フッ酸で5分以内のエッチングにより除去する工程と、(f)炭化珪素半導体基体裏面にオーミック電極6を、炭化珪素半導体基体表面の所定領域にショットキー電極7をそれぞれ形成する工程とを備える。

(もっと読む)

表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法を提供する。

【解決手段】本発明は、基板上に薄膜トランジスタを製造する製造装置であり、基板に関する基板情報を取得する取得部と、取得部で得られた基板に関する基板情報に基づいて、基板の伸縮強度が高い方向を特定し、伸縮強度が高い方向と薄膜トランジスタのチャネル領域を挟んでソース電極およびドレイン電極が配置される配置方向とが直交するように薄膜トランジスタを形成する向きを設定する設定部とを有する。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法、ならびにプログラム

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法、ならびにプログラムを提供する。

【解決手段】本発明は、基板上にゲート電極、ゲート絶縁層、半導体層、ソース電極およびドレイン電極が少なくとも設けられた薄膜トランジスタの製造方法である。ソース電極およびドレイン電極を形成する工程において、基板の歪み、または基板の伸縮率に基づいて、露光データを、スケーリング処理を用いて薄膜トランジスタのチャネル長を固定した状態で補正して第1の補正データを作成する。この第1の補正データに基づいて、ソース電極およびドレイン電極の形成領域にレーザ光を照射し、その形成領域を親液性にする。この形成領域に、ソース電極およびドレイン電極となる液滴を、打滴データに基づいて打滴する。

(もっと読む)

非晶質酸化物薄膜トランジスタ及びその製造方法、その薄膜トランジスタを含むディスプレイパネル

【課題】本発明の実施例は非晶質酸化物薄膜トランジスタ及びその製造方法、ディスプレイパネルを開示する。

【解決手段】前記非晶質酸化物薄膜トランジスタは、ゲート電極、ゲート絶縁層、半導体活性層、ソース電極及びドレイン電極を含む。前記半導体活性層はチャネル層とオーミック接触層を含み、前記チャネル層は前記オーミック接触層に比べ酸素含有量が高い。また、前記チャネル層は前記ゲート絶縁層と接し、前記オーミック接触層は二つの独立したオーミック接触領域に分けられ、かつ前記二つの独立したオーミック接触領域はそれぞれ前記ソース電極、ドレイン電極と接する。

(もっと読む)

半導体素子及び半導体素子形成方法

【課題】ゲルマニウムをチャネル材料とする金属/ゲルマニウムからなるソース/ドレイン構造を有する半導体素子を提供する。

【解決手段】半導体と金属とが接合してソース/ドレイン構造を形成する半導体素子において、ゲルマニウム(Ge)を3価元素(又は5価元素)でドーピングしたp型ゲルマニウム(又はn型ゲルマニウム)をチャネル2の材料とし、当該p型ゲルマニウム(又はn型ゲルマニウム)の任意の結晶面における原子配置と同一の原子配置である結晶面を有する金属3を、前記同一の原子配置である結晶面で接合して界面を形成し、当該形成された界面を用いたソース/ドレイン構造を有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

(もっと読む)

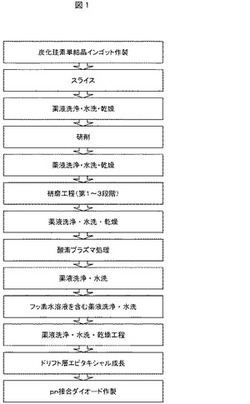

ダイオードの製造方法

【課題】製造過程でエピタキシャル層の表面部に形成されるエッチピットに起因するリーク電流を抑えること。

【解決手段】ダイオードの製造方法は、エピタキシャル層の表面にキャップ層を形成するキャップ層形成工程(S3)と、キャップ層が形成されている状態でドーパントを活性化させるアニール工程(S4)と、キャップ層を除去するキャップ層除去工程(S5)と、エッチング技術を利用してエピタキシャル層の表面を洗浄する洗浄工程(S6)と、エピタキシャル層の表面部に形成されているエッチピットの底部を平滑化させる底部平滑化工程(S7)と、を備えている。

(もっと読む)

半導体装置及び電子機器

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、酸化物半導

体を有する半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する半導体装置の作

製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって

形成されたマスク層を用いて酸化物半導体膜及び導電膜のエッチング工程を行う。エッチ

ング工程において、第1のエッチング工程は、エッチングガスによるドライエッチングを

用い、第2のエッチング工程はエッチング液によるウエットエッチングを用いる。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタ及び薄膜トランジスタの製造方法を提供する。

【解決手段】薄膜トランジスタは、第1方向に形成された少なくとも1本のゲートラインを含むゲート11と、ゲート上に形成されたゲート絶縁層12と、ゲート絶縁層12上に形成された少なくとも1つのソース13及びドレイン14と、を含み、ソース13及びドレイン14のうち少なくともいずれか一つは、延長部分13b、14bを含み、延長部分13b、14bは、少なくとも1本のゲートラインと平行するように、第1方向に形成される。ゲート11は、ライン状に均一厚を有し、その側面と上面との間に曲面を含み、1本または2本以上のゲートラインを含む形態となる。

(もっと読む)

配線形成方法、及び配線形成装置

【課題】絶縁層が積層された導電層に該絶縁層を貫通するカーボンナノチューブが接続される配線構造にて電気的特性を向上することのできる配線形成方法、及び該方法を用いる配線形成装置を提供する。

【解決手段】

下部配線層32に積層された絶縁層34を貫通するホール35に、その内表面の全体が含まれるように触媒層36,37を形成した後、ホール35の内部にシースShが形成され、且つホール35の内壁面35aに対するシースの厚さがホール35の底壁面35bに対するシースShの厚さよりも小さくなるようにプラズマを生成する。そして、ホール35の内壁面35aに形成された触媒層36,37をプラズマ中のスパッタ粒子Spによって除去した後、ホール35の底壁面35bに残された触媒層36,37を用いて該底壁面35bからカーボンナノチューブ38を形成する。

(もっと読む)

半導体発光素子及び半導体発光装置

【課題】高輝度、高効率、高信頼性を達成する半導体発光素子を提供する。

【解決手段】実施形態に係る半導体発光素子は、積層構造体と、電極と、を備える。積層構造体は、窒化物系半導体からなる第1導電形の第1半導体層と、窒化物系半導体からなる第2導電形の第2半導体層と、前記第1半導体層と前記第2半導体層との間に設けられた発光層と、を有する。電極は、第1金属層、第2金属層及び第3金属層を有する。第1金属層は、第2半導体層の発光層とは反対側に設けられ、銀または銀合金を含む。第2金属層は、第1金属層の第2半導体層とは反対側に設けられ、金、白金、パラジウム、ロジウム、イリジウム、ルテニウム、オスミウムの少なくともいずれかの元素を含む。第3金属層は、第2金属層の第1金属層とは反対側に設けられる。第3金属層の第1半導体層から第2半導体層に向かう方向に沿った厚さは、第2金属層の前記方向に沿った厚さ以上である。

(もっと読む)

電力用半導体装置

【課題】本発明は、製造プロセスが煩雑でなく、かつ高い絶縁耐力を有する電力用半導体装置の提供を目的とする。

【解決手段】本発明に係る電力用半導体装置は、第1導電型のSiC基板1と、SiC基板1上に形成され、その表面にリセス構造2aが形成された第1導電型のドリフト層2と、リセス構造2aの表面内に配設された第2導電型の終端部3と、終端部3の一端にかかるようにドリフト層2上に形成され、ドリフト層2とショットキー接続するショットキー電極4,5と、終端部3を被うようにドリフト層2上に形成された絶縁膜6と、絶縁膜6上に形成され、ショットキー電極5と電気的に接続された導電膜8とを備える。導電膜8の抵抗値は106(Ω/sq.)以上1013(Ω/sq.)以下である。

(もっと読む)

41 - 60 / 634

[ Back to top ]