Fターム[4M104DD55]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | 電極への不純物導入(析出時又は後) (529)

Fターム[4M104DD55]の下位に属するFターム

限定領域への導入 (73)

固相膜(PSG等)からの導入 (8)

Fターム[4M104DD55]に分類される特許

141 - 160 / 448

半導体装置及びその製造方法

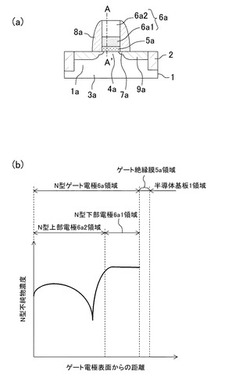

【課題】 空乏化が抑制されたゲート電極を備え、特性のばらつきが小さく十分な駆動能力を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1における活性領域1a上に形成された第1のゲート絶縁膜5aと、第1のゲート絶縁膜5a上に形成され、第1導電型の不純物を含む多結晶シリコン膜からなる第1のゲート電極6aとを備えている。第1のゲート電極6aに含まれる第1導電型の不純物は、第1のゲート電極6aにおける第1のゲート絶縁膜5aとの界面部分に第1の濃度ピークを有し、且つ、第1のゲート電極6aの上面部分に第2の濃度ピークを有し、第1の濃度ピークは、第2の濃度ピークよりも濃度が大きい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート長が膜厚で規定された縦型の半導体装置であって、良好な信頼性のゲート絶縁膜を備え、微細化が容易な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置10の基板11上の、チャネル領域32に対応する領域を

除いた領域を種結晶領域として用い、チャネル領域32を迂回する形で、

基板11上に選択エピタキシャル成長又は固相エピタキシャル成長によってゲートとなる単結晶膜を結晶成長させる。この単結晶膜をCMPで窒化膜19の膜厚に規定し、この単結晶膜と絶縁膜からなる積層膜に、チャネルとなる任意の大きさの開口を形成する。この開口形成時にできた、単結晶膜の端面を酸化させることによりゲート酸化膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタ特性を長期安定化して使用することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板1上にゲート絶縁膜2を形成する工程と、前記ゲート絶縁膜上にポリシリコン膜3を形成する工程と、前記ポリシリコン膜の下層側に重元素の不純物イオン4をイオン注入する工程と、前記ポリシリコン膜の上層側に、前記重元素より質量の小さい軽元素の不純物イオン6をイオン注入する工程と、前記ポリシリコン膜を加工することにより、前記ゲート絶縁膜上にゲート電極3aを形成する工程と、前記半導体基板に不純物イオンをイオン注入し、熱処理を施すことによりソース・ドレイン領域の拡散層9を形成する工程と、を具備することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】スループットを向上できる半導体装置の製造方法を提供する。

【解決手段】第1絶縁膜15に覆われた第1半導体パターン13eを第1活性領域7の上方に形成し、第2半導体パターン13aを第2活性領域3の上方に形成し、第1絶縁膜15と第1、第2半導体パターン13a、13eの上方に第2絶縁膜25を形成し、第2絶縁膜25及び第1絶縁膜15をエッチングして第1半導体パターン13eに達する深さの開口を形成し、第2絶縁膜25をパターニングして第2半導体パターン13aの側面にサイドウォールを形成し、第1、第2半導体パターン13a、13eのそれぞれの上に金属膜を形成し、第1、第2半導体パターン13a、13eと金属膜31を反応させることによりシリサイド層31a、31eを形成する工程を含む。

(もっと読む)

半導体装置、およびその製造方法

【課題】配線間をCuプラグによって電気的に接続する構成において、Cuプラグとの電気的接続の信頼性が高く、リーク電流が少ない半導体装置、およびその製造方法を提供することを目的とする。

【解決手段】本発明における半導体装置100は、拡散層43およびゲート電極42を形成した半導体基板1と、半導体基板1上に形成された層間絶縁膜5と、層間絶縁膜5を貫通し、拡散層43およびゲート電極42上に形成されたコンタクトホール61と、コンタクトホール61の内面に形成されたTiバリアメタル層62と、バリアメタル層62上に形成されたW、Co、Ru、Ptのいずれかを含むシード層63と、シード層63上であってコンタクトホール61を充填するように形成されたCuプラグ64と、Cuプラグ64上に形成された配線層7と、を備える。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 微細化に伴うコンタクト抵抗の増加を防止した、信頼性の高い素子特性を有する薄膜半導体装置を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、及び前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成された第1及び第2のコンタクト孔内にそれぞれ埋め込まれた第1導電型の不純物を含む凸型ソース多結晶半導体層並びに第1導電型の不純物を含む凸型ドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】コンタクトおよび配線形成時の合わせマージンがゼロであり、集積度を大幅に向上し、パターンレイアウトの自由度の拡大を可能とする薄膜半導体素子及びその製造方法を提供する。

【解決手段】透明絶縁性基板10上に形成され、第1導電型の不純物を含むソース領域及びドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜及びゲート電極18、前記ソース領域又はドレイン領域の表面に形成された高融点金属と半導体との化合物からなる層、前記島状半導体層及びゲート電極を覆う層間絶縁膜29、及び前記ソース領域又はドレイン領域に接続された局所配線28を具備し、前記局所配線28は、前記ソース領域又はドレイン領域の表面に形成された前記化合物層と高融点金属層との2層構造、及び前記ソース領域又はドレイン領域の外側に形成された前記高融点金属層の延長からなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 周辺回路領域の電荷蓄積層へのホットキャリア注入の影響を少なくする半導体装置等を提供する。

【解決手段】 半導体装置であって、少なくとも1つの不揮発性記憶セルの少なくとも1つの第1のトランジスタと、前記少なくとも1つの不揮発性記憶セルを駆動するための少なくとも1つの第2のトランジスタと、を含む。第1のトランジスタは、第1のゲート絶縁層と、第1のゲート電荷蓄積層と、第2のゲート絶縁層とを有する。第2のトランジスタは、第3のゲート絶縁層と、第2のゲート電荷蓄積層と、第4のゲート絶縁層とを有する。フッ素系ガスおよび/または水素系ガスを用いるイオン注入が実施された前記第2のゲート電荷蓄積層(22b’)の全部または一部の第1の電荷蓄積能力は、フッ素系ガスおよび/または水素系ガスを用いるイオン注入が実施される前の前記第2のゲート電荷蓄積層(22b’)の前記全部または前記一部の第2の電荷蓄積能力より低い。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】バックゲート電極を有するMOSトランジスタのS/D層について、その抵抗を小さくすることができ、且つ、その寄生容量を低減できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】Si基板1上に形成されたSi層68と、Si層68上に絶縁膜2を介して形成されたSi層3と、Si層3を平面視で囲むようにSi基板1上に形成された絶縁膜4とを有し、絶縁膜4が絶縁膜2よりも厚く形成されたSOI基板10に、MOSトランジスタ50を形成する方法であって、Si層3上にゲート絶縁膜5を介してゲート電極6を形成する工程と、ゲート電極6の両側にS/D層20を形成する工程と、を含み、S/D層20を形成する工程は、ゲート電極6が形成される領域の両側に位置する端部領域のSi層3に不純物層7を形成する工程と、不純物層7と接触する導電膜8を、不純物層7上から絶縁膜4上にかけて形成する工程と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】MONOS型不揮発性記憶装置を含む、高い性能を有する半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、MONOS型不揮発性記憶セルの第1のトランジスタと、記憶セルを制御または駆動するための第2のトランジスタを含む。第1のトランジスタは、ソースドレイン領域12,13,18,19と,ゲート絶縁層22a’と、ゲート電荷蓄積層22b’と、第2のゲート絶縁層22c’と、ゲート導電層14’と、絶縁層16,17、とを有する。ゲート絶縁層22a’は、ソースドレイン領域の一部12,13の上に形成された下層60と、下層60の一部である中心部の上に形成された上層61とを有する。第2のトランジスタの第2のソースドレイン領域12,13,18,19を形成するために用いられたレジストを洗浄除去するときに、下層60と上層61とに区別された。

(もっと読む)

半導体装置およびその製造方法

【課題】 ディスターブを防止する半導体装置等を提供する。

【解決手段】 半導体装置は、少なくとも1つの不揮発性記憶セルの少なくとも1つのトランジスタを含む。前記少なくとも1つの不揮発性記憶セルの前記少なくとも1つのトランジスタは、第1のゲート絶縁層(22a’)と、前記第1のゲート絶縁層(22a’)の上に形成された電荷蓄積能力を有するゲート電荷蓄積層(22b’)と、前記ゲート電荷蓄積層(22b’)の上に形成された第2のゲート絶縁層(22c’)とを有する。前記ゲート電荷蓄積層(22b’)の一部(31)の第1の電荷蓄積能力は、前記ゲート電荷蓄積層(22b’)の残部(32)の第2の電荷蓄積能力より低い。前記ゲート電荷蓄積層(22b’)の前記一部(31)の前記第1電荷蓄積能力は、フッ素系ガスおよび/または水素系ガスを用いるイオン注入によって低下している。

(もっと読む)

半導体装置の製造方法

【課題】デバイスの性能や信頼性を低下させることなく、注入した不純物を熱処理することができる半導体装置の製造方法を提供する。

【解決手段】下地層であるpGaN層103に形成された注入領域104’上に、GaNのバンドギャップエネルギーよりも小さいバンドギャップエネルギーを有する物質よりなる光吸収膜T1を形成し、この状態で基板101上面から赤外光や赤色光など、pGaN層103のバンドギャップエネルギーよりも小さいエネルギーの所定光を用いてアニールを行う。pGaN層103と比較して光吸収膜T1の方がアニールで使用される光の吸収係数が大きいため、光吸収膜T1直下もしくは近傍の領域(注入領域104’)を選択的に熱処理することが可能となる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧特性と電流増幅特性とに優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】電界緩和領域として機能するRESURF領域110を備えたRESURF−MOSFET100において、RESURF領域110と、ソース用コンタクトとして機能するn+型コンタクト領域104sと、ドレイン用コンタクトとして機能するn+型コンタクト領域104dとのうち少なくとも1つに、n型の導電性を有する原子と窒素原子とを不純物として含ませる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】記憶情報を高速に読み出す半導体集積回路装置の製造方法を提供する。

【解決手段】本発明の半導体集積回路装置の製造方法は、半導体基板上に第1ゲート電極を形成する工程、この工程の後に第1ゲート電極を覆うように半導体基板上に導電性膜を形成する工程、この工程の後に導電性膜の一部を覆うように半導体基板上にマスクパターンを形成する工程、この工程の後にドライエッチングを行いマスクパターンで覆われていない導電性膜をサイドスペーサ状の第2ゲート電極に加工する工程で、且つマスクパターンで覆われた導電性膜を第2ゲート電極のコンタクト領域としてパターニングする工程、この工程の後にマスクパターンを除去する工程、この工程の後に不揮発性メモリセルを覆うように半導体基板上に層間絶縁膜を形成する工程、この工程の後に層間絶縁膜中に第2ゲート電極のコンタクト領域に接続するプラグを形成する工程、を有する。

(もっと読む)

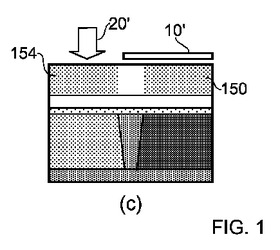

半導体デバイスの製造方法および半導体デバイス

適切な仕事関数の材料のゲート電極を有する半導体デバイスの製造方法を開示する。この方法は、所定数の活性領域(110,120)および該活性領域(110,120)を被覆する誘電体層(130)を含む基板(100)を提供する工程と、前記誘電体層上に積層体(140,150,160)を形成する工程を有する。積層体の形成は、前記誘電体層(130)上に、第1の厚さ、例えば10nm未満を有する第1の金属層(140)を析出させる工程と、該第1の金属層(140)上に、第2の厚さを有する第2の金属層(150)を析出させる工程であり、前記第2の厚さが前記第1の厚さより厚い工程と、前記第2の金属層(150)にドーパント(152,154)を導入する工程と、前記デバイスを温度上昇下にさらし、前記ドーパント(152,154)の少なくとも一部を、前記第2の金属層(150)から前記第1の金属層(140)と前記第2の金属層(150)との界面を越えて、移動させる工程と、前記積層体を所定数のゲート電極(170)にパターニングする工程と、を有する。この方法によれば、ゲート電極は、誘電体層(130)の近くにドーパントプロファイルを有するように形成されるため、ゲート誘電体がドーパントの侵入により劣化することなく、ゲート電極の仕事関数を最適化することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、高誘電率ゲート絶縁膜/多結晶シリコン界面におけるダイマーの発生を既存の製造工程になじみやすい工程により抑制して、フェルミレベルピンニングを除去する。

【解決手段】 半導体基板上方に形成されたHf、Zr或いはAlの少なくとも一つと酸素とを含むゲート絶縁膜とシリコンを含むゲート電極との間に、炭素を含むキャップ層を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】最小の工程数で尚且つ、特性が安定しており、スイッチングスピードの速いパワー半導体装置を実現する。

【解決手段】厚いゲート絶縁膜9及びこれよりも薄いゲート絶縁膜11を形成した後、ゲート電極材料を堆積し、ゲート絶縁膜9下のボディ領域の形成予定部位にp型不純物をイオン注入してp型不純物領域15を形成する。そして、ゲート絶縁膜9,11下にそれぞれp型不純物をイオン注入してボディ領域19a,19bをそれぞれ形成する。ボディ領域19aはp型不純物領域15と一体化する。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSFETダイオードのチャネル幅を効率良く広げることができ、レイアウトの利用効率を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】Si基板1上に絶縁層3を介して形成されたSi層5と、Si層5上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、平面視で環状の第1の部位を有するゲート電極15と、第1の部位の内側と外側のSi層5にそれぞれ形成されたS/D層17、18と、S/D層18とゲート電極15とを接続する配線31と、を備える。このような構成であれば、例えば正方形或いは長方形のアクティブ領域のSi層5に、環状のチャネル領域を形成することができ、MOSFETダイオードのチャネル幅を効率良く広げることができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を活性化するために熱処理をしても閾値の負側へのシフトを抑制した

半導体装置の製造方法を提供する。

【解決手段】基板10上に熱酸化により形成された酸化膜19を介してゲート電極を設けた半導体装置の製造方法であって、基板10上に第1の酸化膜を形成する第1工程と、前記第1の酸化膜を不活性ガス雰囲気にて熱処理をする第2工程と、前記不活性ガスにて熱処理した第1の酸化膜を所定の膜厚となるようにエッチングして得られる第2の酸化膜を形成する第3工程と、前記第2の酸化膜上にゲート電極を形成して熱処理する第4工程と、を有する製造方法である。

(もっと読む)

電子素子とその製造方法

【課題】ショットキー障壁を生じさせず,所望する電気伝導特性を有する電子素子及び電子素子の製造方法を提供することを課題とする。

【解決手段】本発明に係る電子素子では,離間されて配置された一対の電極102と,電極102間それぞれに接続され,半導体的性質を有する半導体ナノワイヤ101とを備え,電極102が,ナノワイヤ101と同一の材料又は同一の半導体的性質を有する材料からなることを特徴とする。

(もっと読む)

141 - 160 / 448

[ Back to top ]