Fターム[4M104DD55]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | 電極への不純物導入(析出時又は後) (529)

Fターム[4M104DD55]の下位に属するFターム

限定領域への導入 (73)

固相膜(PSG等)からの導入 (8)

Fターム[4M104DD55]に分類される特許

81 - 100 / 448

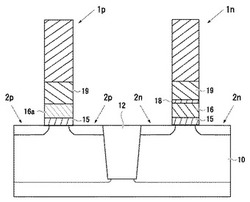

半導体装置の製造方法および半導体装置

【課題】容易に製造できる半導体装置を提供する。

【解決手段】半導体装置は、PMOSトランジスタのゲート電極1pの仕事関数値が、High-kゲート絶縁膜16(16a)、及び、High-kゲート絶縁膜16・酸化シリコン膜15界面へのAlの拡散により調整されており、NMOSトランジスタのゲート電極1nの仕事関数値が、High-kゲート絶縁膜16・金属ゲート膜19間に挿入された、数原子層程度のAl層18により調整されている構成を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率材料を含むゲート絶縁膜と、高融点金属等を含むゲート電極とを備え、消費電力の低減と高速動作化とが図られた半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、高誘電率膜を含む絶縁膜101aを形成する工程(a)と、上面に酸化膜が形成され、高融点金属または高融点金属の化合物の少なくとも一方を含む第1の導電膜102aを形成する工程(b)と、酸化膜103aを間に挟んで第1の導電膜102a上に、シリコンを含む第2の導電膜104aを形成する工程(c)と、第1の導電膜102aおよび第2の導電膜104aに対してイオン注入を行い、酸化膜103aの構成材料を前記第2の導電膜104a中のシリコンと混合させてミキシング層103bを形成する工程(d)と、熱処理を行ってミキシング層103bを導電層103cにする工程(e)とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域にエピタキシャル結晶を含み、エピタキシャル結晶上の金属シリサイドに起因する接合リークの発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、ファセット面13fを有するエピタキシャル結晶層13を有するMISFET10と、MISFET10を他の素子から電気的に分離し、上層3aのゲート電極12側の端部の水平方向の位置が下層3bのそれよりもゲート電極12に近く、上層3aの一部がファセット面13fに接する素子分離絶縁膜3と、エピタキシャル結晶層13の上面、およびファセット面13fの上層3aとの接触部よりも上側の領域に形成されたシリサイド層18と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、最適な仕事関数を有するメタルゲート電極を持つ半導体装置及びその製造方法に関する。

【解決手段】n チャネルMIS トランジスタを含む半導体装置であり、n チャネルMIS トランジスタは、基板上に形成されたp 型半導体領域、p 型半導体領域に形成されたソース領域102及びドレイン領域104、ソース領域102及びドレイン領域104間のp 型半導体領域上に形成されたゲート絶縁膜106、ゲート絶縁膜106上に形成された金属層108及び化合物層110からなる積層構造を持つゲート電極を有する。金属層108は2 nm未満の厚さ及び4.3 eV以下の仕事関数を有し、化合物層110は4.4 eVを越える仕事関数を有しかつAl及び金属層108とは異なる金属を含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの下部電極のダメージを抑制することができる半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置は、立設する複数の電極と、前記電極の立設を保持する第1の絶縁膜と、前記電極が貫通するように前記第1の絶縁膜に形成され、各々の前記電極の外周側面の少なくとも一部に接触する複数の孔部と、前記第1の絶縁膜に形成され、前記複数の孔部のうちその一部の孔部に連結する第1の開口と、前記第1の絶縁膜に形成され、前記複数の孔部のいずれの孔部に対してよりも前記溝部に近接する位置に配置すると共に前記複数の孔部のいずれにも連結しない第2の開口とを、備えたことを特徴とすることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エミッタ電極の膜厚が均一であり、このために素子特性のばらつきが少ない特性が良好な半導体装置を提供する。

【解決手段】Si基板1上のN−hill層11と、N−hill層11を囲む素子分離領域であるシャロートレンチアイソレーション6に開口されたオープン領域21と、を備えたHCBT100を含む半導体装置において、オープン領域21上に面方位のないアモルファスSi膜30,31を形成する。アモルファスシリコン膜30、31を、N−hill層11がアモルファスシリコン膜30、31から露出する厚みにまでエッチングして電極とする。

(もっと読む)

半導体装置及びその製造方法

【課題】複数のゲート長を有するトランジスタを形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、第1の柱状体と第2の柱状体とを形成する工程と、前記第1及び第2の柱状体と前記半導体基板とを覆う半導体膜であって、前記第1の柱状体を覆う第1の部分と前記第2の柱状体を覆う第2の部分との導電型及び不純物の濃度の少なくとも一方が互いに異なるように半導体膜を形成する工程と、前記半導体膜をエッチバックして、前記第1及び第2の柱状体のそれぞれの側壁に、互いに異なる高さを有する第1の半導体膜柱状部と第2の半導体膜柱状部とを形成する工程と、を備えることを特徴とする半導体装置の製造方法を採用する。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタとp型MISトランジスタとにおいてサイドウォール幅が同一である場合、n型MISトランジスタの高信頼性とp型MISトランジスタの高性能化を両立させることは難しい。

【解決手段】半導体装置は、n型MISトランジスタとp型MISトランジスタとを備えている。n型MISトランジスタは、半導体基板10における第1の活性領域10a上に順次形成された第1のゲート絶縁膜13a及び第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール16aとを備えている。p型MISトランジスタは、半導体基板10における第2の活性領域10b上に順次形成された第2のゲート絶縁膜13b及び第2のゲート電極14bと、第2のゲート電極14bの側面上に形成された第2のサイドウォール16bとを備えている。第2のサイドウォール16bは、第1のサイドウォール16aに比べてサイドウォール幅が小さい。

(もっと読む)

半導体装置

【課題】動作信頼性を向上させる半導体装置を提供すること。

【解決手段】基板10内に、互いに離隔して形成された第1乃至第3拡散層13と、前記第1拡散層13と前記第2拡散層13との間の前記基板10上に第1絶縁膜14を介在して形成された第1電極15を備え、前記第1拡散層13をソースとし、前記第2拡散層13をドレインとする、第1トランジスタ20と、前記第2拡散層13と前記第3拡散層13との間の前記基板10上に第2絶縁膜14を介在して形成された第2電極15を備え、前記第2拡散層13をドレインとし、前記第3拡散層13をソースとする第2トランジスタ21とを具備し、前記第2トランジスタ21は、前記第2電極15及び前記第3拡散層13に固定電圧が与えられることにより、常時オフ状態とされ、前記第1トランジスタ20の閾値は、前記第2トランジスタ21の閾値よりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス工程数を増加させることなく、レイアウト面積が小さく且つ駆動能力が高いMulti−Fin型トランジスタを実現できるようにする。

【解決手段】半導体装置は、シリコンからなる基板100の上に形成され、それぞれ互いに間隔をおき且つ並列に配置された直方体状の複数のソース拡散層110及び複数のドレイン拡散層111(Fin部)と、複数のFin部の上に、各Fin部と交差すると共にそれぞれゲート絶縁膜105を介在させて形成されたゲート電極106とを有している。複数のFin部における少なくとも一方の端部には、少なくとも2つのFin部と電気的に接続されたソース拡散層部コンタクトプラグ120が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】配線層に銅配線を使用する半導体装置において、半導体基板の裏面に付着した銅原子が半導体基板の裏面から内部へと拡散することを抑制し、半導体基板の主面に形成されているMISFETなどの半導体素子の特性劣化を抑制できる技術を提供する。

【解決手段】半導体基板1Sの主面に形成される銅拡散防止膜を銅拡散防止膜DCF1aとし、半導体基板1Sの裏面に形成される銅拡散防止膜を銅拡散防止膜DCF1bとする。本実施の形態1の特徴は、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成する点にある。このように、銅配線の形成工程の前に、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成することにより、半導体基板1Sの裏面から銅原子(銅化合物を含む)が拡散することを防止できる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

表示装置

【課題】オフ電流の低減とともにオフリーク電流の低減が図れ、製造工数の増大をもたらすことなく回路の集積化が図れる薄膜トランジスタを備えた表示装置の提供。

【解決手段】表示部が形成された基板上に複数の薄膜トランジスタが形成されている表示装置であって、

前記薄膜トランジスタは、

ゲート電極と、

前記ゲート電極を跨って形成されたゲート絶縁膜と、

このゲート絶縁膜の上面に形成され、平面的に観て前記ゲート電極の形成領域内に開口が形成された層間絶縁膜と、

前記層間絶縁膜の表面に前記開口を間にして配置された一対の高濃度半導体膜と、

前記層間絶縁膜の前記開口を跨いで形成され、平面的に観て、前記ゲート電極の形成領域内に形成されるとともに前記一対の高濃度半導体膜に電気的に接続された多結晶半導体層と、

前記一対の高濃度半導体膜のそれぞれに重ねられ前記多結晶半導体膜に重ねられることなく形成された一対の電極と、

を備えたものを含む。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力を開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、パターニング後、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力をパターン側面を含めて開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

半導体装置

【課題】強度を保持しつつ、導通時の抵抗を低減可能な電力用の半導体装置を提供する。

【解決手段】半導体装置10は、基板領域1と、基板領域1上に設けられ、炭化珪素を含む半導体材料からなり、複数の凹部が形成されたドリフト領域2と、側壁に配設されたアノード電極3と、凹部の側壁を挟んでアノード電極3と互いに対面するように側壁に配設され、かつ、アノード電極3と絶縁されたカソード電極4とを有する。

(もっと読む)

トレンチ・シールドされた半導体デバイスおよびショットキー・バリア整流デバイスの構造およびそれらを改善するための方法

トレンチ・シールドされた電力用半導体デバイス等の性能を改良するための種々の構造および方法について記載されている。  (もっと読む)

(もっと読む)

81 - 100 / 448

[ Back to top ]