Fターム[4M104DD62]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | 露光 (189)

Fターム[4M104DD62]に分類される特許

161 - 180 / 189

電気光学表示装置およびその製造方法

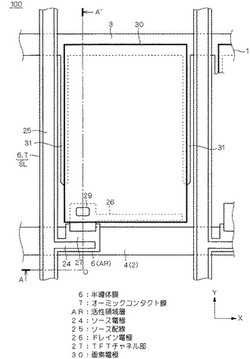

【課題】TFT構造部の製造工程を簡略化するとともに、ソース・ドレイン電極の材質を限定せずとも、TFTチャネル部となる半導体層の膜厚を正確に制御することで、表示ムラを防止した電気光学表示装置を提供する。

【解決手段】活性領域層AR上から、画素電極30の下方の透明絶縁性基板1の上方にかけて延在するようにドレイン電極26が配設されている。ソース電極24およびソース配線25は、その端面が半導体膜6の何れの端面よりも後退した位置となるように配設され、活性領域層AR上のドレイン電極26の端面も、半導体膜6のほぼ平行な関係にある端面よりも後退した位置となるように配設されている。

(もっと読む)

電極基板,薄膜トランジスタ,表示装置、及びその製造方法

本発明は、下部電極をフォトマスクに利用して、絶縁膜上に下部電極と概ね同一パターン形状の撥液領域と概ね反転パターン形状の親液領域を形成して、親液領域内に導電性インクを塗布焼成して、下部電極に対して概ね反転パターン形状の上部電極を自己整合して形成するため、印刷法を用いても位置ずれが発生しない。このため、アクティブマトリクス型薄膜トランジスタ基板などの半導体装置が印刷法を用いて形成できる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極近傍の過度のエッチングを抑制する方法を提供する。

【解決手段】 パターニングすべき膜43,44が形成された基板の上にアモルファスカーボン膜46を形成する。アモルファスカーボン膜46の表面上に所定の領域にパターニングされたレジストパターン47を形成する。レジストパターン47をマスクとして、アモルファスカーボン膜と、パターニングすべき膜の少なくとも下層部分43を残して一部上層部分をエッチングする。その後、レジストパターン47を除去する。さらに、アモルファスカーボン膜46をマスクとして、パターニングすべき膜の少なくとも下層部分43を選択的にエッチングする。

(もっと読む)

薄膜トランジスタを用いた液晶表示装置及びその製造方法

【課題】薄膜トランジスタを用いた液晶表示装置及びその製造方法において、生産工程を簡素化すると共に、ソース配線とゲート配線の配線抵抗の増加を防ぐ。

【解決手段】絶縁基板11上に形成された第1の光透過型感光性樹脂12の開口部に、ゲート電極13とソース配線201’と画素コンタクト層21’とを形成する。これらの上にゲート絶縁膜14と半導体層15とオーミックコンタクト層(n+半導体層)16と保護膜17を形成する。さらに、第2の光透過型感光性樹脂12’の開口部に、ソース電極19とドレイン電極19’と画素電極21とを形成する。また、第2の光透過型感光性樹脂の開口部に形成されるクロス部接続配線は、ソース配線又はゲート配線と同じく、インクジェット塗布された銀微粒子を含有するインクが焼成されてできた焼成銀である。

(もっと読む)

集積回路のパターンレイアウト、フォトマスク、半導体装置の製造方法、及びデータ作成方法

【課題】 ライン&スペースのパターンの端部においてもパターンの解像性を高めることができ、且つリソグラフィマージンの低下やCAD処理時間の増大を抑制する。

【解決手段】 集積回路に露光すべきパターンが形成されたフォトマスクであって、一方向に対する一定間隔の固定ピッチ上にラインとスペースが交互に配列された第1のデバイスパターン10と、第1のデバイスパターン10の配列方向端部に離間して配置され、固定ピッチの3倍以上の奇数倍の幅を有する第2のデバイスパターン20と、第1及び第2のデバイスパターン10,20間に配置され、固定ピッチ上にラインとスペースが交互に配置された、回路動作に影響を与えないダミーパターン30と、第2のデバイスパターン内20で固定ピッチに配置された、露光によって解像されない補助パターン21a,22aと、を有する。

(もっと読む)

半導体装置及びその作製方法

【課題】LDD領域を有する微細TFTを、工程数の少ないプロセスで作製し、各回路に応じた構造のTFTを作り分けることを課題とする。また、LDD領域を有する微細TFTであってもオン電流を確保することを課題とする。

【解決手段】ゲート電極を2層とし、下層のゲート電極のゲート長を上層のゲート電極のゲート長よりも長くし、ハットシェイプ型のゲート電極を形成する。この際に、レジストの後退幅を利用して上層のゲート電極のみをエッチングし、ハットシェイプ型のゲート電極を形成する。また、配線と半導体膜のコンタクト部をシリサイド化し、コンタクト抵抗を下げる。

(もっと読む)

薄膜トランジスタの製造方法

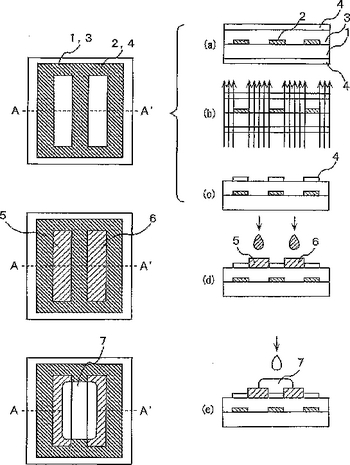

【課題】 蒸着リフトオフという高価な工程を使用せずに、ゲート電極、ソース電極およびドレイン電極の位置合わせ精度を向上させ、ゲート電極に対するソース電極およびドレイン電極の重なりを小さい薄膜トランジスタ製造方法の提供。

【解決手段】本発明の薄膜トランジスタの製造方法は、透明絶縁基板上にゲート電極を形成する工程と、前記透明絶縁基板と前記ゲート電極を覆うようにゲート絶縁膜を形成する工程と、半導体層を形成する工程と、レジストを塗布する工程と、裏露光によって前記ゲート電極に自己整合したレジストパターンを形成する工程と、ソース電極とドレイン電極を形成する工程と、レジストを除去する工程とを少なくとも有する薄膜トランジスタの製造方法であって、前記ソース電極とドレイン電極を形成する工程が、金属ナノ粒子を含む液体を塗布する工程を含む。

(もっと読む)

有機シラン単分子膜の製造方法、薄膜パターンの形成方法、及び有機半導体装置

【課題】 特にX線反射率測定法を用いることにより、各分子が均一に揃った状態で化学的に吸着した良好な膜質の有機シラン単分子膜の製造を可能にした、有機シラン単分子膜の製造方法を提供するとともに、この製造方法を利用した薄膜パターンの形成方法、及び有機半導体装置を提供する。

【解決手段】 少なくとも表層部に酸化物層3を形成した基板1の酸化物層3上に、有機シラン単分子膜7を製造する方法である。予めX線反射率測定法による膜厚測定によって製造する有機シラン単分子膜7の最適厚を、少なくとも加熱条件をパラメータとして実験的に求める工程と、最適厚となる条件のもとで、基板1上に有機シラン単分子膜7を製造する工程と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】 反射防止機能とハードマスク機能を兼備した多層構造のSiC系膜を効率良く、確実に除去し、併せてゲート電極形成プロセスにおける膜の除去工程を簡素化し、デバイスへの悪影響を極力低減できる半導体装置の製造方法を提供する。

【解決手段】 基板上に形成された高誘電体膜と、ポリシリコン膜と、反射防止機能とハードマスク機能とを有するSiC系膜と、を有する積層体に対し、SiC系膜を、パターニングされたレジストをマスクとしてエッチングし、次にSiC系膜をマスクとして、ポリシリコン膜をエッチングした後、少なくとも、SiC系膜および露出した高誘電体膜にプラズマを作用させて改質するプラズマ処理工程と、改質されたSiC系膜および高誘電体膜をウエット洗浄により除去する洗浄工程と、を行なう。

(もっと読む)

高解像度および低解像度にパターニングされた膜特徴部分をもつ大面積電子装置

【課題】大面積の電子装置の製造に利用できるパターニングされたIC用薄膜層の形成方法として、安価に大面積のパターンを形成できるパターニング技術と、小さな特徴パターンを形成できる微細パターニング技術と、を同時に実現する方法を提供する。

【解決手段】本発明は、装置の基板上にパターニングされた薄膜層を形成する方法であって、第1の処理ツールを用いて、前記装置基板上に比較的高解像度の第1構造を形成するステップ(ブロック110)と、第2の処理ツールを用いて、前記装置基板上に、前記第1構造と接続されるように、比較的低解像度の第2構造を形成するステップ(ブロック120)と、を含む方法であることを特徴とする。

(もっと読む)

フォトマスク及び半導体装置の製造方法

ゲートパターン(1)及びゲートパターン(1)間距離が大きい部位に挿入されてなる解像可能線幅のアシストパターン(2a)及び解像限界以下の線幅のアシストパターン(2b)とを備えたハーフトーン位相シフトマスク(11)と、フォトマスク(11)のゲートパターン(1)に対応したシフタパターン(3)を有するレベンソン位相シフトマスク(12)とを用いて、2重露光処理する。この際、アシストパターン(2a),(2b)は消去され、ゲートパターン(1)のみが転写される。これにより、二重露光処理によりパターン転写を行う際に、パターンの共通焦点深度を向上させ、線幅の高均一化を実現し、信頼性の高い半導体装置の製造を可能とする。  (もっと読む)

(もっと読む)

薄膜トランジスタの製造方法及び表示素子

【課題】製造工程を単純化し且つ製造コストを節減することが可能な薄膜トランジスタの製造方法を提供する。

【解決手段】基板100、ゲート電極110、ゲート絶縁体層120、ドレイン電極150、ソース電極130および半導体層140が順次に形成された薄膜トランジスタの製造方法において、金属前駆体を溶媒に溶解させたコーティング液をゲート絶縁体層120上に塗布する段階と、光還元によってドレイン電極150およびソース電極130を形成する段階と、を含む。

(もっと読む)

ナノギャップ電極の形成方法及びこれによって得られたナノギャップ電極並びに該電極を備えた素子

【課題】ランニングコストの高い電子ビーム露光を用いることなく、μm程度のパターニング精度の技術をもちいて、1〜20nmのギャップ長さを持ち、かつ電極幅も100nm以下の、規定されたナノギャップ電極を作製する。

【解決手段】基板上に、光露光によりフォトマスクのパターンを形成する工程、1回目の電極材を斜め蒸着する工程、これをリフトオフする工程、2回目の光露光を行い1回目の蒸着電極膜上に跨ったスリットパターンを作製する工程、2回目の電極材を斜め蒸着する工程及びこれをリフトオフする工程からなるギャップ電極を形成する方法において、前記スリットパターンを作製する際に、1回目の蒸着電極に対して角度α<90°でスリットパターンを作製することを特徴とするナノギャップ電極の形成方法。

(もっと読む)

パターン形成構造、パターン形成方法、デバイス及び電気光学装置、電子機器

【課題】 パターン形成時に、微細パターンと他のパターンとの各々の高さを同じくすることにより、上記パターン上を含む領域を平坦にするバンク構造体、パターン形成方法、及び電気光学装置、電子機器を提供する。

【解決手段】 機能液により形成するパターンに対応した凹部が設けられた隔壁構造体であって、第1パターンに対応して隔壁34に設けられた第1凹部55と、第1パターンに接続され、かつ、第1パターンよりも幅が狭い第2パターンに対応して隔壁34に設けられた第2凹部56と、を含み、第2凹部56の底面の高さが、第1凹部55の底面の高さよりも高く設けられていることを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】 はんだ付けする際の加熱処理によって、ニッケル層の相転移に伴う体積の収縮に起因する最大の引張り応力を緩和する。

【解決手段】 半導体20上に形成されているアルミニウムを主成分とするアルミニウム金属膜42と、そのアルミニウム金属膜42の表面を複数の領域に分割する分割絶縁層52bと、アルミニウム金属膜42の表面に形成されているとともに、分割絶縁層52bの上方において結晶構造が不連続となっている境界82Gを有するニッケルを主成分とするニッケル層72を備える半導体装置。

(もっと読む)

露光用マスク及びフォトレジストパターンの形成方法

【課題】複数回の露光やベークを実施することなく、一回の露光処理で容易に逆テーパー形状のレジストパターンを得ることが可能な露光用マスクならびに当該マスクを用いたポジ型フォトレジストパターンの形成方法を提供する。

【解決手段】外周部が遮光領域101で区画された光透過領域102を有し、ポジ型フォトレジスト207への選択的露光を行う露光システムにおいて用いる、露光用マスク100であり、前記マスク100の光透過領域内の一部に、ポジ型フォトレジストの塗布厚み以下の幅を有するダミー遮光領域103、105が、少なくともレジストパターンとして逆テーパー形状を形成したい部分に対応する前記外周部遮光領域の縁101a、b、c、dのいずれかの縁の近傍に少なくとも1個以上形成されている露光用マスク。

(もっと読む)

膜スタックをエッチングするための方法およびシステム

膜スタックを設け、複数のドライ・エッチング・プロセスを用いてこの膜スタック中にフィーチャを形成するための方法およびシステムが記載される。膜スタック中に形成されたフィーチャは、約25nm以下の限界寸法を有するゲート構造を含み得る。この限界寸法は、4つのマスク層を用いてポリシリコン層中に形成できる。  (もっと読む)

(もっと読む)

液晶用マトリクス基板およびその製造方法

【課題】 表示品位が高く、周辺回路とのコンタクト性に優れた液晶表示装置を構成するマトリックス基板およびその製造方法を実現する。

【解決手段】 複数の液晶セルを形成するためのマトリクス回路が形成されている液晶用マトリクス基板において、液晶パネルを組み立てるときに貼り合わせ面となる表面に島状に、第1の導電材からなる絵素電極12と、第2の導電材からなる端子電極13とを形成する。このとき、第1の導電材は、第2の導電材よりも透過性が高く、かつ、導電性が低いものを使用する。

(もっと読む)

積層構造体、積層構造体を用いた電子素子、これらの製造方法、電子素子アレイ及び表示装置

【課題】 印刷法のような低コストかつ材料使用効率の高い方法が適用でき、簡便に微細なパターンの形成が可能であって、かつ、パターン形成以外に高付加価値機能を有し、より高移動度の半導体層を有する積層構造体を廉価に提供する。

【解決手段】 エネルギーの付与によって臨界表面張力が変化する材料を含み、より臨界表面張力の大きな高表面エネルギー部3とより臨界表面張力の小さな低表面エネルギー部4との少なくとも臨界表面張力の異なる2つの部位を有する濡れ性変化層2と、この濡れ性変化層2に対して高表面エネルギー部3の部位に形成された導電層5と、濡れ性変化層2に対して少なくとも低表面エネルギー部4の部位に接して設けられた半導体層6と、を有し、濡れ性変化層2は、メチレン基を含み、側鎖に疎水性基を有する高分子材料を含むように積層構造体1を構成した。

(もっと読む)

半導体装置

【課題】光近接効果に起因するトランジスタのゲート長ばらつきを抑制しうる半導体装置を提供する。

【解決手段】半導体装置は、P型拡散領域,N型拡散領域及び素子分離領域に跨って形成され、拡散領域上に位置するゲート電極部G21a〜G21cと、素子分離領域上に位置するゲート配線部G22a〜G22cとを有する複数のゲートポリシリコン膜G20a〜G20cを備えている。そして、層間絶縁膜を貫通して、ゲート配線部G22a〜G22cに接続されるゲートコンタクトC23a〜C23cと、各ゲートコンタクトC23a〜C23cに接続される配線M21とが設けられている。ゲートコンタクトC23a〜C13cの径Rは、ゲートポリシリコン膜G20のゲート長Lよりも大きい。

(もっと読む)

161 - 180 / 189

[ Back to top ]