Fターム[4M104DD62]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | 露光 (189)

Fターム[4M104DD62]に分類される特許

41 - 60 / 189

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

感光性塗布型電極材料を用いたTFTの製造方法

【課題】従来の電極方法であるフォトリソグラフィ、マスクスパッタリングは、工程の簡略化、材料使用効率、コスト、多様な基板サイズに対応において解決するには困難な課題があり、インクジェット方式では高精細度なパターンが得られないという課題がある。

【解決手段】感光性塗布型電極材料を用いて、所望の電極パターンニングを行う。本発明による電極作成工程において、コストメリットがある拡散光を光源とするランプを用いて第1の露光と第1の露光よりも大きい露光量をもった第2の露光を施すことで、所望の電極パターンを得ることができる。拡散光を用いた2回露光プロセスによって、例えばTFT作成において従来の方法では解決できない材料使用効率、コスト、多様な基板サイズに対応という課題かつ、インクジェット方式では解決できない高精細パターニングを解決するものである。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】工程を追加せずに、アライメントマークの形成領域におけるゲート電極膜の残渣を低減する。

【解決手段】半導体装置の製造方法は、アライメントマーク10を有する第1領域R1と、抵抗体40が形成される第2領域R2と、ゲート電極15が形成される第3領域R3と、を主面1aに有する基板の主面1a上に、金属材料を含有するゲート電極膜11を形成する工程を有する。更に、第1及び第2領域R1、R2のゲート電極膜11を等方性エッチングにより除去する工程を有する。更に、ゲート電極膜11を除去した第2領域R2と、第3領域R3と、に導電膜(ポリシリコン膜13)を成膜する工程を有する。更に、導電膜を成膜する工程の後に、基板の主面1a上にフォトレジスト膜を形成し、アライメントマーク10をアライメントに用いて所定のパターンをフォトレジスト膜に転写する工程を有する。

(もっと読む)

パターン画像の形成方法

【課題】有機薄膜トランジスタソース/ドレイン電極などに適する厚みが均一で高精細なパターン画像の形成方法を提供する。

【解決手段】特定の構造単位を有するポリイミド前駆体及び該ポリイミド前駆体を脱水閉環して得られるポリイミドからなる群より選ばれる少なくとも一種の重合体を含むパターン画像下層膜形成液を基板上に塗布し、乾燥、焼成することでパターン画像下層膜を得る工程と、

得られるパターン画像下層膜に紫外線を照射しパターン画像下層膜の濡れ性を変化させる工程と、

パターン画像形成液が付着したブレードと上記パターン画像下層膜とを相対的に移動させることにより、上記パターン画像下層膜の紫外線照射領域に上記パターン画像形成液を塗布させ、乾燥する工程と、

を有することを特徴とする。

(もっと読む)

半導体装置、光学装置及びセンサ装置

【課題】ソース電極及びドレイン電極と有機半導体材料層との間の接触抵抗を低下させることができ、これを簡便な製造プロセスで実現できる半導体装置、光学装置及びセンサ装置を提供すること。

【解決手段】ソース電極5と、ドレイン電極6と、少なくともこれらの電極間に設けられた有機半導体材料層7とを有し、有機半導体材料層7を介してソース電極5とドレイン電極6との間で電荷を移動させるように構成された有機電界効果トランジスタにおいて、ソース電極5及びドレイン電極6が、導電性高分子材料と電荷移動錯体との混合物からなる、有機電界効果トランジスタ1a。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、疎水化処理を要することなく、フォトリソグラフィー技術による酸化シリコン膜のパターニングが可能な半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明は、基板上に形成された酸化シリコン膜上に機能層を形成する機能層形成工程と、上記機能層上に第1フォトレジストを塗布し、フォトリソグラフィー法により上記機能層および上記酸化シリコン膜をパターニングし、上記第1フォトレジストを除去する第1パターニング工程と、パターニングされた上記機能層上に第2フォトレジストを塗布し、フォトリソグラフィー法により上記機能層をさらにパターニングし、上記第2フォトレジストを除去する第2パターニング工程とを有し、上記機能層と上記第1フォトレジストおよび上記第2フォトレジストとの接触角が20度以下であることを特徴とする半導体素子の製造方法を提供する。

(もっと読む)

薄膜トランジスタとその製造方法、及びアクティブマトリックス基板

【課題】電極/配線の材料としてAl及び/又はその合金が用いられており、オフリーク電流が小さく良好な素子特性を有する薄膜トランジスタ(TFT)を提供する。

【解決手段】TFT101は、基板1上にゲート電極2とゲート絶縁膜3とチャネル層として機能する半導体膜4とを備え、半導体膜4上にソース電極6とドレイン電極7とが互いに離間して設けられたものであり、ソース電極6及びドレイン電極7は、アルミニウム及び/又はその合金を主成分とする少なくとも1層のアルミニウム(合金)膜を含む単層膜又は積層膜からなり、半導体膜4の表面のソース電極6及びドレイン電極7の間の領域8に、電気的に不活性な少なくとも1種のアルミニウム化合物9が形成されたものである。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

導電膜及びその製造方法、並びにタッチパネル及び集積型太陽電池

【課題】絶縁性が著しく改善でき、高透過性、低抵抗である導電膜及び簡易にファインなパターンを形成できる導電膜の製造方法、並びに筆圧耐久性及び可撓性が向上したタッチパネル、及び変換効率が向上した集積型太陽電池の提供。

【解決手段】基材と、該基材上に少なくとも導電性繊維を含む導電層とを有してなり、前記導電層がパターン形成されており、パターンエッジ粗さが5μm以下である導電膜となる。該導電層が分散媒を含有し、該分散媒の合計含有量Aと、導電性繊維の含有量Bとの質量比(A/B)が0.1〜5.0である態様、該導電性繊維が、平均短軸長さが100nm以下であり、かつ平均長軸長さが5μm以上である態様などが好ましい。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート電極の形成工程におけるフォトレジスト層を露光した際に、露光不良によりレジスト残渣が発生しないようにすること。

【解決手段】本発明の電界効果トランジスタ100は、半導体基板1上にゲート電極を備えた電界効果トランジスタで、半導体基板1上に設けられた誘電体膜2と、この誘電体膜2の開口部に設けられたフット部8と、このフット部8上及び誘電体膜2上に設けられたヘッド部9とを備え、誘電体膜の膜厚t1が、0.9k×λ/2|n1−n2|<t1<1.1k×λ/2|n1−n2|(ただしkは自然数であり、屈折率n1は所定の波長λを有する露光光に対する誘電体膜の屈折率n1(>2.1)、屈折率n2はフォトレジスト層の屈折率)である。

(もっと読む)

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

半導体装置

【課題】並列に並ぶゲートパターンを有する半導体装置において、ゲートパターンのレイアウトを工夫することによって、光近接効果を補正しつつ、集積度を向上させる。

【解決手段】並列に並ぶゲートパターン21,22の端部と、並列に並ぶゲートパターン23,24の対向端部とにおいて、ゲートパターン21の端部はゲートパターン22の端部よりもゲートパターン23,24の方に突き出ており、ゲートパターン24の対向端部はゲートパターン23の対向端部よりも、ゲートパターン21,22の方に突き出ている。引っ込んでいる方の、ゲートパターン22の端部およびゲートパターン23の対向端部について、仕上がり形状において後退が生じない程度に、補正量を大きく設定することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

半導体素子、半導体装置及びそれらの作製方法

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

半導体発光素子の製造方法および半導体積層基板

【課題】1枚の基板から得られる複数の半導体発光素子の構造のばらつきを抑制することのできる半導体発光素子の製造方法および半導体積層基板を提供する。

【解決手段】サファイアウエハWAの一方の面に、逐次露光方式を用いて凸部および平面を有する凸部形成領域SAと、位置決め用のマークMを有するマーク形成領域MAとを形成する。その後、サファイアウエハWAの一方の面にIII族窒化物半導体層を積層した半導体積層基板を作成し、マークMの形成位置の読み取り結果に基づいて、逐次露光方式を用いて複数の半導体発光素子に対応した電極構造を形成する。

(もっと読む)

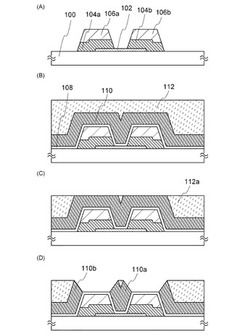

薄膜トランジスタ表示板及びその製造方法

【課題】銅を含む層とチタニウムを含む層とをエッチングする時に、非過水系のエッチング液を使用して工程の安定性を向上させる。

【解決手段】本発明は、薄膜トランジスタ表示板に対する発明であって、より詳細には、銅(Cu)とチタニウム(Ti)とをそれぞれ含む二重層配線に形成される薄膜トランジスタ表示板に関し、構造的にはチタニウムを含む層が銅を含む層より幅が広くて、チタニウムと銅とを共にエッチングする段階と、別にエッチングする段階とを含めて製造することを特徴とする。また、ゲート絶縁膜に段差が形成されている。

(もっと読む)

液晶表示装置の製造方法

【課題】本発明は、エッチングレジストを形成するためのフォトリソグラフィの工程を減らすことを目的とする。

【解決手段】ゲート電極30、ドレイン電極52及びソース電極54を含む薄膜トランジスタを形成する。薄膜トランジスタを覆う第1絶縁膜44を形成する。第1絶縁膜44上に第2絶縁膜46を形成する。第2絶縁膜46上に透明導電膜170を形成する。透明導電膜170上にフォトリソグラフィによってパターニングされたエッチングレジスト50を形成する。エッチングレジスト50を介して、透明導電膜170を第1エッチングによってパターニングして第1透明電極70を形成する。エッチングレジスト50を介して、第2絶縁膜46の第1透明電極70から露出する表面に対して行う第2エッチングによって第2絶縁膜46にドレイン電極52及びソース電極54の一方の上方に位置する貫通穴40を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極のテーパ形状の傾斜度を緩やかにすることができるようにして、ゲート電極の破損が起こらないようにしながら、確実にさらなる微細化を実現した下部電極を形成できるようにする。

【解決手段】ソース電極2及びドレイン電極3を有する半導体領域1上に絶縁膜4を形成し、絶縁膜4上に複数のレジスト層5,6,7を含む積層レジスト8を形成し、積層レジスト8の最下層以外のレジスト層6,7に開口9を形成し、最下層のレジスト層5にリフロー用開口10を形成し、熱処理を施してリフロー用開口10に露出している最下層のレジスト層5の一部PTcをリフローさせ、リフローさせることによって最下層のレジスト層5の表面に形成された傾斜面11に連なるように最下層のレジスト層5に第1ゲート下部開口12Aを形成し、開口9、傾斜面11及び第1ゲート下部開口12Aの形状に応じた形状を持つゲート電極13を形成する。

(もっと読む)

半導体装置の作製方法

【課題】 レジスト材料の利用効率を向上させて、作製コストの削減を目的としたレジス

トパターンの作製方法、レジストパターンの除去方法、半導体装置の作製方法を提供する

ことを課題とする。

【解決手段】 本発明は、減圧下で、被加工物上に、感光剤を含む組成物を吐出してレジ

ストパターンを形成するステップを有することを特徴とする。また、前記レジストパター

ンをマスクとして前記被加工物をエッチングするステップ、若しくは、前記レジストパタ

ーンに、フォトマスクを介して前記感光剤の感光波長域の光を照射するステップ、前記レ

ジストパターンをマスクとして前記被加工物をエッチングするステップ、前記被加工物上

の前記レジストパターンを除去するステップを有することを特徴とする。

(もっと読む)

41 - 60 / 189

[ Back to top ]