Fターム[4M104DD72]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | パターニング用マスク (645) | エッチングストッパ (103)

Fターム[4M104DD72]に分類される特許

81 - 100 / 103

半導体装置製造方法

【課題】光検出器の受光部上の配線構造層等をエッチングして開口部を形成する際の工程を簡素化する。

【解決手段】半導体基板60上に、シリコン窒化膜86をCVD法等により形成した後、配線構造層を含む積層構造88を形成する。積層構造88の上に、受光部上に開口を有したフォトレジスト膜122を形成し、これをエッチングマスクとして、積層構造88に対するエッチング処理を行う。このエッチングは、シリコン窒化膜に対する層間絶縁膜の選択比が確保されるような種類・条件として、当該エッチング処理においてシリコン窒化膜86をエッチングストッパとして機能させる。開口部116の底部に露出したシリコン窒化膜86は反射防止膜を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト構造形成時に生じ得る抵抗増加や導通不良の発生を抑制する。

【解決手段】ゲート電極1の上層に第1,第2の応力膜4,5を張り分けてからそのゲート電極1に通じるコンタクトホールを形成してコンタクト電極を形成する際、そのコンタクトホール形成領域9を第1の応力膜4側にレイアウトする。第1,第2の応力膜4,5の境界とコンタクトホール形成領域9をずらしてレイアウトすることにより、コンタクトホール形成時のシリサイド領域2やゲート電極1へのエッチングダメージや開口不良の発生を効果的に抑制することが可能になる。これにより、低抵抗コンタクト構造を有する、高性能の半導体装置が実現可能になる。

(もっと読む)

半導体装置の微細パターン形成方法

【課題】パターンのCD変異を減らすことが可能な半導体素子の微細パターン形成方法を提供すること。

【解決手段】被エッチング層を有する半導体基板上に第1ポリシリコン膜28とバッファ酸化膜29を順次形成し、さらに第2ポリシリコン膜30、研磨停止膜31及び第1酸化膜32が積層された構造のハードマスクを形成する。ハードマスクの側面に窒化膜スペーサ35を形成し、全体に第2酸化膜36を形成する。第2酸化膜、窒化膜スペーサ及び第1酸化膜を研磨し、前記研磨停止膜と窒化膜スペーサを除去する。第2ポリシリコン膜と第2酸化膜をマスクとしてバッファ酸化膜をエッチングする。第2酸化膜を除去し、第2ポリシリコン膜とバッファ酸化膜をマスクとして第1ポリシリコン膜をエッチングし、第2ポリシリコン膜を除去する。バッファ酸化膜と前記第1ポリシリコン膜をマスクとして被エッチング層をエッチングする。

(もっと読む)

接続部構造及びその製造方法

【課題】シリサイド上に接続孔を形成する際のエッチングで、高抵抗の変質層が発生することを防止する。

【解決手段】 基板中もしくは基板上に導電層を形成する。次に、導電層上を含む基板上に第1の金属膜を形成する。次に、基板に対して熱処理を行なって第1の金属膜と導電層とを反応させ、導電層上に選択的にシリサイド膜を形成する。次に、選択CVD法によりシリサイド膜上のみに第2の金属膜を形成する。次に、第2の金属膜上を含む基板上に絶縁膜を形成する。次に、絶縁膜の所定領域を開口して、第2の金属膜に到達するコンタクトホールを形成する。次に、コンタクトホール内を洗浄して、コンタクトホール底面における第2の金属膜表面に形成された変質層を除去する。

(もっと読む)

異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造および方法

【課題】異なる高さのコンタクト線を有する高密度MOSFET回路を製造するための構造、方法などを提示すること。

【解決手段】このMOSFET回路は、コンタクト線(500、1300)と、コンタクト線(500、1300)の近くに位置するゲート(310、1210)とを含む。コンタクト線(500、1300)は、ゲート(310、1210)の高さよりも低い高さを含む。このMOSFET回路はさらに、ゲート(310、1210)の近くに位置するゲート・スペーサ(710、715、1610、1615)を含み、コンタクト線(500、1300)とゲート(310、1210)との間のコンタクト線(500、1300)の近くに位置するコンタクト線スペーサを含まない。

(もっと読む)

プラズマエッチング方法

【課題】高誘電率絶縁体からなる絶縁材料層上に形成した遷移金属元素を含む電極材料層に対し高選択比でエッチングを施すことのできるエッチング技術を提供する。

【解決手段】遷移金属元素を含む電極材料層107および高誘電率絶縁体108からなる絶縁材料層の積層体を備えた試料を真空処理容器内に設置した下部電極上に配置し、前記真空処理容器内に処理ガスを導入し、前記真空処理容器内に高周波電力を供給して前記導入した処理ガスをプラズマ化して前記試料表面にエッチング処理を施すプラズマエッチング処理方法において、前記電極材料層をエッチングするとき、処理ガスとしてHClガスを供給する。

(もっと読む)

半導体装置の製造方法

【課題】ゲートリーク電流の発生や短絡等のような特性の劣化が抑制された半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、位相シフタを備える露光用マスクを用いてレジスト膜を露光現像することにより、前記レジスト膜をパターニングする工程と、第2レジスト膜118をマスクとし第2の膜(シリコン酸化膜108)をエッチングストッパとして第3の膜(多結晶シリコン膜)を選択的にドライエッチングし、第3の膜を第1のパターンに加工する工程と、前記第2の膜をエッチングストッパとして第3の膜(多結晶シリコン膜110a)をさらにドライエッチングし、前記第3の膜の一部を除去して前記第3の膜を第2のパターンに加工する工程と、前記第2のパターンに加工された第3の膜(多結晶シリコン膜110b)をマスクとして用いる工程と、を含む。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】シリコン窒化膜が半導体基板に近接しないようにした半導体集積回路装置と、コンタクトホールの加工を容易にする半導体集積回路装置の製造方法を提供する。

【解決手段】素子分離領域4に囲まれたシリコン基板21上に、シリコン窒化膜をエッチングストッパーとして用いた自己整合コンタクトプロセスによって形成されたコンタクトホールに埋め込まれ、拡散層2,3に電気的に接続されたコンタクトプラグ33を有する半導体集積回路装置であって、前記拡散層2、3の露出面に選択エピタキシャル成長により形成された、各ゲート絶縁膜22の前記拡散層側端部と接するシリコン層28を形成し、各ゲート電極22と前記シリコン層28との間にシリコン酸窒化膜またはシリコン酸化膜からなる絶縁膜27’が前記ゲート絶縁膜22に接して埋め込まれており、シリコン窒化膜26,29’,32が絶縁膜27’によりシリコン基板21と隔離されている。

(もっと読む)

SF6ベースの化学反応を用いてドープトシリコンをエッチングするプロセス及びシステム

ドープトシリコン層を介して異方性ドライエッチングを行う方法及びシステムが開示される。プロセス化学はSF6及びフッ化炭素ガスを含む。フッ化炭素ガスは、x及びyを1以上の整数として、CxFy、例えばC4F8、を含む。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 トレンチゲート構造の半導体装置において、トレンチ上方コーナ部に結晶欠陥が生じることを抑制する。また、半導体装置の小型化が可能となる構造の半導体装置およびその製造方法を提供する。

【解決手段】 ゲート電極7の形状を、その断面がT字となるように、トレンチ5の内部から半導体基板4の表面に至って形成された形状とし、ソースとなるN+型領域15をトレンチ5から離れた位置であって、ゲート電極7における半導体基板4の表面上に位置する部分7aの下に配置した構造とした場合、ゲート電極7の上方部7aのトレンチ側壁5aに対するオーバラップ量を0.3μm以上とする。また、ゲート電極7とゲート配線10とを電気的に接続させるためのコンタクトホール18を、層間絶縁膜8のうち、トランジスタ領域内におけるトレンチ5の上方の位置に形成する。

(もっと読む)

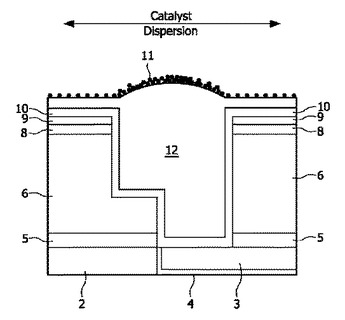

半導体デバイス用構造体の製造方法

本発明は、半導体デバイス用デュアルダマシン構造を製造する方法に関する。基板中に形成されたトレンチまたはバイア内の、拡散バリア層の堆積の間中、ハロゲン系前駆物質が使用される。前記堆積からの残留ハロゲンは、前記バリア層上に残ることができ、前記トレンチまたはバイアを充填するために、前記バリア層上に位置する金属層の成長を触媒するのに用いられる。  (もっと読む)

(もっと読む)

微細構造の製造方法

【課題】微細パターンを歩留まりよくエッチングできる微細構造の製造方法を提供する。

【解決手段】製造方法は、(a)被エッチング膜の上に、下層ハードマスク膜、上層ハードマスク膜を積層したエッチング対象物を準備し、(b)エッチング対象物の上にレジストパターンを形成し、(c)レジストパターンをマスクとして、上層ハードマスク膜をエッチングして上層ハードマスクを形成し、(d)工程(c)の後、レジストパターンを除去し、(e)工程(d)の後、上層ハードマスクをエッチングして細くし、(f)工程(e)の後、細くした上層ハードマスクをマスクとして下層ハードマスク膜をエッチングして下層ハードマスクを形成し、(g)上層ハードマスク、下層ハードマスクをマスクとして、被エッチング膜をエッチングするにあたり、上層ハードマスク膜は下層ハードマスク膜よりもレジストパターンをマスクとしたエッチングが容易な膜を用いる。

(もっと読む)

半導体素子のゲートパターン及びその形成方法

【課題】ゲートパターン間に埋め込まれる層間絶縁膜の埋め込み性及びランディングプラグ形成物質の埋め込み性を向上させることができる半導体素子のゲートパターン及びその形成方法を提供すること。

【解決手段】半導体素子のゲートパターンは、基板110に形成されたトレンチ112の内面及び基板110の表面に形成されたゲート絶縁膜114と、トレンチ112が形成されていない領域におけるゲート絶縁膜114の上面より突出しないように、トレンチ112に埋め込まれた第1ゲート電極層116Aと、一部分が第1ゲート電極層116Aと接触するように、第1ゲート電極層116A上に形成された第2ゲート電極層120Aとを備えている。

(もっと読む)

半導体装置の作製方法

【課題】基板を切断する工程の歩留まりを向上する方法を提供する。

【解決手段】基板11にレーザービームを照射して、絶縁層や導電層を積層した複数の層に達する溝32を形成する。ここでレーザビーム照射による溝32は、基板中のある部分の分子結合を切断し、光分解し、気化して蒸発させるアブレーション加工で形成する。その後さらに溝にレーザービームを照射して基板を切断する。

(もっと読む)

ゲート電極積層およびゲート電極積層を用いる方法

【課題】エッチングの容易なポリシリコン−メタル積層で構成されるゲート電極構造を提供する。

【解決手段】少なくとも1層のポリシリコン3と少なくとも1層のポリSi1−xGex材料の層4とを有するゲートコンダクタを備える半導体デバイスの基板上のゲート電極積層構造であり、ポリシリコン3とポリSi1−xGex材料の層4のエッチングにより、終点検出が可能であるため、上記構造を効果的にエッチングすることができる。

(もっと読む)

微細パターン形成方法

【課題】

微細加工が可能な微細パターン形成方法を提供する。

【解決手段】

パターニングされたマスク層76の側壁にプラズマ反応生成物を堆積させてマスク層76のパターン幅を広げる第1工程と,パターン幅が広げられたマスク層76をマスクとして,第1の被エッチング層74をエッチングする第2工程と,エッチングされた第1の被エッチング層74に生じたスペース80にマスク材81を埋め込む第3工程と,スペース80に埋め込まれたマスク材を残して,第1の被エッチング層74をエッチングする第4工程と,残されたマスク材81をマスクとして,第2の被エッチング層72をエッチングする第5工程とを有することを特徴とする,微細パターン形成方法である。

(もっと読む)

炭化珪素においてビアを形成する方法、及び得られるデバイスと回路

望ましくないインダクタンスを引き起こし得るワイヤーボンディングを排除する、炭化珪素基板上で集積回路を作製する方法。該方法は、炭化珪素基板の表面上のエピタキシャル層において半導体デバイスを作成し、該エピタキシャル層の最上位表面上においてデバイスのための少なくとも1つの金属コンタクトを作製することを含む。次に、実質的に透明になるまで、基板の反対側の表面を研削及び研磨する。次に、該方法は、炭化珪素基板の該研磨された表面をマスキングして、エピタキシャル層の最上位表面上にあるデバイス金属コンタクトとは反対側に存在する少なくとも1つのビアのために所定の位置を画成する工程;所望のビアをエッチングする工程を含む。第1のエッチング工程は、エッチングがエピタキシャル層に達するまで、所望のマスキングされた場所の炭化珪素基板を貫通させてエッチングする。第2のエッチング工程は、エピタキシャル層を貫通させてデバイスコンタクトまでエッチングする。最後に、ビアをメタライズして、基板の第一表面から、金属コンタクト及び基板の第二表面上にあるデバイスに至る導電経路を提供する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 エッジラフネスを解消してパターンを形成する。

【解決手段】 基板上に、被加工膜を形成形成し、第1マスクの材料膜である第1材料膜を形成する。そして、第1材料膜をエッチングして、第1マスクを形成する。更に、第1マスク表面を含む基板全面に、第2マスクの材料膜である第2材料膜を形成した後、第1マスクの側面に第2材料膜を残すようにして、第2材料膜をエッチングして、第2マスクを形成する。その後、第1マスク及び第2マスクをマスクとして、被加工膜をエッチングしてパターンを形成する。

(もっと読む)

半導体装置

【課題】低抵抗、且つ高耐熱性を有するゲート電極またはゲート配線を備えた高性能な半導体装置を実現する。

【解決手段】ゲート電極またはゲート配線を三層以上の積層構造とし、例えば、第1の導電層106a/第2の導電層106b/第3の導電層106cを形成する。さらに、第2の導電層の幅は、第1の導電層及び第3の導電層の幅よりも狭いことを特徴とする。そして第1の導電層及び第3の導電層は高融点金属でなる。これにより高性能な半導体装置を実現できる。

(もっと読む)

自己整合されたレトログレード外部ベース注入プロファイル及び自己整合されたシリサイドを有するバイポーラ・トランジスタ

【課題】 外部ベース注入部、外部ベース・シリサイド及びエミッタが互いに自己整合された、自己整合型バイポーラ・トランジスタを提供すること。

【解決手段】 基板(10)内のコレクタ(12)と、コレクタの上にある内部ベース(14)と、内部ベースに隣接した外部ベースと、内部ベースの上にあるエミッタ(130)とを含むバイポーラ・トランジスタ、及びトランジスタを形成する方法が開示される。外部ベースは、断面から見たときに、内部ベースと隣接した外部ベース注入領域(82、172、192)を含む。トランジスタは、内部ベースの上の基板上に、エミッタの下部のためのエミッタ・ペデスタル(50)をパターン形成することによって形成される。エミッタ・ペデスタルによって保護されない領域内に、外部ベースが形成される。その後、エミッタ、関連したスペーサ(180)及びシリサイド領域(220)が形成される。シリサイド、外部ベース及びエミッタは、全て互いに自己整合される。

(もっと読む)

81 - 100 / 103

[ Back to top ]