Fターム[4M104DD72]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | パターニング用マスク (645) | エッチングストッパ (103)

Fターム[4M104DD72]に分類される特許

21 - 40 / 103

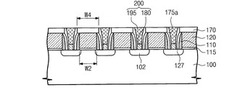

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

トランジスタ及びその作製方法

【課題】スイッチング特性が良好で、且つ信頼性が高いトランジスタを提供する。

【解決手段】例えば、ボトムゲートトップコンタクト構造のトランジスタを作製するに際して、第1の配線層を形成し、該第1の配線層を覆って第1の絶縁膜を形成し、該第1の絶縁膜上に半導体層を形成し、該半導体層上に導電膜を形成し、該導電膜に少なくとも2段階のエッチングを行って第2の配線層を離間させて形成し、前記2段階のエッチングが、少なくとも前記導電膜に対するエッチングレートが前記半導体層に対するエッチングレートより高い条件により行う第1のエッチング工程と、前記導電膜及び前記半導体層に対するエッチングレートが、前記第1のエッチング工程よりも高い条件により行う第2のエッチング工程と、を有する方法によりトランジスタを作製する。

(もっと読む)

半導体装置、半導体集積回路装置及び半導体装置の製造方法

【課題】高耐圧且つ低オン抵抗な半導体装置及びこれを含む半導体集積回路装置を歩留まり良く、安価に提供する。

【解決手段】第1導電型の半導体基板(1)と、前記第1導電型と反対の第2導電型であって前記半導体基板の表面側に形成されたソース領域(11)、低濃度ドレイン領域(12)及び高濃度ドレイン領域(13)と、前記半導体基板上に形成されたゲート絶縁膜(14)と、前記ゲート絶縁膜上に形成されたゲート電極と、を備える半導体装置(10)であって、

前記ゲート電極は、前記低濃度ドレイン領域の少なくとも一部を覆うように形成され、且つ、前記低濃度ドレイン領域の上方において開孔(16)を有することを特徴とする半導体装置。前記低濃度ドレイン領域と高濃度ドレイン領域とは互いに隣接することが好ましい。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数を十分に制御することができ、閾値電圧の変動を抑制した半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10に第1導電型チャネルMOSFETを備える。第1導電型チャネルMOSFETは、例えばPチャネルMOSFETであって、半導体基板10の上に設けられたゲート絶縁膜21と、ゲート電極65とからなる。ゲート電極65は、ゲート絶縁膜21の上に設けられた金属ゲート電極20と、金属ゲート電極20の上に設けられた金属酸化膜24と、金属酸化膜24の上に設けられた金属ゲート電極26と、を含んでいる。

(もっと読む)

置換ゲート構造体を有するFET及びその製造方法

【課題】 マルチゲート型FETの置換ゲート構造体及びマルチゲート型FETの置換ゲート構造体の製造方法を提供する。

【解決手段】 MUGFET及びMUGFETを製造する方法が示される。MUGFETを製造する方法は、複数の活性領域の周りに一時的スペーサ・ゲート(図3の16)を形成することと、複数の活性領域の間を含む、一時的スペーサ・ゲートの上に誘電体材料(18a及び空間20内)を堆積させることとを含む。この方法は、誘電体材料(空間20内)の部分をエッチングして一時的スペーサ・ゲート(16)を露出させることと、一時的スペーサ・ゲートを除去して、活性領域と誘電体材料の残りの部分(18a)との間に空間を残すこととをさらに含む。この方法はさらに、活性領域と誘電体材料の残りの部分(18a)との間の空間(22)及び誘電体材料の残りの部分の上方をゲート材料で充填することを含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート電極部と容量コンタクトプラグとのショートを防止する。

【解決手段】複数のゲート電極部10と該ゲート電極部10間を接続する配線部との上に、耐エッチング膜17を備えたゲートハードマスク20を形成後、前記配線部上の前記耐エッチング膜17を除去する。これにより、CMP処理を経てコンタクトプラグ22を形成し、さらに、エッチングにより容量コンタクトホール24を開口して容量コンタクトプラグ25を形成した場合に、ゲート電極部10と容量コンタクトプラグ25とのショートを防止することができる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ニッケル系メタル・シリサイドとコンタクト用メタル間でのコンタクト抵抗の低抵抗化がホールの微細化に伴って、困難になるという問題がることが、本願発明者の検討により明らかとなった。

【解決手段】本願の一つの発明は、ニッケル系メタル・シリサイドによりソース・ドレイン領域等のシリサイデーションを施したMISFETを有する半導体集積回路装置の製造方法において、プリ・メタル絶縁膜に設けられたコンタクト・ホールにバリア・メタルを形成する前に、シリサイド膜の上面に対して、窒素水素間結合を有するガスを主要なガス成分の一つとして含む非プラズマ還元性気相雰囲気中で、熱処理を実行するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極との短絡を抑えたセルフアラインコンタクトを有する、製造コストの低い半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、それぞれ半導体基板2上に形成され、それぞれゲート電極4a、4bを有し、互いの間のソース・ドレイン領域8aを共有する隣接したトランジスタ1a、1bと、ゲート電極4a上に形成された絶縁膜11aと、ゲート電極4b上に形成された絶縁膜11aよりも厚さの厚い領域を有する絶縁膜11bと、ソース・ドレイン領域8aに接続され、その中心位置がゲート電極4a、4bの間の中心位置よりもゲート電極4b側に位置するSAC14と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

トレンチ金属酸化膜半導体素子及び終端構造の製造方法

【課題】トレンチ金属酸化膜半導体素子及び終端構造を同時に製造するトレンチ金属酸化膜半導体素子及び終端構造の製造方法を提供する。

【解決手段】活性領域にトレンチ金属酸化膜半導体素子を形成するための複数の第1のトレンチ及び終端構造を形成するための第2のトレンチを形成する。次に、半導体基板の全領域にゲート酸化層を形成し、第1のトレンチ及び第2のトレンチに第1の導電材料を埋め込む。エッチバックプロセスを行い、余分な第1の導電材料を除去し、第2のトレンチにスペーサ122を形成するとともに、第1のトレンチのみに導電材料140を残す。次に、第1のトレンチ及び第2のトレンチに導電層間酸化層を形成する。次に、メサ表面115A上のゲート酸化層を除去する。蒸着、リソグラフィック及びエッチングプロセスにより、終端構造酸化層150を形成する。第1の電極160Aを所定の位置に形成する。

(もっと読む)

TFT−LCDアレイ基板、及びその製造方法

【課題】TFT−LCDアレイ基板及びその製造方法に関する。

【解決手段】TFT−LCDアレイ基板の製造方法であって、基板にゲート金属層薄膜を堆積し、ゲート電極とゲート・ラインとのパターンが含まれたパターンを形成するステップ1と、前記ステップ1を完成した基板にゲート絶縁層薄膜と、半導体層薄膜と、TFTチャネル部分の半導体層がエッチングされることを防止する阻止層薄膜とを堆積し、ゲート絶縁層と、半導体層と、阻止層とのパターンが含まれたパターンを形成するステップ2と、前記ステップ2を完成した基板にオーミック接触層薄膜と、透明導電層薄膜と、ソース・ドレイン金属層薄膜と、パッシベーション層薄膜とを堆積し、オーミック接触層と、画素電極と、データ・ラインと、ソース電極と、ドレイン電極と、パッシベーション層とのパターンが含まれたパターンを形成するステップ3と、を備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】金属シリサイド層と窒化シリコン膜の界面に自然酸化膜が残存していると、窒化シリコン膜の成膜後の種々の加熱工程(例えば種々の絶縁膜や導体膜の成膜工程のように半導体基板の加熱を伴う工程)において、金属シリサイド層表面にある自然酸化膜の酸素に起因して、金属シリサイド層が部分的に異常成長してしまう。

【解決手段】本願発明においては、集積回路を構成する電界効果トランジスタのソース・ドレイン上のニッケル・シリサイド等の金属シリサイド膜の上面に対して、不活性ガスを主要な成分とするガス雰囲気中において、実質的にノン・バイアス(低バイアスを含む)のプラズマ処理を施した後、コンタクト・プロセスのエッチング・ストップ膜となる窒化シリコン膜を成膜することにより、金属シリサイド膜の不所望な削れを生じることなく、金属シリサイド膜の上面の自然酸化膜を除去することができる。

を図ることができる。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を有する薄膜トランジスタにおいて、水分などの不純物を混入させずに良好な界面特性を提供することを課題の一つとする。電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】ゲート絶縁層表面に酸素ラジカル処理を行うことを要旨とする。よってゲート絶縁層と半導体層との界面に酸素濃度のピークを有し、かつゲート絶縁層の酸素濃度は濃度勾配を有し、その酸素濃度はゲート絶縁層と半導体層との界面に近づくにつれて増加する。

(もっと読む)

半導体装置の製造方法

【課題】

DRAMの容量を安定化し、メモリセル部と周辺回路部の高低差を小さくして平坦化を容易にする。

【解決手段】

メモリセルトランジスタ上の第1の絶縁膜に第1のコンタクトプラグを埋め込み、エッチング特性の異なる第2、第3の絶縁膜を形成し、第3、第2の絶縁層を貫くコンタクト窓を形成し、シリンダ型蓄積電極を形成し、第2の絶縁膜をエッチングストッパとして第3の絶縁膜を除去し、キャパシタ絶縁膜、導電膜を形成し、パターニングして対向電極を形成し、対向電極に合わせて第2の絶縁膜も除去してメモリセルを形成し、周縁領域において第1の絶縁膜の上に導電膜、絶縁膜を形成し、第2のコンタクトプラグを埋め込む。第2の絶縁膜端部は、第2のコンタクトプラグに接しない。

(もっと読む)

半導体装置及びその作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられた逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体装置の製造方法

【課題】接合リーク電流の低減が図られる半導体装置の製造方法を提供する。

【解決手段】半導体基板1に所定の深さのトレンチが形成され、そのトレンチ5内に分離酸化膜6が形成される。不純物イオンを注入することにより、分離酸化膜6の表面に、分離酸化膜6のエッチング特性とは異なるエッチング特性を有する改質層7が形成される。半導体基板の領域に、トランジスタ等の所定の半導体素子が形成される。半導体基板1上に、エッチングストッパ膜10および層間絶縁膜16が形成される。その層間絶縁膜16およびエッチングストッパ膜に、金属シリサイド9の表面を露出するコンタクトホール16a,16bが形成される。コンタクトホール16a,16b内にプラグ18a,18bが形成される。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜やゲート電極を構成する材料がエッチングされることが無く、高い信頼性を有するゲート電極を有する絶縁ゲート電界効果トランジスタを提供する。

【解決手段】絶縁ゲート電界効果トランジスタは、ソース/ドレイン領域13、チャネル形成領域12、ゲート電極423、ゲート絶縁膜430を備え、ゲート絶縁膜430はゲート絶縁膜本体部430A及びゲート絶縁膜延在部430Bから構成されており、ゲート電極を構成する第1層431はゲート電極の側面部の途中まで薄膜状に形成されており、第2層の外側層432Aは第1層431の上に薄膜状に形成されており、第2層の内側層432Bは第2層の外側層で囲まれた部分を埋め込んでおり、第3層の外側層433Aは第2層の内側層、外側層、ゲート絶縁膜延在部を覆い、ゲート電極の頂面まで薄膜状に形成されており、第3層の内側層433Bはゲート電極の残部を占めている。

(もっと読む)

半導体装置およびその製造方法

【課題】MONOS型のゲート電極を有するメモリセルと、通常のMOSトランジスタの各ゲート電極を同時に加工できるようにする。

【解決手段】メモリセル領域のゲート電極Gは、シリコン基板1上にゲート絶縁膜4、トラップ膜5、ブロック膜6、電極膜7が積層されている。周辺回路領域のゲート電極GPは、シリコン基板1上にゲート絶縁膜4、多結晶シリコン膜9、電極膜7が積層されている。また、多結晶シリコン膜9中には、下層側にシリコン窒化膜10、上層側にシリコン酸化膜11が直接接触しないように形成されている。ゲート一括加工時に、電極膜7をエッチングするときにシリコン酸化膜11がストッパとなり、ブロック膜6加工時にシリコン窒化膜10がストッパとなり、トラップ膜5加工時に多結晶シリコン膜9がストッパとなり、シリコン基板1がダメージを受けるのを防止できる。

(もっと読む)

21 - 40 / 103

[ Back to top ]