Fターム[4M104DD84]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 固相反応 (1,946) | シリサイド化 (1,636)

Fターム[4M104DD84]に分類される特許

101 - 120 / 1,636

半導体装置

【課題】動作特性に対する信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコンを含む基板7と、前記基板7上に設けられた積層体6と、を有する半導体装置1であって、前記積層体6は、少なくとも前記積層体6の側壁の前記基板側にフッ素を含む抑制領域13を有している。前記抑制領域13は、基板7上に設けられた絶縁膜2の前記側壁側に設けられ、フッ素濃度は、チャネル領域11のフッ素濃度よりも高い。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極同士の間の突合わせ部を挟むように形成されたコンタクトプラグ同士が、当該突合わせ部の絶縁膜内に形成されたボイドを介してショートすることを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】本発明は、製造プロセスが煩雑でなく、かつ高い絶縁耐力を有する炭化珪素半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の炭化珪素半導体装置の製造方法は、(a)第1導電型の炭化珪素半導体よりなる下地であるSiC基板1を準備する工程と、(b)SiC基板1上において、素子領域を囲むリセス構造4を、レジストパターン3を用いて形成する工程と、(c)工程(b)の後、レジストパターン3を介した不純物注入により、リセス構造4内のリセス底面及びリセス側面の面内に、第2導電型の不純物層としてのイオン注入層6を形成する工程とを備え、工程(c)は、斜め回転イオン注入により不純物注入を行う工程である。

(もっと読む)

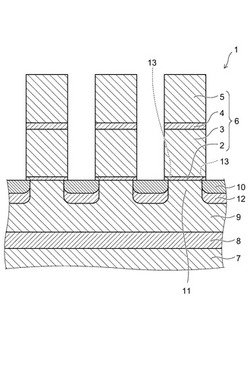

トレンチゲート型半導体装置

【課題】本発明は、アバランシェ耐量と主耐圧を向上させることができるトレンチゲート型半導体装置を提供することを目的とする。

【解決手段】本願の発明に係るトレンチゲート型半導体装置は、基板と、該基板上の第1導電型のエピタキシャル成長層と、該エピタキシャル成長層上の第2導電型の拡散層と、該拡散層を貫通し、先端が該エピタキシャル成長層に達するトレンチゲートと、該トレンチゲートの先端に接するように該エピタキシャル成長層に形成された、該エピタキシャル成長層よりもキャリア濃度の低い、第1導電型の低キャリア濃度部と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】信頼性を犠牲にすることなく、オン抵抗を低減することができるトレンチゲート型の半導体装置を提供する。

【解決手段】半導体装置1は、ドレイン領域21と、ドレイン領域21に積層されたチャネル領域20と、チャネル領域20に積層されたソース領域16とを有するシリコン半導体層からなる活性領域30を含む。半導体装置1は、さらに、ソース領域16からチャネル領域20を貫通してドレイン領域21に至るトレンチ15内に埋め込まれたゲート導体(ポリシリコンゲート)26と、ソース領域16に電気的に接続されたソース電極4とを含む。ソース電極4は、ソース領域16に接するように形成され、ソース領域16との界面がシリサイド化された密着層41を有する。密着層41は、膜厚が150Å以下の金属層からなる。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】LDMOSと、LDMOSのソース領域と電気的に接続されるソースプラグP1Sと、ソースプラグP1S上に配置されるソース配線M1Sと、LDMOSのドレイン領域と電気的に接続されるドレインプラグP1Dと、ドレインプラグP1D上に配置されるドレイン配線M1Dと、を有する半導体装置のソースプラグP1Sの構成を工夫する。ドレインプラグP1Dは、Y方向に延在するライン状に配置され、ソースプラグP1Sは、Y方向に所定の間隔を置いて配置された複数の分割ソースプラグP1Sを有するように半導体装置を構成する。このように、ソースプラグP1Sを分割することにより、ソースプラグP1SとドレインプラグP1D等との対向面積が低減し、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置とその製造方法

【課題】配線加工時のエッチングレートの極端な上昇を抑え、プロセスを安定化させる。

【解決手段】炭化珪素基板1上に形成された炭化珪素層20の上に、ソース電極8、ゲート電極9、層間絶縁膜10、層間絶縁膜10上に形成されたソース電極上部配線11およびゲート電極上部配線12とが形成され、ソース電極上部配線11とゲート電極上部配線12の下には、これらの上部配線を構成する金属が炭化珪素層20に拡散することを抑制するためのバリアメタル16が形成されている。層間絶縁膜10には、炭化珪素層20上に形成されたソース電極8およびゲート電極9に到達するようにコンタクトホール13、15が形成されており、バリアメタル16はコンタクトホール内の電極と上部配線との界面、層間絶縁膜10の側壁と上部配線との界面、および側壁の上端部近傍と上部配線との界面にのみ形成されている。

(もっと読む)

レーザアニール方法及びレーザアニール装置

【課題】高エネルギ効率でレーザアニールを行う方法及び装置を提供する。

【解決手段】(a)不純物がイオン注入により添加されたSiC基板を準備する。(b)SiC基板に、炭酸ガス(CO2)レーザ発振器から出射された反射率の低い9μm〜10.3μmの範囲内のいずれかの波長のレーザビームを照射して、SiC基板に添加された不純物を活性化させる。

(もっと読む)

半導体装置

【課題】集積回路の動作速度の向上に有利な技術を提供する。

【解決手段】n型トランジスタおよびp型トランジスタがシリコンの(551)面に形成された半導体装置において、前記n型トランジスタの拡散領域に接触するシリサイド層の厚さが前記p型トランジスタの拡散領域に接触するシリサイド層の厚さよりも薄い。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】簡単な工程でニッケル含有シリサイドを形成する。

【解決手段】シリコン基板を用いた場合であって、ゲート絶縁膜、ゲート電極、ゲート電極側面のサイドウォールを形成し、不純物イオンをドープしてソース領域及びドレイン領域を形成し、表面酸化膜を除去し、シリコン基板を450℃以上に加熱しながら、ニッケル含有膜を10nm〜100nmの膜厚で形成することにより、ソース領域、ドレイン領域、及びゲート電極上にニッケル含有シリサイドを形成することができる。その後、未反応のニッケルを除去する。

(もっと読む)

半導体装置

【課題】本発明は、高電界での耐圧を確保でき、かつ絶縁破壊を抑制できる終端構造を有する半導体装置の提供を目的とする。

【解決手段】本発明にかかる半導体装置は、ドリフト領域2表面において、平面視でSBD電極5を囲むように形成された、リセス構造3と、リセス構造3底面内に形成され、SBD電極5と接続された、ガードリング注入層4と、リセス構造3に沿って、少なくともリセス構造3を覆って形成された、保護膜7と、保護膜7に沿って、保護膜7上に形成された、半絶縁膜20とを備え、半絶縁膜20は、リセス構造3が囲む領域の内側においてSBD電極5と接続される接続部21と、リセス構造3が囲む領域の外側においてドリフト領域2と接続される接続部22とを備える。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

半導体装置

【課題】十分なチャネル移動度と製造コストの低減とを両立することが可能な半導体装置を提供する。

【解決手段】MOSFET100は、{0001}面に対するオフ角が50°以上65°以下である主面1Aを有する炭化珪素基板1と、主面1A上に形成された活性層7と、活性層7上に接触して形成されたゲート酸化膜91と、活性層7においてゲート酸化膜91と接触する領域を含むように形成され、導電型がp型であるp型ボディ領域4と、p型ボディ領域4内において活性層7の炭化珪素基板1とは反対側の主面を含むように形成され、導電型がn型であるn+領域5と、活性層7上にn+領域5と接触するように形成されたソースコンタクト電極92とを備え、p型ボディ領域4におけるp型不純物密度は5×1017cm−3以上であり、ソースコンタクト電極92とp型ボディ領域4とは直接接触している。

(もっと読む)

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMセルとロジックを混載したLSIデバイスにおけるアスペクト比の大きいコンタクト構造において、素子分離絶縁膜および不純物拡散層のオーバエッチングを抑制して、接合リークを抑制することを課題とする。

【解決手段】周辺MOSトランジスタを覆う第1エッチングストッパ層121と、DRAMメモリセルのキャパシタ部上層に第2エッチングストッパ層122が形成され、周辺MOSトランジスタの不純物拡散層113は、第1、第2エッチングストッパ層121、122を貫通する電極層131により、上記キャパシタ部上層に形成された金属配線層と接続され、不純物拡散層113の少なくとも一つは素子分離絶縁膜102の境界上に電極層131を接続し、素子分離絶縁膜102上に形成された電極層131の底部の不純物拡散層113表面からの深さ寸法は、不純物拡散層113の接合深さ寸法もより短く形成されたものである。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル形成時のひずみ緩和の抑制を可能にすると共に、更にひずみを印加することを可能にする。

【解決手段】基板1と、基板上に形成されひずみを有する第1半導体層3と、第1半導体層3上に離間して設けられ、第1半導体層3と格子定数が異なる第2および第3半導体層8と、第2半導体層と第3半導体層8との間の第1半導体層3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極5と、を備え、第2半導体層および第3半導体層8直下の第1半導体層3の外表面領域をシリサイド3a、8aとする。

(もっと読む)

半導体装置の製造方法

【課題】リーク電流を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】MOSFET100の製造方法は、炭化珪素基板1を準備する工程と、炭化珪素基板1上に活性層7を形成する工程と、活性層7上にゲート酸化膜91を形成する工程と、ゲート酸化膜91上にゲート電極93を形成する工程と、活性層7上にソースコンタクト電極92を形成する工程と、ソースコンタクト電極92上にソース配線95を形成する工程とを備える。ソース配線95を形成する工程は、ソースコンタクト電極92上に導電体膜を形成する工程と、導電体膜を反応性イオンエッチングによりエッチングすることにより導電体膜を加工する工程とを含む。そして、MOSFET100の製造方法は、導電体膜を加工する工程よりも後に、炭化珪素基板1を50℃以上の温度に加熱するアニールを実施する工程をさらに備える。

(もっと読む)

101 - 120 / 1,636

[ Back to top ]