Fターム[4M104DD84]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 固相反応 (1,946) | シリサイド化 (1,636)

Fターム[4M104DD84]に分類される特許

161 - 180 / 1,636

半導体装置及びその製造方法

【課題】ストレッサ膜を有する半導体装置及びその製造方法に関し、ストレッサ膜からの応力を効率よくチャネル領域に印加してMISFETの電流駆動能力を向上しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に、素子領域を画定する素子分離絶縁膜を形成し、素子領域上に、ゲート絶縁膜を介してゲート電極を形成し、ゲート電極の両側の半導体基板内にソース/ドレイン領域を形成し、ゲート電極及びソース/ドレイン領域が形成された半導体基板上に第1の絶縁膜を形成し、素子分離絶縁膜の端部に生じた窪み内に第1の絶縁膜が残存するように第1の絶縁膜をエッチバックし、半導体基板上に、半導体基板の表面に平行な方向に応力を印加する第2の絶縁膜を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】素子分離領域13は、溝11に埋め込まれた酸化シリコン膜からなり、上部が半導体基板1から突出しており、半導体基板1から突出している部分の素子分離領域13の側壁上に、窒化シリコンまたは酸窒化シリコンからなる側壁絶縁膜SW1が形成されている。MISFETのゲート絶縁膜は、ハフニウムと酸素と低しきい値化用の元素とを主成分として含有するHf含有絶縁膜5からなり、メタルゲート電極であるゲート電極GEは、活性領域14、側壁絶縁膜SW1および素子分離領域13上に延在している。低しきい値化用の元素は、nチャネル型MISFETの場合は希土類またはMgであり、pチャネル型MISFETの場合は、Al、TiまたはTaである。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス負荷を軽減するとともに、EOTを十分に低減するための絶縁膜の薄膜化と、バンドエッジ近傍の仕事関数を有するゲート構造とを実現した半導体装置を提供する。

【解決手段】基板101の異なる領域に形成されたp型トランジスタ100a及びn型トランジスタ100bを備える半導体装置100であって、p型トランジスタ100aは、基板101上方に形成された、第1高誘電率材料からなる第1高誘電率膜106aと、第1高誘電率膜106a上方に形成された、全体が金属によりシリサイド化された第1フルシリサイド電極107aとを備え、n型トランジスタ100bは、基板101上方に形成された、第2高誘電率材料が添加された第1高誘電率材料からなる第2高誘電率膜106bと、第2高誘電率膜106b上方に形成された、全体が金属によりシリサイド化された第2フルシリサイド電極107bとを備える。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置においてショートを生じることを防ぐことができる、半導体装置及びその製造方法を提供する。

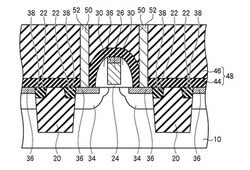

【解決手段】半導体装置は、半導体基板と、半導体基板に所定の間隔で設けられた一対の不純物拡散領域と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側面及び前記ゲート絶縁膜の両側面を覆う、絶縁性の一対のサイドウォールスペーサーと、ゲート電極の上面に形成されたシリサイド金属膜と、を備える。サイドウォールスペーサーは、上下に積み重ねられた下部サイドウォールスペーサーと上部サイドウォールスペーサーとを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】不純物ドープを用いることなく、低温プロセスでオーミック電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】n+型基板1の表面側に素子構造や表面電極を形成した後、n+型基板1の裏面1bにアモルファス層12を形成する。そして、アモルファス層12が形成された裏面1b上に金属薄膜110を形成した後、n+型基板1の裏面1b側に光子エネルギーとレーザ出力の積が1000eV・mJ/cm2以上かつ8000eV・mJ/cm2以下となるような条件でレーザ光を照射することでシリサイド層111を含むドレイン電極11を形成する。これにより、n+型基板1に高温処理を行うことなく、n+型基板1にドレイン電極11にシリサイド層111を生成できる。したがって、不純物ドープ層を用いることなく、かつ低温プロセスによってドレイン電極11をオーミック電極にできる。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタが設計より低い閾値電圧で動作し始めるという寄生トランジスタ動作を抑制する。

【解決手段】半導体装置100は、基板102の素子形成領域に形成されたトレンチ162、トレンチ162の側壁および底面に形成されたゲート絶縁膜120、トレンチ162を埋め込むようにゲート絶縁膜120上に形成されたゲート電極122、基板102表面のゲート長方向の一方の側に形成されたソース領域112、およびゲート長方向の他方の側に形成されたドレイン領域113、を有するトランジスタを含む。ここで、ゲート電極122は、トレンチ162外部の基板102上にも露出して形成され、ゲート電極122は、ゲート長方向における、トレンチ162の両端部上部が覆われるとともに、中央部に少なくとも一つ深さが基板まで達する凹部が形成されるように設けられている。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】本発明は、MPS構造の半導体装置において、逆方向特性の漏れ電流を低減できる半導体装置の製造方法を提供することを目的とする。

【解決手段】第1の導電型の半導体と金属層がオーミック接合するオーミック接合部と、第2の導電型の半導体と金属層がショットキ接合するショットキ接合部とを備える半導体装置の製造方法は、オーミック接合部がオーミック接合可能な膜厚範囲で薄くした膜厚によって、金属層を形成する金属層形成工程(ステップS101、S102)と、金属層の一部を覆って保護する絶縁膜を形成する絶縁膜形成工程(ステップS103、S104)と、絶縁膜形成工程(ステップS103、S104)の後に、絶縁膜をベークすると共に、オーミック接合部の金属層をシリサイド化させる熱処理工程(ステップS105)とを有する。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホール形成時の重ね合わせずれに起因したリークの増大やコンタクト抵抗の上昇が抑制された半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100と、半導体基板100上にゲート絶縁膜101を介して形成されたゲート電極102と、ゲート電極102の側壁上に形成されたサイドウォールスペーサ150と、半導体基板100のうち、ゲート電極102及びサイドウォールスペーサ150を間に挟んで両側に形成されたソースドレイン領域106と、ゲート電極102、サイドウォールスペーサ150、及び半導体基板100の上面を覆う応力絶縁膜110とを備えている。サイドウォールスペーサ150は、少なくとも中央部のゲート長方向膜厚よりも上部のゲート長方向膜厚の方が大きくなっている。

(もっと読む)

固体撮像素子とその製造方法

【課題】配線やコンタクトホールの寸法の微細化に際しても、コンタクト抵抗の低減を図ることが可能であり、且つ、暗電流の発生が少ない固体撮像素子およびその製造方法を提供する。

【解決手段】固体撮像素子1では、配線24と転送電極膜102とが、2層のコンタクトホールにより接続されている。下側のコンタクトホールAは、その底部にチタンシリサイド膜105が形成されている。そして、上側のコンタクトホールBは、チタンシリサイドを構成中に含まず、下側のコンタクトホールとの間が中間配線層としてのタングステン膜107により接続されている。ここで、上下の両コンタクトホールA,Bには、純粋なチタンは残っていない。また、撮像画素領域におけるフォトダイオード121の上方の層内レンズ膜127は、下方のコンタクトホールAに対して積層上方に選択的に形成されている。

(もっと読む)

バイポーラトランジスタ

【課題】高速動作性・高電流駆動力を有するヘテロ接合バイポーラトランジスタ及びその製造方法を提供する。

【解決手段】バイポーラトランジスタは、コレクタとして機能するSi単結晶層3と、Si単結晶層3の上に形成された単結晶のSi/SiGeC層30a及び多結晶のSi/SiGeC層30bと、エミッタ開口部を有する酸化膜31と、エミッタ電極50と、エミッタ層35とを備えている。単結晶のSi/SiGeC層30aに真性ベース層52が形成され、単結晶のSi/SiGeC層30aの一部と多結晶のSi/SiGeC層30bとCoシリサイド層37bとにより、外部ベース層51が構成されている。エミッタ電極の厚みは、エミッタ電極50に注入されたボロンがエミッタ電極50内を拡散して、エミッタ−ベース接合部まで達しないように設定されている。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つチャネルの劣化を抑制可能なトレンチゲートを有する半導体装置を提供する。

【解決手段】n型のドレイン層11と、ドレイン層11の主面に配設され、ドレイン層11よりも不純物濃度が低いn型のドリフト層12と、ドリフト層12上に配設されたp型のベース層13と、ベース層13の表面領域に配設され、ドリフト層12よりも不純物濃度が高いn型のソース層14と、ソース層14及びベース層13を貫通し、ドリフト層12に達する深さを有して配設されたストライプ状のゲートトレンチ16と、ゲートトレンチ16を形成する側面及び底面に沿って配設されたトレンチ形状のゲート絶縁膜17と、ゲート絶縁膜17の開口幅の狭い対向する側面に設けられた触媒層18と、トレンチ形状のゲート絶縁膜17内に、触媒層18に接続されたカーボンナノチューブ19が配設されたゲート電極21とを備える。

(もっと読む)

161 - 180 / 1,636

[ Back to top ]