Fターム[4M104DD84]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 固相反応 (1,946) | シリサイド化 (1,636)

Fターム[4M104DD84]に分類される特許

121 - 140 / 1,636

半導体装置の製造方法、および、半導体装置

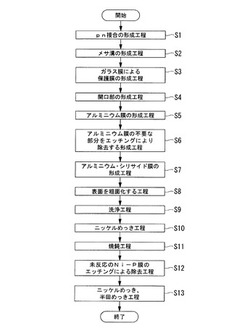

【課題】ニッケルめっき電極を備え、低VFを兼ね備えた半導体装置の製造方法、および、半導体装置を提供することを目的としている。

【解決手段】n型半導体基板の一方の表面近傍に、小電流領域の電圧降下を得るべく濃度設定されたp型の半導体層を形成してpn接合を形成する工程と、p型の半導体層表面に、鉛を含有するガラスパッシベーション膜を形成し、形成したガラスパッシベーション膜の一部を除去して開口部を形成する工程と、開口部を形成した後、p型の半導体層表面に、アルミニウムの膜を形成する工程と、アルミニウムとp型の半導体層のシリコンを、熱処理により反応させてアルミニウム・シリサイド膜を生成する工程と、アルミニウム・シリサイド膜上部に存在するシリコンと未反応のアルミニウムを、エッチングにより除去して表面を粗面化する工程と、粗面化されたアルミニウム・シリサイド膜の上にニッケル電極を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造コストを低減させ、信頼性を向上させる。

【解決手段】半導体ウエハSWを支持するステージ53と、半導体ウエハSWに対向するターゲット54と、半導体ウエハSWとターゲット54との間に配置されたコリメータ61と、半導体ウエハSWとターゲット54との間の空間とコリメータ61とを囲むロアーシールド62及びダークスペースシールド63とを備える成膜装置を用い、スパッタリング法によって半導体ウエハSWにNi−Pt合金膜を形成する。この際、ロアーシールド62およびダークスペースシールド63の内面のうち、コリメータ61の下面61bより上に位置する領域にAl膜71を予め形成しておくが、コリメータ61の下面61bより下に位置する領域にはAl膜71を形成しない。ロアーシールド62及びダークスペースシールド63を取り外して洗浄する際に、アルカリ溶液によってAl膜71を溶解する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】nチャネル型MISFET用のメタルゲート電極であるゲート電極GE1とpチャネル型MISFET用のダミーゲート電極GE2とを形成してから、nチャネル型MISFET用のソース・ドレイン領域とpチャネル型MISFET用のソース・ドレイン領域をそれぞれ形成する。その後、ダミーゲート電極GE2を除去し、ダミーゲート電極GE2が除去されたことで形成された凹部にpチャネル型MISFET用のメタルゲート電極を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】所望の抵抗値を有する制御ゲートを備えた半導体装置の製造方法を提供すること。

【解決手段】シリコン基板13の表面上に第1の絶縁膜15、電荷蓄積層16、第2の絶縁膜17、およびポリシリコン膜21をこの順で形成する工程と、ポリシリコン膜21上および両側壁全面に金属膜25を形成する工程と、金属膜25が形成されたポリシリコン膜21を加熱してシリサイド化する工程と、金属膜25を除去する工程と、を具備する半導体装置の製造方法。

(もっと読む)

半導体記憶装置

【課題】メモリセルの特性の劣化を抑制した半導体記憶装置を提供する。

【解決手段】メモリセルは、ダイオード層、可変抵抗層、及び電極層を備える。ダイオード層は、整流素子として機能する。可変抵抗層は、可変抵抗素子として機能する。電極層は、可変抵抗層とダイオード層との間に設けられ、可変抵抗層及びダイオード層に接するように形成されている。電極層は、窒化チタンにて構成された窒化チタン層を備える。ここで、窒化チタン層内の第1領域における窒素原子に対するチタン原子の割合を第1割合とし、窒化チタン層内であって且つ第1領域よりも可変抵抗層に近い第2領域における窒素原子に対するチタン原子の割合を第2割合とする。この場合、第2割合は第1割合よりも大きい。

(もっと読む)

異種材料接合型ダイオード及びその製造方法

【課題】電流電圧特性を維持しつつ、アノード電極6の剥離に対する機械的強度を向上させる。

【解決手段】異種材料接合型ダイオードは、半導体基体1と、半導体基体1の上に形成された第1導電型のドリフト領域2と、ドリフト領域2の主表面に接合された、ドリフト領域2とは異なる種類の材料からなるアノード電極6と、半導体基体1に接続されたカソード電極7とを備える。ドリフト領域2とアノード電極6との接合によりダイオードが形成されている。アノード電極6の主表面のうち、ドリフト領域2に接している側の主表面に、嵌合構造(3、G1)が形成されている。

(もっと読む)

酸化膜電界効果トランジスタおよびその製造方法

【課題】デバイス特性のばらつきを抑制しつつ、耐久性を向上可能なSiC系酸化膜電界効果トランジスタ、およびデバイス特性のばらつきを抑制することが可能なSiC系酸化膜電界効果トランジスタの製造方法を提供する。

【解決手段】MOSFET1は、n+SiC基板10と、n−SiC層20と、pウェル21と、n+ソース領域22と、絶縁層35とを備えている。一方のpウェル211および他方のpウェル212においては、pウェル21の中に配置される第1n+ソース領域221と、pウェル21の内部からpウェル21の外部にまで延在する第2n+ソース領域222とが、チャネル領域29を挟んで互いに対向するように配置されている。絶縁層35の厚みは、pウェル21の内部に位置するチャネル領域29上よりも、ウインドウ領域28上において大きくなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】基板表面にシリサイド膜が形成された半導体装置において、ゲート電極パターンの粗密に関わらず、コンタクトの深さの差を緩和する。

【解決手段】半導体装置100は、活性領域(104)に、表面にシリコン酸化膜122aが選択的に形成されたシリサイド膜120aを形成する工程と、その上に、シリコン酸化膜120aとの間でエッチング選択比を有するライナー絶縁膜124を形成する工程と、その上に、ライナー絶縁膜124との間でエッチング選択比を有する絶縁膜(126)を形成する工程と、絶縁膜(126)、ライナー絶縁膜124、およびシリコン酸化膜122aを貫通してシリサイド膜120aに達する第1のコンタクトホール144を形成する工程と、により製造される。

(もっと読む)

金属−炭化珪素オーミックコンタクトの局所的アニーリングおよびそのようにして形成された素子

【課題】高温アニーリングは、SiC基板上に含まれる窒化ガリウムベースの材料からなるエピタキシャル層に損傷を与える可能性がある。

【解決手段】炭化珪素(SiC)基板上に金属を形成し、この金属とSiC基板との界面部をアニーリングして、そこに金属−SiC材を形成し、SiC基板上のある箇所ではアニーリングされないようにして、そこには金属−SiC材が形成されないようにすることによって半導体素子のコンタクトを形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】部分反応方式のサリサイドプロセスによりゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の第1の熱処理では、熱伝導型アニール装置を用いて半導体ウエハを熱処理し、第2の熱処理では、マイクロ波アニール装置を用いて半導体ウエハを熱処理することにより、第2の熱処理を低温化し、金属シリサイド層41の異常成長を防ぐ。これにより金属シリサイド層41の接合リーク電流を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】NBTIを改善することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたn型ウェル領域102と、n型ウェル領域102上に形成され、ゲート絶縁膜104と、下部ゲート電極105、及び下部ゲート電極105上に形成された上部ゲート電極106を含むゲート電極120とを有するpチャネル型MISトランジスタとを備える。下部ゲート電極105は、結晶粒界を有する多結晶の金属窒化物で構成されており、当該結晶粒界には金属窒化物を構成する元素とは異なる元素が偏析されている。

(もっと読む)

半導体装置

【課題】半導体装置の耐圧を向上させる。

【解決手段】半導体装置10は、p型半導体基板1、p型半導体基板1内に設けられたn型ドリフト領域3、及びn型ドリフト領域3内に設けられたp型ボディ領域4を含む。p型ボディ領域4の側面とn型ドリフト領域3とのpn接合部22の上方に、そのpn接合部22に沿って、環状のゲート電極6が設けられる。このゲート電極6の一部を挟んでn型ドリフト領域3内及びp型ボディ領域4内にそれぞれ、n型ドレイン領域7及びn型ソース領域8が設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】Ge半導体層に、極浅かつ高濃度のキャリアからなるn型不純物領域を形成する。

【解決手段】n型とp型のうちの一方の導電型の半導体基板と、半導体基板表面に選択的に設けられ、一方の導電型と異なる導電型の一対の不純物拡散領域と、一対の不純物拡散領域により挟まれた半導体基板上に設けられたゲート絶縁層と、ゲート絶縁層の上に設けられたゲート電極とを備え、不純物拡散領域の少なくとも一部は、基板に含まれる不純物と同じ導電型で、かつ基板の不純物濃度より高い不純物濃度を有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】添加元素に起因してNiシリサイド層が高抵抗化することを抑制する。

【解決手段】まず、シリコン層100上に、Niより原子番号が大きい金属元素を含み、Niを含まない反応制御層202を形成する。次いで、反応制御層202上にNiを堆積し、シリコン層100、反応制御層202、及びNiを熱処理することにより、シリコン層100にNiシリサイド層200を形成する。反応制御層202は、Niより原子番号が大きい金属元素から構成されるのが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の主面上の洗浄効果を低下させることなく、電界効果トランジスタのゲート電極の側面上に形成されたオフセットスペーサ膜の除去を抑制する。

【解決手段】ゲート電極部Gn,Gpを覆うように、半導体基板1の主面上に薬液に対するエッチング速度が互いに異なる第1OSS膜10および第2OSS膜12を順次形成した後、異方性エッチングにより、ゲート電極部Gn,Gpの側面上に位置する第2OSS膜12を残して、他の部分に位置する第2OSS膜12を除去する。そして、ゲート電極部Gn,Gpと、ゲート電極部Gn,Gpの側面上に位置する第1OSS膜10および第2OSS膜12と、をマスクにして、半導体基板1に不純物をイオン注入した後、半導体基板1を薬液により洗浄して、露出している第1OSS膜10を除去する。

(もっと読む)

ワイドバンドギャップ半導体装置

【課題】ワイドバンドギャップ半導体デバイスにおいて、金属/ワイドバンドギャップ半導体界面を有する装置の逆方向電圧印加時のリーク電流の増加や、オン抵抗の増加を抑制する。

【解決手段】第1導電型の高濃度ワイドバンドギャップ半導体基板と、半導体基板上に形成された第1導電型の低濃度のワイドバンドギャップ半導体堆積膜と、半導体堆積膜上に形成され、半導体堆積膜との間でショットキー界面領域を構成する金属膜8と、該第1導電型の低濃度のワイドバンドギャップ半導体堆積膜の金属膜周辺部に対応する領域に形成された第2導電型の領域4,5とを含み、該第1導電型の低濃度のワイドバンドギャップ半導体堆積膜における該ショットキー界面領域は、第2導電型の領域に囲まれて複数個の周期的な島領域を構成する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造工程の煩雑化および製造プロセスの長時間化を抑制できると共に、量産性に優れた半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法では、ゲート電極7上に、積層膜19を形成する。そして、層間絶縁膜8形成後、層間絶縁膜8等に対してエッチング処理を施す。これにより、ソース領域3およびp+ベースコンタクト領域5が底面から露出した第1のコンタクトホール12を形成すると同時に、積層膜19が底面から露出した第2のコンタクトホール13を形成する。ここで、当該エッチング処理は、積層膜19のエッチングレートが層間絶縁膜8のエッチングレートよりも遅くなるエッチング条件により、実施する。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

121 - 140 / 1,636

[ Back to top ]