Fターム[4M104DD89]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 限定部分の物質、物性の変換 (333) | 電極表面のみ(電極層間界面を含む) (197)

Fターム[4M104DD89]の下位に属するFターム

電極下部のみ(基板との界面) (25)

Fターム[4M104DD89]に分類される特許

161 - 172 / 172

半導体集積回路装置およびその製造方法

ポリメタルゲートを構成する高融点金属膜の洗浄工程における欠けを防止し、装置の特性を向上させ、また、洗浄効率を向上させるため、基板1上の低抵抗多結晶シリコン膜9a、WN膜9bおよびW膜9cを、窒化シリコン膜10をマスクにドライエッチングし、これらの膜よりなるゲート電極9を形成し、ウエットハイドロゲン酸化により薄い酸化膜9dを形成した後、RPN法を用いて窒化処理を行い、ゲート電極の側壁から露出したW膜9cをWN膜9eとする。その結果、その後の洗浄工程、例えば、n−型半導体領域11やp−型半導体領域12の形成時に行われる、1)レジスト膜のホトリソグラフィー工程、2)不純物の注入工程、3)レジスト膜の除去工程および4)基板表面の洗浄工程が繰り返し行われても、W膜9cの欠けを防止でき、また、洗浄液としてU洗浄液やフッ酸系の洗浄液のような強い洗浄液を用いることができる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 信頼性の高いフルシリサイドMOSFETおよびシリサイドMOSFETを従来よりも簡単に同一基板上に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10上にゲート絶縁膜30を形成し、ゲート絶縁膜上に第1のゲート電極40および第2のゲート電極42を形成し、第1のゲート電極および第2のゲート電極上にマスク材料90を堆積し、第2のゲート電極を被覆したまま第1のゲート電極の上面を露出させるようにマスク材料をパターニングし、マスク材料を利用して第1のゲート電極の上部をエッチングし、マスク材料を除去し、第1のゲート電極および第2のゲート電極上に金属膜100を堆積し、第1のゲート電極の全部および第2のゲート電極の上部をシリサイド化することを具備する。

(もっと読む)

半導体装置

【課題】低抵抗、且つ高耐熱性を有するゲート電極またはゲート配線を備えた高性能な半導体装置を実現する。

【解決手段】ゲート電極またはゲート配線を三層以上の積層構造とし、例えば、第1の導電層106a/第2の導電層106b/第3の導電層106cを形成する。さらに、第2の導電層の幅は、第1の導電層及び第3の導電層の幅よりも狭いことを特徴とする。そして第1の導電層及び第3の導電層は高融点金属でなる。これにより高性能な半導体装置を実現できる。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、ゲート電極の空乏化を抑制すると共に、シリサイドの高抵抗化を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】 ゲート絶縁膜上に、所定の半導体材料とゲルマニウムとを含む膜を形成するステップと、膜を酸化することにより、ゲート絶縁膜上に、当該膜よりもゲルマニウム濃度が高くかつ膜厚が薄い第1の膜を形成すると共に、第1の膜上に酸化膜を形成するステップと、酸化膜を除去するステップと、第1の膜上に、半導体材料を含み、第1の膜よりもゲルマニウム濃度が低い第2の膜を形成するステップと、第2の膜及び第1の膜にエッチングを行うことにより、ゲート電極を形成するステップとを備えることを特徴とする。

(もっと読む)

エレクトロマイグレーション制御

エレクトロマイグレーション及びその悪影響の制御方法、パターン化された半導体デバイスの導電層(9)。複数の空孔障壁(10)は、選択された原子を打込むことによって、金属相互接続部(9)に沿って各々の位置で生成させる。各々空孔障壁(10)は、エレクトロマイグレーション(8)によって生成された空孔がそこに蓄積させる、このことにより導線(9)に沿ってこのようなエレクトロマイグレーションの全体の効果を分布し、及び半導体デバイスの寿命をかなり増やす。  (もっと読む)

(もっと読む)

有機薄膜トランジスタ、有機薄膜トランジスタシート及びこれらの製造方法

【課題】 基板への接着性が良好で、且つ、良好に駆動可能な有機薄膜トランジスタ、該有機薄膜トランジスタを設けた有機薄膜トランジスタシート及びこれらの製造方法の提供。

【解決手段】 支持体と金属箔とをラミネートする接着層を支持体上に有し、前記支持体と前記金属箔とが前記接着層によりラミネートされ、前記支持体上にラミネートされた前記金属箔表面が研磨されたものであることを特徴とする有機薄膜トランジスタ。

(もっと読む)

半導体装置の製造方法

【課題】 絶縁膜に形成された凹部に埋め込んだ銅配線の表面をパラジウム置換めっきするにあたり、銅配線の表面がエッチングされることを抑え、良好な電気特性を長期に亘り維持可能な半導体装置を製造すること。

【解決手段】 絶縁膜例えばSiOC膜21をエッチングすることにより形成した凹部200に銅を埋め込んで銅配線25を形成した後、カルボキシル基を有する有機酸溶液にパラジウムを溶かしてなる置換めっき液を用いて前記凹部200に埋め込まれた銅配線25の表面をパラジウム置換めっきする。そしてパラジウム膜26が形成された銅配線25の表面に無電解めっき液を用いて密着層27を形成する構成とする。この場合、有機酸を選択したことにより、パラジウム置換めっき時に銅配線25がエッチングさせることを抑えることができる。

(もっと読む)

デュアル・ゲートCMOSの製造

本発明は、CMOS素子を製造する方法に関し、その方法は、絶縁材料層(102)をその中に有する半導体基板(101)を準備するステップと、絶縁層(102)の上に第1の材料層(106)を形成するステップとを備え、第1の材料層(106)の厚さが、第1の能動素子を担持する第1の領域(103)では、第2の能動素子を担持する第2の領域(104)より薄い。次いで、第2の材料層(107)が、第1の材料層(106)上に形成され、次いで、その構造体に熱処理が行われて、第1と第2の材料が合金化される。第1の領域上の両層部分は全体が合金化されるが、第2の領域上の両層部分はそうはならず、その結果、第1の材料層(106)の一部分(109)が残留する。  (もっと読む)

(もっと読む)

導電性材料とその製法

【課題】銅を含む導電性コア領域と界面領域とを有する導電性材料及び該導電性材料の製造方法を提供すること。

【解決手段】銅と、0.001原子百分率から0.6原子百分率までの、イリジウム、オスミウム、及びレニウムから選択された1つ又はそれ以上の金属とを含む導電性コア領域、及び界面領域を備える導電性材料である。界面領域は、少なくとも80原子百分率又はそれ以上の1つ又はそれ以上の金属を含む。界面領域は、銅と、イリジウム、オスミウム、及びレニウムから選択された1つ又はそれ以上の金属とを含むシード層を形成し、その上に銅からなる導電性層を形成し、導電性層を研磨して、研磨された銅の表面材料を構成し、シード層から研磨された表面への1つ又はそれ以上の金属のマイグレーションを引き起こすのに十分な温度で該研磨された銅の表面材料をアニールして形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】 リーク電流の少ない半導体装置を提供する。

【解決手段】 半導体装置は、第1導電型を有する半導体基板1を含む。第2導電型を有する1対のソース/ドレイン領域4が半導体基板の表面に形成される。ゲート絶縁膜3がソース/ドレイン領域相互間のチャネル領域上に配設される。第1導電型を有するゲート電極5がゲート絶縁膜上に配設される。ゲート電極は、チャネル領域の上方に位置する第1部分5aと、ソース/ドレイン領域の上方に位置する第2部分5bとを有する。第2部分の多数キャリア濃度は第1部分の多数キャリア濃度より低い。

(もっと読む)

陽極酸化装置および終点検出方法

【課題】 弾性表面波共振片の電極パターンに形成される陽極酸化膜の厚さを一定にするとともに、弾性表面波共振片の共振周波数を一定にする陽極酸化装置および終点検出方法を提供する。

【解決手段】 陽極酸化装置10は、被処理物に形成される陽極酸化膜の厚さに応じて前記被処理物に印加される電圧値を求めるとともに、前記電圧値より陽極酸化を終了する終点電流設定値を求める電源制御部20と、前記電源制御部20で求めた値の電圧を陽極酸化槽12の電解液中に浸漬された前記被処理物に印加するとともに、前記電源制御部20によって前記被処理物への電源供給が制御される電源部18と、前記被処理物に供給される電流値を監視するとともに、前記電流値が前記終点電流設定値を下回ったときに陽極酸化の終点と判定する監視部24とを有する構成である。

(もっと読む)

MOSトランジスタ

【課題】 再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供する。

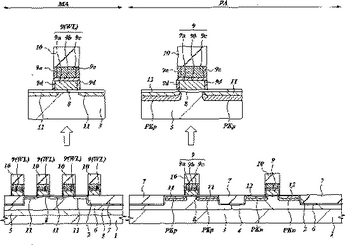

【解決手段】 半導体基板1に形成したソース及びドレイン領域10a,10bと、酸化膜3bを介して形成したゲート電極5と、前記ソース及びドレイン領域10a,10bとチャネル形成領域30の間に前記ソース及びドレイン領域10a,10bを取り囲むソース及びドレイン低濃度領域6a’,6b’とを有するMOSトランジスタにおいて、前記酸化膜3bを介して前記ソース及びドレイン低濃度領域6a’,6b’に接する導電性である2つのサイドスペーサ9aと、前記ゲート電極5及び前記サイドスペーサ9a上に形成された導電性薄膜15とを有する。

(もっと読む)

161 - 172 / 172

[ Back to top ]