Fターム[4M104DD89]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 限定部分の物質、物性の変換 (333) | 電極表面のみ(電極層間界面を含む) (197)

Fターム[4M104DD89]の下位に属するFターム

電極下部のみ(基板との界面) (25)

Fターム[4M104DD89]に分類される特許

41 - 60 / 172

半導体装置およびその製造方法

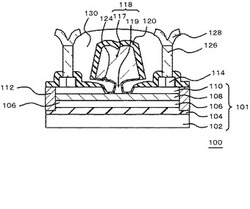

【課題】ゲート電極の内部に腐食が進行することを抑制する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、化合物半導体基板101と、化合物半導体基板101上の一部に形成された接続部119と接続部119上に形成されかつ接続部119より幅広の本体部117とを有しており、かつアルミニウムを含むゲート電極118と、ゲート電極118の表面上に設けられた保護絶縁層(シリコン窒化膜120)と、シリコン窒化膜120が被覆していないゲート電極118の表面に設けられており、アルミニウムよりも酸化されにくい不動態膜124と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ボイドやシームが発生しにくい構造体とする。

【解決手段】本発明の半導体装置は、半導体基板101に形成された層間絶縁膜103と、層間絶縁膜103に形成されたコンタクト孔104と、コンタクト孔104を埋め込むCu膜107と、コンタクト孔104の内部の側壁に形成され、Cu膜107の下地となる金属含有下地膜13と、を備える。コンタクト孔104の開口に接続している側壁の一部を含む第一の領域11において、金属含有下地膜13は、Cu膜107との界面に金属窒化層106を有する。第一の領域11よりも半導体基板101側の側壁を含む第二の領域12において、金属含有下地膜13は、Cu膜107との界面に金属層105を有する。金属層105の表面におけるCu膜107の成膜速度は、金属窒化層106の表面におけるCu膜107の成膜速度よりも大きい。

(もっと読む)

トランジスタ基板及びその製造方法

【課題】オフ領域におけるゲート電圧−ドレイン電流特性(Vg−Id特性)の劣化を抑制した薄膜トランジスタを備えたトランジスタ基板及びその製造方法を提供する。

【解決手段】薄膜トランジスタTFTに設けられるチャネル保護層15の下層に形成された半導体層14のうち、ソース、ドレイン電極17間に側壁部が露出する領域(及びその近傍領域)が、酸素プラズマ処理により酸化処理されている。これにより、当該領域に酸化膜20が形成され、非導体化又は高抵抗化する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体装置のソース電極、ドレイン電極及びゲート電極を形成するいずれの領域においても、残渣のない良好な半導体/金属界面が得られるようにする。

【解決手段】化合物半導体装置の製造方法を、基板1上に化合物半導体積層構造4を形成する工程と、化合物半導体積層構造上に金属膜5A〜5Cを形成する工程と、金属膜上にソース電極7及びドレイン電極8を形成する工程と、金属膜の一部を酸化又は窒化して、金属酸化物膜又は金属窒化物膜5CXを形成する工程と、金属酸化物膜又は金属窒化物膜上にゲート電極9を形成する工程とを含むものとする。

(もっと読む)

有機薄膜トランジスタの製造方法、有機薄膜トランジスタレイの製造方法及び表示装置の製造方法

【課題】有機薄膜トランジスタを高い歩留まりで製造する製造方法を提供する。

【解決手段】基板上又は基板上における絶縁膜上にソース電極及びドレイン電極を形成する電極形成工程と、有機半導体インクが供給された際、前記ソース電極及び前記ドレイン電極上における前記有機半導体インクの接触角を前記基板上又は前記絶縁膜上における接触角よりも高くする電極処理工程と、形成された前記ソース電極及び前記ドレイン電極の間に前記有機半導体インクを供給することにより有機半導体層を形成する半導体層形成工程と、を有し、前記ソース電極と前記ドレイン電極とにより形成されるチャネルのチャネル幅をW、前記有機半導体インクが供給される際の液滴の液滴径をφ、前記液滴が供給される位置の誤差である着弾位置誤差幅をXとした場合、W>φ+Xを満たしていることを特徴とする有機薄膜トランジスタの製造方法を提供することにより上記課題を解決する。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

半導体装置

【課題】シリサイドプロセス前にイオン注入を行う半導体装置であって、より確実にMISFETにおけるリーク電流の抑制が図れるものを実現する。

【解決手段】マスク層RMによりPチャネル型MISFETを覆いつつ、Nチャネル型MISFETのN型ソース領域およびN型ドレイン領域に、イオン(F,Si,C,Ge,Ne,Ar,Krのうち少なくとも一種類を含む)を注入する。その後、Nチャネル型MISFETおよびPチャネル型MISFETの各ゲート電極、ソース領域およびドレイン領域にシリサイド化(Ni,Ti,Co,Pd,Pt,Erのうち少なくとも一種類を含む)を行う。これにより、Pチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流を劣化させること無く、Nチャネル型MISFETにおいてドレイン−ボディ間オフリーク電流(基板リーク電流)の抑制が図れる。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置の製造装置

【課題】希釈された溶液を用いて、貴金属を含む被処理膜等を迅速に且つ効果的にエッチングでき、且つ、設備の稼働率を向上できるようにする。

【解決手段】薬液を調合する薬液調合槽24と、調合された薬液を貯蔵する薬液貯蔵槽28と、貯蔵された薬液を用いて半導体基板を処理する処理チャンバ21とを有する半導体装置の製造装置を用いた半導体装置の製造方法は、薬液調合槽24において、酸化剤と錯化剤とを混合して第1の薬液を調合し、薬液調合槽24において、第1の薬液を活性化する。続いて、薬液貯蔵槽28において、活性化された第1の薬液と純水とを混合し、第1の薬液の濃度及び温度を調整することにより、第1の薬液を希釈した第2の薬液を調整する。続いて、処理チャンバ21に投入された半導体基板に第2の薬液を供給する。

(もっと読む)

薄膜トランジスタおよびその製造方法、並びに表示装置

【課題】チャネルへの不純物添加を行うことなく閾値電圧を大きくすることが可能な薄膜トランジスタおよびその製造方法、並びに表示装置を提供する。

【解決手段】基板11にゲート電極20を形成したのち、このゲート電極20の表面から厚み方向における一部を、熱処理またはプラズマ処理を用いて酸化させることにより、ゲート電極20のゲート絶縁膜30との界面20Aから厚み方向における一部を、金属酸化物よりなる界面層21とする。ゲート電極20のゲート絶縁膜30との界面20Aにおける仕事関数が大きくなるので、ゲート電極20と酸化物半導体膜40との仕事関数差φMSが大きくなり、閾値電圧Vthが大きくなる。

(もっと読む)

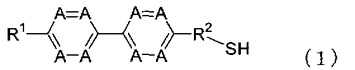

金属電極および該金属電極を有する有機半導体素子

【課題】本発明は、有機高分子等の半導体薄膜形成材料が単結晶でなく、多結晶であっても、印刷方法により金属電極上に安定で良好な有機半導体薄膜を簡便に形成することができ、性能の優れた有機半導体素子を提供することを課題とする。

【解決手段】本発明の金属電極は、下記式(1)で表される化合物を含有する溶液を用いて形成された表面処理層を有することを特徴とする。 (もっと読む)

(もっと読む)

半導体装置およびその作製方法

【課題】良好な特性を備えた、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、ソース電極およびドレイン電極は、その側面が酸化された酸化領域を有する半導体装置である。なお、ソース電極およびドレイン電極の酸化領域は、300MHz以上300GHz以下の高周波電力、および、酸素とアルゴンの混合ガスを用いたプラズマ処理により形成されたものであることが望ましい。

(もっと読む)

半導体装置およびその作製方法

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、不純物領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の酸化物半導体層と、第2のソース電極および第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、を有し、第2のソース電極および第2のドレイン電極は、その側面が酸化された酸化領域を有し、第1のゲート電極、第1のソース電極、または第1のドレイン電極のいずれかは、第2のゲート電極、第2のソース電極、または第2のドレイン電極のいずれかと電気的に接続されている半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

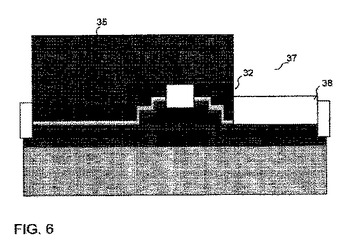

マスク・レベルを削減した金属酸化物FETの製造法

アクティブ・マトリクス・ディスプレイ用の薄膜トランジスタを、マスキング作業を削減して製作する方法は、基板上にゲートをパターン形成することを含む。ゲート誘電体がゲート上に形成され、さらに、半導体金属酸化物がゲート誘電体上に堆積される。チャネル保護層が、ゲートの上方に重なる半導体金属酸化物上にパターン形成されてチャネル領域が画定され、半導体金属酸化物の残部が露出される。その構造上にソース/ドレイン金属層が堆積され、ゲートの上のチャネル保護層までエッチングすることにより、ソース/ドレイン金属層がソース端子とドレイン端子とに分離され、さらに、周辺部でソース/ドレイン金属層および半導体金属酸化物を通ってエッチングされ、トランジスタが隔離される。非導電性スペーサが、トランジスタおよび周囲のソース/ドレイン金属層の部分上にパターン形成される。  (もっと読む)

(もっと読む)

金属酸化膜の形成方法および金属酸化膜

【課題】所定パターンを有するとともに、表面抵抗率や光透過率等のばらつきが少ない金属酸化膜の形成方法およびそのような金属酸化膜を提供する。

【解決手段】基材上に、所定パターンを有する金属酸化膜の形成方法等であって、基材に対して、金属塩を含有する液状物を塗布して金属塩膜を形成する第1工程と、金属塩膜に対して、所定パターンを設ける第2工程と、金属塩膜に対して、熱酸化処理または所定のプラズマ酸化処理を行い、金属酸化膜とする第3工程と、を含む。

(もっと読む)

薄膜トランジスタアレイ基板、発光パネル及びその製造方法並びに電子機器

【課題】製造中のパーティクルの発生を低減して、歩留まりを改善することができる基板構造を有する薄膜トランジスタアレイ基板、該薄膜トランジスタアレイ基板を適用した発光パネル及びその製造方法、並びに、該発光パネルを実装した電子機器を提供する。

【解決手段】基板11上に形成されるトランジスタTr11、Tr12に接続される配線層のうち、最上層に形成される配線(電源電圧ラインLa、選択ラインLs)表面の少なくとも一部が陽極酸化膜で形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

41 - 60 / 172

[ Back to top ]