Fターム[4M104DD89]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 限定部分の物質、物性の変換 (333) | 電極表面のみ(電極層間界面を含む) (197)

Fターム[4M104DD89]の下位に属するFターム

電極下部のみ(基板との界面) (25)

Fターム[4M104DD89]に分類される特許

21 - 40 / 172

半導体装置

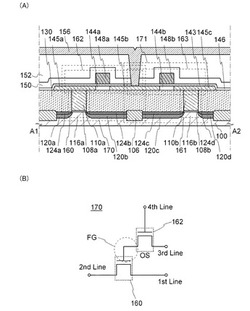

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

バリア層の形成方法

【課題】 本発明は、以上の点に鑑み、異種金属からなる導電層間に介在されるような場合でも十分なバリア性能を発揮し得るバリア層を生産性よく形成することができるバリア層の形成方法を提供する。

【解決手段】 バリア層BMは、処理対象物Wを一方の導電層CL1を有するものとし、この処理対象物と、例えばTi製のターゲット2とを真空処理室1a内に配置し、真空処理室内に希ガスを導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして一方の導電層表面に第1金属層を形成し、真空処理室内に酸素ガス及び窒素ガスを含むガスを導入してプラズマ雰囲気を形成し、第1金属層の表面を酸窒化処理すると共に、ターゲットをもプラズマ雰囲気に曝して当該ターゲット表面を酸窒化し、真空処理室内に希ガスを更に導入してプラズマ雰囲気を形成し、ターゲットをスパッタリングして酸窒化処理された表面に第2金属層を形成してなる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】より良い製造工程で良好な特性の半導体装置を製造する技術を提供する。

【解決手段】導電性膜上に第1領域1Asを覆い、第1領域と隣接する第2領域1Adを開口したマスク膜を形成し、導電性膜中に不純物イオンを注入し、導電性膜を選択的に除去することにより、第1領域と第2領域との境界を含む領域にゲート電極GE1を形成する。その後、熱処理を施し、ゲート電極の側壁に側壁酸化膜7を形成し、ゲート電極の第2領域側の端部の下方に位置する半導体基板中にドレイン領域を形成し、ゲート電極の第1領域側の端部の下方に位置する半導体基板中にソース領域を形成する。かかる工程によれば、ドレイン領域側のバーズビーク部7dを大きくし、ソース領域側のバーズビーク部を小さくできる。よって、GIDLが緩和され、オフリーク電流を減少させ、また、オン電流を増加させることができる。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】基板表面にシリサイド膜が形成された半導体装置において、ゲート電極パターンの粗密に関わらず、コンタクトの深さの差を緩和する。

【解決手段】半導体装置100は、活性領域(104)に、表面にシリコン酸化膜122aが選択的に形成されたシリサイド膜120aを形成する工程と、その上に、シリコン酸化膜120aとの間でエッチング選択比を有するライナー絶縁膜124を形成する工程と、その上に、ライナー絶縁膜124との間でエッチング選択比を有する絶縁膜(126)を形成する工程と、絶縁膜(126)、ライナー絶縁膜124、およびシリコン酸化膜122aを貫通してシリサイド膜120aに達する第1のコンタクトホール144を形成する工程と、により製造される。

(もっと読む)

EL表示装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものと

して、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を

有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線

上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層

と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前

記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを

特徴としている。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 低コストで必要な仕事関数及び耐酸化性を有する金属膜を備えた半導体装置を提供する。

【解決手段】 基板を処理容器内に搬入する工程と、処理容器内に処理ガスを供給し排気することで、基板上に所定膜厚の金属膜を形成する処理を行う工程と、処理済基板を処理容器内から搬出する工程と、を有し、処理を行う工程では、金属膜を形成する途中もしくは金属膜を形成した後に処理容器内に酸素含有ガスおよび/または窒素含有ガスを熱またはプラズマで活性化して供給し排気することで、金属膜の底面もしくは表面を導電性の金属酸化層、導電性の金属窒化層または導電性の金属酸窒化層に改質する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 低コストで必要な仕事関数及び耐酸化性を有する金属膜を備えた半導体装置を提供する。

【解決手段】 表面に金属膜が形成された基板を処理容器内に搬入する工程と、処理容器内に原料ガスと酸化源とを供給し排気することで、基板の表面に形成された金属膜上に所定膜厚の金属酸化膜を形成する処理を行う工程と、処理済基板を処理容器内から搬出する工程と、を有し、処理を行う工程では、酸化源としてオゾンガス、酸素ガスまたはプラズマにより活性化された酸素ガスを用い、所定膜厚の金属酸化膜を形成する過程において形成される金属酸化膜越しに、酸化源に含まれる酸素原子を、金属膜の表面に導入することで、金属膜の表面を酸化して導電性の金属酸化層に改質する。

(もっと読む)

半導体装置及びその製造方法

【課題】ダイオードと電極材料とのコンタクト抵抗を低減した半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、シリコンを含むダイオードと、前記ダイオードに対して積層された金属層及び可変抵抗膜と、前記ダイオードと前記金属層との間に設けられた、チタンとシリコンと窒素とを含む層と、を備えた。前記チタンと前記シリコンと前記窒素とを含む前記層は、前記窒素よりも前記チタンまたはチタンシリサイドを多く含む。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】半導体領域または導電領域を被覆する絶縁膜に、溝及び該半導体領域または導電領域に達するコンタクトホールの少なくともいずれかを形成し、溝及びコンタクトホールの少なくともいずれかに第一の導電膜を形成し、酸化性ガス及びハロゲン系ガスの混合ガスから生成するプラズマに暴露した後、水を含む雰囲気に暴露して、第一の導電膜の一部または全部を流動化し、その後、第一の導電膜上に第二の導電膜を形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】n型及びp型の少なくともいずれかの不純物が添加された不純物領域を有する半導体膜と、配線とを有し、配線は、導電性を有する金属酸化物を含む拡散防止膜と、該拡散防止膜上の低抵抗導電膜とを有し、配線と半導体膜とのコンタクト部において、拡散防止膜と不純物領域とが接する。拡散防止膜は、導電膜を酸化性ガス及びハロゲン系ガスの混合ガスから生成されるプラズマに暴露して該導電膜に含まれる金属材料の酸化物を形成し、金属材料の酸化物が形成された導電膜を、水を含む雰囲気に暴露して導電膜を流動化させ、流動化した導電膜を固化することで形成する。

(もっと読む)

導電部形成方法、導電部及び発光装置

【課題】導電部の欠損を防止すること。

【解決手段】Al含有膜2からなるゲートラインLgやコンタクト部42などの導電部を形成する際に、下層保護導電膜/Al含有膜/上層保護導電膜の導体膜を成膜した後、その導体膜に改質処理として酸化処理を施して、上層保護導電膜3で覆われずにピンホールPから露出してしまったAl含有膜2部分に酸化保護領域4を形成することによって、Al含有膜2がレジストの剥離液などに晒されて消失してしまうことを防ぎ、導電部の欠損を防止した。

(もっと読む)

半導体装置の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

バイポーラトランジスタ

【課題】高速動作性・高電流駆動力を有するヘテロ接合バイポーラトランジスタ及びその製造方法を提供する。

【解決手段】バイポーラトランジスタは、コレクタとして機能するSi単結晶層3と、Si単結晶層3の上に形成された単結晶のSi/SiGeC層30a及び多結晶のSi/SiGeC層30bと、エミッタ開口部を有する酸化膜31と、エミッタ電極50と、エミッタ層35とを備えている。単結晶のSi/SiGeC層30aに真性ベース層52が形成され、単結晶のSi/SiGeC層30aの一部と多結晶のSi/SiGeC層30bとCoシリサイド層37bとにより、外部ベース層51が構成されている。エミッタ電極の厚みは、エミッタ電極50に注入されたボロンがエミッタ電極50内を拡散して、エミッタ−ベース接合部まで達しないように設定されている。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置

を提供することを課題の一とする。また、同一基板上に複数種類の薄膜トランジスタの構

造を作製して複数種類の回路を構成し、増加する工程数が少ない半導体装置の作製方法を

提供することを課題の一とする。

【解決手段】絶縁表面上に金属薄膜を成膜した後、酸化物半導体層を積層し、その後、加

熱処理などの酸化処理を行うことで金属薄膜の一部または全部を酸化させる。また、論理

回路などの高速動作を優先する回路と、マトリクス回路とで異なる構造の薄膜トランジス

タを配置する。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】バリアメタル層を有する半導体装置を製造するに際し、パーティクルの発生を抑制可能な製造方法、及びこの製造方法を用いる半導体装置の製造装置を提供する。

【解決手段】

2つの金属層の間に金属化合物層が挟まれてなるバリアメタル層を有する半導体装置を製造するに際し、チタン及びタンタルのいずれか一方の金属元素から構成されるターゲットを希ガスの雰囲気でスパッタして、複数の金属層を下地配線上に積層する過程において最下層となる第1金属層に酸化処理を施す。次いで、最下層となる第1金属層の表面に第1金属酸化物層を形成した後に、層間において構成元素が異なるように、一つ以上の金属層を含む下地の表面に対して酸化処理、窒化処理、及び酸窒化処理のいずれかの処理を施す。こうした処理より第2金属化合物層を形成する。上記金属化合物層は、金属酸化物層の他、金属窒化物層や金属酸窒化物層であってもよい。

(もっと読む)

21 - 40 / 172

[ Back to top ]