Fターム[4M104DD89]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 限定部分の物質、物性の変換 (333) | 電極表面のみ(電極層間界面を含む) (197)

Fターム[4M104DD89]の下位に属するFターム

電極下部のみ(基板との界面) (25)

Fターム[4M104DD89]に分類される特許

141 - 160 / 172

半導体装置および半導体装置の製造方法

【課題】SOI基板を用いることなく、絶縁体上に配置された電界効果型トランジスタ下にバックゲート電極を形成する。

【解決手段】半導体基板11上に第1半導体層12および第2半導体層13を形成した後、第1半導体層12をエッチング除去することで半導体基板11と第2半導体層13との間に空洞部20を形成し、半導体基板11および第2半導体層13の熱酸化を行うことにより、半導体基板11と第2半導体層13との間の空洞部20内の上下面に絶縁膜21を形成してから、空洞部20内に埋め込み導電体層30を形成する。

(もっと読む)

有機半導体膜を有する半導体装置の製造方法

【課題】 有機半導体層を用いた半導体装置では、各電極の位置合わせとコストの両観点を両立する製造方法が無かった。印刷法では位置ずれが生じるため、絶縁膜を介して下部電極と上部電極が良く位置合せされた電極基板を形成できなかった。位置合わせのためにフォトマスクを使用すると、飛躍的にコストが向上した。

【解決手段】 本発明は、下部電極と、上部電極との位置あわせを自己整合的に行ない、印刷法を用いても位置ずれが発生しない。この為、有機半導体を用いたフレキシブル基板などの半導体装置が印刷法を用いて安価に形成できる。

(もっと読む)

半導体装置の製造方法

【課題】金属半導体化合物からなるゲート電極の抵抗ばらつきの発生を抑制できる半導体装置の製造方法を実現すること。

【解決手段】半導体装置の製造方法は、半導体基板200上にゲート絶縁膜201を形成する工程と、前記ゲート絶縁膜上に、金属と半導体との化合物からなり、所定のゲート長を有するゲート電極206を形成する工程とを含む半導体装置の製造方法であって、前記ゲート電極206を形成する工程は、平均粒径が前記所定のゲート長に対応した所定値以下に制御され、かつ、シリコンおよびゲルマニウムの少なくとも一方を含む、多結晶の半導体膜205を形成する工程と、前記半導体膜205上に金属膜203を形成する工程と、熱処理により前記半導体膜205と前記金属膜203とを反応させ、前記半導体膜205の全体を金属半導体化合物層に変える工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】動作性能および信頼性の高い回路を備えた半導体装置を提供することを課題とする。そして、半導装置の信頼性を向上させることにより、それを備える電子機器の信頼性を向上させることを課題とする。

【解決手段】連続発振レーザ若しくは10MHz以上の周波数で発振するレーザビームを照射しながら一方向に走査して半導体膜を結晶化若しくは再結晶化させる工程と、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用いて形成するフォトリソグラフィー工程と、低電子温度で高電子密度のプラズマを利用した、半導体膜、絶縁膜若しくは導電膜表面の酸化処理、窒化処理若しくは表面改質処理を行う工程とを組み合わせることで上記課題を解決する。

(もっと読む)

電気めっき用治具

【課題】 材料強度が比較的弱い極薄な半導体ウエーハ等の被めっき物に対して伝導板を接触させた場合でも、被めっき物に破損、損傷等が生じる事態を解消できるようにする。

【解決手段】 半導体ウエーハWをボルト21を用いて第1の絶縁板10と第2の絶縁板20との間で挟持する。そして、弾性を有する環状の平板からなる導電ゴム(伝導板)60を、第1の絶縁板10と半導体ウエーハWとの間に介在させ、この導電ゴム60を半導体ウエーハWに弾性的に面接触させる。これにより、導電ゴム60は半導体ウエーハWに対するクッションとして機能し、半導体ウエーハWに加えられる導電ゴム60からの荷重(押付力)を和らげるようにする。

(もっと読む)

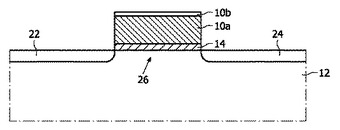

ポリシリコン電極を有する半導体デバイス

MOSトランジスタなどの半導体デバイスを製造する方法。本デバイスは、ポリシリコンのゲート(10)および、半導体基板(12)内に形成されチャネル領域(26)で分離されたドーピング領域(22,24)を備える。後の熱アニールの間にドーパント・イオンが拡散することを阻害するために、半導体基板の露出面を、例えばイオン衝撃によって、アモルファス化する。活性化およびポリシリコン再成長のためのサーマルバジェットが低いことは、ソース/ドレイン領域における急峻なドーピングプロファイルを確実にするために好ましい。結果として、ゲート電極の上部(10b)は、アモルファスのままである。ポリシリコンの下部を用いて低抵抗の接点を作成するために、ゲート電極の上部を除去する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】簡便な方法により、配線の接続信頼性が向上した半導体装置を提供することができ、さらに、トランジスタの閾値電圧を安定させることにより、電気的特性が安定した半導体装置を提供することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、シリコン基板に凹部を形成する工程と、前記凹部の内壁を含む前記シリコン基板の表面に第1絶縁膜を形成する工程と、前記凹部を埋め込むとともに前記シリコン基板全面にポリシリコン膜を形成する工程と、前記凹部の外部の前記ポリシリコン膜を酸化するとともに、前記凹部の外部における前記第1絶縁膜の直下に位置する前記シリコン基板の表面領域と、前記凹部内の前記ポリシリコン膜の表面領域とを酸化して第2絶縁膜を形成する工程と、前記第2絶縁膜を除去して、前記シリコン基板の表面を露出させるとともに前記ポリシリコン膜を前記凹部内に残し、埋込ポリシリコン層を形成する工程と、を含む。

(もっと読む)

半導体装置および配線の製造方法

【課題】 金属多層構造を持つ配線層のストレスを緩和しつつ、ボイドの発生を抑制する。

【解決手段】 スパッタリング法にて絶縁層1上にTiN膜2を堆積した後、Arを用いたプラズマエッチング処理を行うことにより、TiN膜2の表面を逆スパッタして、TiN膜2の表面の結晶性を劣化させた結晶性緩和層2aを形成し、スパッタリング法を用いることにより、結晶性緩和層2aを介してTiN膜2上にAl−Cu膜3を堆積してから、Al−Cu膜3上にTi膜4およびTiN膜5を順次堆積する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 同一の基板に高耐圧のMISFETと低耐圧のMISFETとが形成される半導体集積回路装置の製造工程数を削減する。

【解決手段】 素子分離溝2Aの幅w1が、ゲート電極10Dの延在する方向と直行する方向において、低耐圧のゲート電極となった多結晶シリコン膜の膜厚(t1)と、ゲート絶縁膜8の膜厚(t2)と、ゲート電極10Dの加工上の位置合わせ余裕寸法(t3)との和より大きくなるようにし、平面においてゲート電極10Dと重ならない領域ではその多結晶シリコン膜の膜厚(t1)より大きくなるように素子分離溝2Aを予め形成しておく。

(もっと読む)

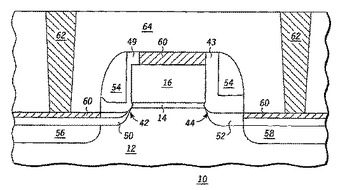

非対称性誘電領域を備える半導体装置の形成方法及びその半導体装置の構造

半導体基板(12)を形成するステップ、半導体基板の上方に第一側面及び第二側面を備えるゲート電極(16)を形成するステップ、及びゲート電極の下方にゲート誘電体を形成するステップを含む半導体装置(10)の形成方法。ゲート誘電体は、ゲート電極の下方でゲート電極の第一側面に隣接した第一領域(42)と、ゲート電極の下方でゲート電極の第二側面に隣接した第二領域(44)と、ゲート電極の下方で第一領域及び第二領域間にある第三領域(14)とを備えている。第一領域は、第二領域よりも薄く、第三領域は、第一領域よりも薄く、更に第二領域よりも薄い。  (もっと読む)

(もっと読む)

タンタル窒化物膜の形成方法

【課題】CVD法により、C、N含有量が低く、Ta/N組成比が高く、Cu膜との密着性が確保されているバリア膜として有用な低抵抗タンタル窒化物膜を形成する方法の提供。

【解決手段】成膜室内に、Ta元素の周りにN=(R,R')(R及びR'は、炭素原子数1〜6個のアルキル基を示し、それぞれが同じ基であっても異なった基であってもよい)が配位した配位化合物からなる原料ガス及び酸素原子含有ガスを導入して基板上で反応させて、TaOxNy(R,R')zを生成し、次いでH原子含有ガスを導入してタンタルリッチのタンタル窒化物膜を形成する。また、得られた膜中にスパッタリングによりタンタル粒子を打ち込み、さらにタンタルリッチとする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】良好なコンタクトを得ることが可能なコンタクトホールを備えた半導体装置を提供する。

【解決手段】単結晶シリコン基板51の表面上にN型またはP型の不純物拡散層52を形成する際に、不純物拡散層52中の不純物濃度を適宜設定する。すると、図2(A)に示すRTN法を用いた熱処理時に、チタンシリサイド層57の成長を適度に抑制して最適化することができる。その結果、不純物拡散層52の接合深さが浅い場合でも、工程4におけるRTN法を用いた熱処理時に、コンタクトホール55の底面部に形成されたチタンシリサイド層57が成長し過ぎて不純物拡散層52を突き抜けるのを防止可能になり、チタンシリサイド層57と単結晶シリコン基板51とが直接接続されてショートするコンタクトリークが生じなくなる。

(もっと読む)

バイポーラトランジスタの製造方法およびそれを用いたバイポーラトランジスタ

【課題】直流電流増幅率の特性が向上した耐電圧、大電力のバイポーラトランジスタの製造方法を提供する。

【解決手段】ベース領域3及びエミッタ領域4の上部に、それぞれベース電極パターン9a、エミッタ電極パターン10aを形成する。形成方法は、電極材料であるAlをスパッタ処理によりAl膜を形成し、リソグラフィ、ドライエッチング処理により電極パターンにする。次に、酸化剤である水、酸素雰囲気下で熱処理を行ない、表面が酸化されたベース電極9b、エミッタ電極10bを形成する。

(もっと読む)

ナノチューブ配線を備えた電子デバイス及びその製造方法

【課題】 ナノチューブ配線を備えた電子デバイス及びその製造方法に関し、製造工程を複雑化することなく、カーボンナノチューブ配線を任意の成長方向に成長させる。

【解決手段】 底面を除く全面が触媒4で覆われた導電体ブロック2のナノチューブ配線が延在しない方向において触媒4と導電体ブロック2との間に成長抑制マスク3を設ける。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の高抵抗化を防ぐとともに、Poly−Siからなるゲート電極を形成する場合と設計事項を変えることなく、不純物イオンのチャネリング現象を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】基板11上に、ポリシリコンからなるゲート電極14を形成する工程と、ゲート電極14の表面を露出させる状態で、基板11上にレジストマスクRを形成する工程と、イオン注入法により、レジストマスクRから露出したゲート電極14の表面側にSiを注入することで、ゲート電極14の表面側に選択的に非晶質層21を形成する工程と、レジストマスクRを除去した後、ゲート電極14の両側の基板11の表面側に不純物イオンを注入して、SD領域を形成する工程と、熱処理を行うことで、SD領域の前記不純物イオンを活性化させるとともに、非晶質層21をポリシリコンに変化させる工程とを有することを特徴とする半導体装置の製造方法である。

(もっと読む)

電子部品用金属材料、電子部品、電子機器、金属材料の加工方法、電子部品の製造方法及び電子光学部品

【課題】 本発明は、電子部品および電子機器またはそれらの製品に使用される金属合金材料、電子および金属材料の加工方法及び電子光学部品に関し、例えば液晶表示素子、各種半導体製品あるいは部品、プリント配線基板、その他のICチップ部品等に適用して、従来に比して低抵抗率であり、更に製造工程中での優位性を保有した安定かつ加工性に優れた電子部品用金属合金材料、この金属材料を使用した電子部品、電子機器を提供する。

【解決手段】 Cuを主成分とし、Wを0.1〜7.0wt%含有し、Al、Au、Ag、Ti、Ni、Co、Siからなる群から選ばれた1又は複数の元素を合計で0.1〜3.0wt%含有してなる合金を金属材料として適用する。この金属材料によれば、CuにWを添加してCuの粒界にMoを均質に混入させることにより、Cu全体の耐候性を向上させることができる。

(もっと読む)

半導体装置と半導体装置の製造方法

ゲート電極高さを抑制し、ゲート絶縁膜を貫通するBの突き抜けを抑制し、ソース/ドレインの寄生容量を抑制することの可能なpMOSトランジスタを作る。 半導体装置の製造方法は、(a)素子分離領域によって画定された第1導電型活性領域を含む半導体基板上にゲート絶縁膜を形成する工程と、(b)前記ゲート絶縁膜上に多結晶半導体のゲート電極層を堆積する工程と、(c)不純物をイオン注入することにより、前記ゲート電極層の上部をアモルファス層に変換する工程と、(d)前記ゲート電極層をパターニングして、ゲート電極を形成する工程と、(e)前記アモルファス層が結晶化しない温度で、前記ゲート電極側壁上にサイドウォールスペーサを形成する工程と、(f)前記ゲート電極と前記サイドウォールスペーサをマスクとして前記第1導電型活性領域に第2導電型不純物をイオン注入し、高濃度ソース/ドレイン領域を形成する工程と、を含む。  (もっと読む)

(もっと読む)

半導体装置およびその作製方法

【課題】新規な構成を有する薄膜トランジスタを提供する。またコンタクトホールの形成を、容易かつ確実に実施する方法を提供する。

【解決手段】断面がテーパー形状であるアルミニウムゲイト電極と、前記ゲイト電極上のゲイト絶縁膜と、前記ゲイト絶縁膜上のチャネル形成領域を構成するI型のアモルファスシリコン膜と、前記I型のアモルファスシリコン膜上の保護膜と、前記I型のアモルファスシリコン膜及び保護膜上のn型のアモルファスシリコン膜からなるソース領域及びドレイン領域と、前記ソース領域に電気的に接続されたアルミニウムソース電極と、前記ドレイン領域に電気的に接続されたアルミニウムドレイン電極と、前記ゲイト絶縁膜上の画素電極と、前記ゲイト電極に電気的に接続されたアルミニウムゲイト配線と、を有し、前記ドレイン領域と前記画素電極とはアルミニウムを介して電気的に接続されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 しきい値が低い高性能の半導体装置およびその製造方法を提供する。

【解決手段】 シリコン基板10の表面部に形成されるCMOSを備える半導体装置1において、PMOS1のゲート電極G4は、窒化タングステンによる表面処理を行なったタングステン上に多結晶シリコン21を堆積させることにより形成する一方、NMOS1のゲート電極G2は、タングステン薄膜上にと多結晶シリコン21を形成した後の熱処理でタングステン薄膜をタングステンシリサイド23に反応させることにより、ゲート電極G2の仕事関数をゲート電極G4の仕事関数からシフトさせる。

(もっと読む)

半導体装置およびその製造方法

【課題】 様々なパターンを有するゲート電極をフルシリサイド化することができる半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板10上にゲート絶縁膜30を形成し、ゲート絶縁膜上に、第1のゲート電極40および第1のゲート電極よりもゲート長またはゲート幅が大きい第2のゲート電極40を形成し、第2のゲート電極の厚みが第1のゲート電極の厚みよりも薄くなるように第2のゲート電極の上部を選択的にエッチングまたは研磨し、第1のゲート電極および第2のゲート電極上に金属膜100を堆積し、第1のゲート電極の全部および第2のゲート電極の全部をシリサイド化することを具備している。

(もっと読む)

141 - 160 / 172

[ Back to top ]