Fターム[4M104EE15]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 材質 (4,070) | ガラス (135)

Fターム[4M104EE15]に分類される特許

101 - 120 / 135

半導体集積回路装置及びその製造方法

【課題】 シリサイド電極を形成する。

【解決手段】 第1及び第2の領域の半導体基板上に、ゲート絶縁膜を介してゲート電極を形成する工程と、第1及び第2の領域に、単一膜若しくは積層状の複数膜からなる第1の絶縁膜と、前記第1の絶縁膜上に形成されたダミー絶縁膜とからなる側壁を、前記ゲート電極に対して自己整合的に、前記半導体基板上に形成する工程と、第1及び第2の領域の前記ダミー絶縁膜を除去する工程と、第1及び第2の領域の全面に第3の絶縁膜を形成する工程と、第1の領域の前記半導体基板及び前記ゲート電極が露出するように、前記第3の絶縁膜を除去し、前記第1の絶縁膜上に第3の絶縁膜を残存させる工程と、前記第3の絶縁膜をマスクとして、前記第1の領域の半導体領域及びゲート電極にシリサイドを形成する工程と、を有することを特徴としている。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド抵抗の低減と接合リークの抑制との両立を実現する半導体装置とその製造方法を提供することを目的とする。

【解決手段】半導体基板101上にフィールド酸化膜102を形成し、活性領域にゲート酸化膜103及びゲート電極104を形成する。次に、ゲート電極104に対して自己整合的に低濃度拡散層105を形成する。次に、半導体基板101の全面にシリコン酸化膜106aを堆積し、全面エッチバックを施してサイドウォールスペーサ106を形成する。このとき、サイドウォールスペーサ106は、ゲート電極104に挟まれた領域において小さく形成されている。次に、サイドウォールスペーサ106に対して自己整合的な高濃度拡散層107を形成する。次に、半導体基板101の全面にNi膜108を堆積し、RTA処理を行い、ゲート電極104の上部及び拡散層の上部に自己整合的にニッケルシリサイド膜109を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 パターンの密度に関係なく、エッチングによる反応生成物がマスク材料の側壁に付着することを抑制可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、所望の目標パターンにパターニングされるべきマスク材料70、80を下地材料10上に堆積し、目標パターンを含みかつそれよりも広い予備パターンにマスク材料をパターニングし、目標パターンにマスク材料をパターニングし、マスク材料をマスクとして用いて下地材料を処理することを具備する。

(もっと読む)

半導体素子の製造方法

【課題】半導体素子の製造方法を提供する。

【解決手段】活性領域が定義された半導体基板210上にゲート電極パターンを形成した後、その上に層間絶縁膜を形成してから、層間絶縁膜のうち活性領域上に置かれた部分をエリアタイプでエッチングしてゲート電極パターン両側に自己整列方式でコンタクトホールを形成し、次いで、このコンタクトホールを通じてイオン注入を実施してソース/ドレイン領域240を形成する半導体素子の製造方法。これにより、熱的負担によりソース/ドレイン領域プロファイルが影響される問題がなく、イオン注入マスク用のフォトレジストパターン形成工程の回数を減らして工程の単純化を図れ、プラグ効果によるトランジスタの特性変動を減少させうる。

(もっと読む)

半導体装置及びその製造方法

【課題】非シリサイド形成領域にシリサイド化防止膜を選択的に形成することによって、シリサイド形成領域に所望のシリサイド膜を確実に形成する。

【解決手段】半導体基板にゲート電極4a、4b、4c及びn型ソース・ドレイン領域9a、9bを形成した後、基板上の全面に炭素含有絶縁膜15及び保護絶縁膜10を順次形成する。その後、レジスト11をマスクにして、シリサイド形成領域AreaAの保護絶縁膜10を除去した後、レジスト11をO2アッシングによって除去する。このとき、シリサイド形成領域AreaAの炭素含有絶縁膜15を改質して改質絶縁膜15aを形成する。その後、改質絶縁膜15aを選択的に除去した後、非シリサイド形成領域AreaBの炭素含有絶縁膜15をシリサイド化防止膜にして、シリサイド形成領域AreaAにシリサイド膜12a、12bを選択的に形成する。

(もっと読む)

半導体素子の製造方法

【課題】タングステンの異常酸化を発生させず且つ素子の電気的特性の劣化を防止することが可能な半導体素子の製造方法を提供する。

【解決手段】半導体基板上の一領域上に、金属膜を含むゲートを形成する段階と、前記金属膜の酸化を誘発させないLPCVD法によって全表面上にLPCVD酸化膜を形成する段階とを含む。

(もっと読む)

半導体装置の製造方法及び半導体装置並びに液晶表示装置

【課題】半導体基板1に対し、その一部を剥離層17に沿って確実に剥離すると共に、ゲート電極8に対向する領域では比較的薄くする一方、その他の領域では比較的厚く形成することにより、TFT50の特性を向上させる。

【解決手段】半導体基板1にゲート電極8を形成するゲート電極形成工程と、半導体基板1の表面とゲート電極8の表面とに対応して形成される表面段差形状をなだらかな表面段差形状に補償するためのBPSG膜15を、ゲート電極8及び半導体基板1を覆うように形成する絶縁膜形成工程と、半導体基板1に対し、BPSG膜15を介して剥離用物質をイオン注入することにより、剥離層を形成する剥離層形成工程と、半導体基板1の一部を剥離層に沿って分離する分離工程とを行う。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 サリサイドプロセスにおけるシリサイド細線化を防ぎ、設計により近い理想的なシリサイド寸法が確保できるポリサイドゲート電極を有する半導体装置及びその製造方法を提供する。

【解決手段】 基板11上にシリコン酸化膜等のゲート絶縁膜13、ポリシリコン層14を順次形成する。このポリシリコン層14を選択的に除去してポリシリコンパターン141を形成し、側壁として絶縁膜16を形成する。その後、ポリシリコンパターン141の上部を所定厚さT1だけ除去する。これにより、絶縁膜16の上部をポリシリコンパターン141の上面よりも高くする。所定厚さT1は、破線に示すように、ポリシリコンパターン141上に形成しようとするシリサイド層19の側部が絶縁膜16の上部で保護されるような形態となるように設定される。

(もっと読む)

半導体装置の製造方法

【課題】 接合特性、抵抗、コンタクト特性のばらつきを低減・防止する。

【解決手段】 図1に示す半導体装置1は、シリコンで構成されたシリコン基板2、シリコン基板2上に形成されたp型ウェル領域3、p型ウェル領域3上に形成されたn+型ソース領域4、n+型ドレイン領域5、p型ウェル領域3上のn+型ソース領域4とn+型ドレイン領域5とに対向して設けられたゲート電極6、ゲート電極6をn+型ソース領域4とn+型ドレイン領域5との接触から絶縁するゲート絶縁膜7およびゲート電極6の側部に設けられたサイドウォール8を有している。ゲート電極6は、CMP法によりポリシリコンが露出しない位置まで、ポリシリコン上に形成されたマスク層の一部を除去し、その後、マスク層を除去してポリシリコン層を露出し、ポリシリコン層をシリサイド化して形成したシリサイドで構成されている。

(もっと読む)

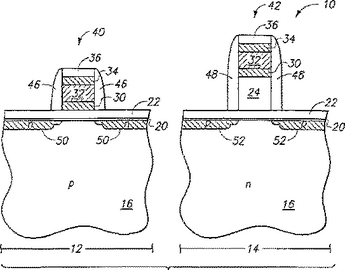

レーザパターニングされた金属ゲートを備えるMOSトランジスタ及びそれを形成するための方法

【課題】 レーザパターニングされた金属ゲートを有するMOSトランジスタ、及びその製造方法。

【解決手段】 本方法は概して、誘電体薄膜上に金属含有材料の層を形成することであって、その誘電体薄膜は無機半導体を含む電気的機能性基板上にある、形成すること;金属含有材料層から金属ゲートをレーザパターニングすること;及び、金属ゲートに隣接する場所にある無機半導体内にソース端子及びドレイン端子を形成することを含む。そのトランジスタは概して、電気的機能性基板と;電気的機能性基板の少なくとも一部の上にある誘電体薄膜と;誘電体薄膜上にあるレーザパターニングされた金属ゲートと;金属ゲートに隣接する、ドープされた無機半導体層を含むソース端子及びドレイン端子とを備える。本発明は、1つ又は複数の従来のフォトリソグラフィ工程をなくすことにより、信頼性がある電気的特性を有するMOS薄膜トランジスタを迅速に、効率的に、及び/又は低コストで提供する点で好都合である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート電極を全て合金化(フルシリサイド化)させる一方で、ソース・ドレイン領域においては合金化反応を抑制することができ、接合リークの発生を抑制することができる半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜2を介してゲート電極を形成した後、ゲート電極の側壁にサイドウォール絶縁膜4を形成する。ゲート電極およびサイドウォール絶縁膜4をマスクとしたイオン注入により、ソース・ドレイン領域6を形成する。その後、ゲート電極を被覆するように半導体基板1上に高融点金属膜8を堆積させ、アニール処理を行う。本発明では、アニール処理において、ゲート電極材料のバンドギャップよりも大きいエネルギーをもつ電磁波を照射する。これにより、フルシリサイド化したゲート電極3aが形成され、ソース・ドレイン領域6中には浅いシリサイド層7aが形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】エピタキシャル成長層によりエクステンション層およびソース・ドレイン層が形成された半導体装置において、合金層と半導体基板間に生じる接合リークを防止して、信頼性を向上させた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1には、活性領域を区画する素子分離絶縁膜2が形成されており、活性領域における半導体基板1上にゲート絶縁膜4を介してゲート電極5が形成されている。ゲート電極5の両側における半導体基板1上には、エピタキシャル成長層により形成された2つのエクステンション層6と、2つのソース・ドレイン層8が積層されている。ソース・ドレイン層8における素子分離絶縁膜2側の端部には、当該端部における合金層の形成を防止する保護層9が形成されている。保護層9から露出したソース・ドレイン層8には、合金層10が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 サリサイド膜を含む半導体装置の信頼性を高める。

【解決手段】 半導体装置の製造方法において、サリサイド膜の形成工程(S30)に先立ち、シリコン基板上の酸化膜の飛散を防止するために酸化膜を保護する処理を行う(S10)。次いで、シリコン基板表面をドライエッチによりクリーニングする処理を行う(S20)。その後、サリサイド膜を形成する(S30)。

(もっと読む)

半導体装置

【課題】低コストで、配線の腐食やコンタクト不良を防止し、ビア・ホールの微細化ができる多層配線構造を有する半導体装置を提供する。

【解決手段】ESD保護素子である縦型ツェナーダイオードのnカソード領域2を取り囲むように第1LOCOS膜4を形成し、nカソード領域2内に第2LOCOS膜11を形成し、この第1、第2LOCOS膜4、11上にビア・ホール22、ビア・ホール23を平坦化のために形成されたSOG膜8に接しないように形成し、このビア・ホール22、23を介して第1配線6と第2配線10を接続することで、SOG膜8による水分、ガス成分などの影響で、配線が腐食したりコンタクト不良を発生することを防止し、低コストで、ビア・ホールの微細化を図ることができる。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】配線の低抵抗性及び信頼性を同時に確保する。

【解決手段】基板110、該基板上に形成されゲート電極124を備えるゲート線、ゲート線上に形成されているゲート絶縁膜140、ゲート絶縁膜上に形成されているソース電極173を備えるデータ線及びソース電極と対向しているドレイン電極175、データ線及びドレイン電極上に形成されている保護膜180、及びドレイン電極と接続されている画素電極190を備える。ゲート絶縁膜及び保護膜の少なくとも一方の下部にケイ素を含むカバー層801、803を備えている。これにより、接着性が向上し、配線抵抗を低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】 ゲートシリサイドの断線を抑制することができる半導体装置の製造方法を得る。

【解決手段】 半導体基板上に絶縁膜を形成する工程と、絶縁膜に開口を形成する工程と、開口の底部で露出している半導体基板の表面にゲート酸化膜を形成する工程と、全面にポリシリコン膜を形成して開口を埋め込む工程と、開口を含む領域を覆うようにポリシリコン膜上にフォトレジストを形成する工程と、フォトレジストをマスクとしてポリシリコン膜及び絶縁膜を異方性エッチングして、ゲート電極と、ゲート電極の下部の側壁を覆うサイドウォールを形成する工程と、フォトレジストを除去する工程と、ゲート電極及びサイドウォールをマスクとして半導体基板に斜め方向からイオン注入してエクステンション領域を形成し、垂直方向からイオン注入してソース・ドレイン領域を形成する工程と、ゲート電極の表面及び半導体基板の表面に金属シリサイド膜を形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 接合リーク電流の増加を防止し、ゲート電極の層抵抗を低減可能な半導体装置の製造方法を提供する。

【解決手段】 高融点金属を材料に含むゲート電極を有する半導体装置の製造方法であって、ゲート電極を形成した後、露出したゲート電極の側面を覆うための酸化膜を形成するために所定の温度で酸化する初期酸化を行うステップと、初期酸化の後、初期酸化よりも高温で酸化する追加酸化を行うステップとを有するものである。

(もっと読む)

半導体MOS装置及びCMOS装置、コンデンサ、及び製造方法

回路装置の作製方法を提供する。導電性にドープされたシリコンと誘電材との間に厚さ20Å以下(または70以下のALDサイクルで生じた厚さ)の金属含有材を形成する。導電性にドープされたシリコンとしてn型を用いることができ、誘電材は高k誘電材を用いることができる。金属含有材は誘電層上へ直接形成でき、導電性にドープされたシリコンは金属含有材上へ直接形成できる。回路装置はコンデンサ構造体あるいはトランジスタ構造体とすることができる。回路装置がトランジスタ構造体である場合はCMOS装置中へ組み入れることができる。本発明による種々装置はメモリ構造体中へ組み入れられる他、電子システムへも組み入れることができる。  (もっと読む)

(もっと読む)

炭化ケイ素デバイス用のはんだ付け可能上部金属

炭化シリコンが、その表面に少なくとも1つの電源電極と、少なくとも1つのパッシベーション層とを有し、はんだ付け可能コンタクトが電源電極に形成され、かつパッシベーション層は、はんだ付け可能コンタクトを囲んでいるが、はんだ付け可能コンタクトから隔離されており、それによって隙間を形成している。 (もっと読む)

半導体装置及びその製造方法

【課題】 微粒子とこの微粒子に結合した有機半導体分子とによって導電路が形成され、その導電性が電界によって制御されるように構成された半導体装置及びその製造方法であって、デバイス構造を工夫することによって性能が向上した半導体装置及びその製造方法を提供することにある。

【解決手段】 金などの微粒子10と、この微粒子に結合した有機半導体分子13との結合体を電極2の上に層状に形成し、電極2の反対側の結合体層の面上に電極6を設け、電極2と電極6との間の結合体層の膜厚方向に形成された導電路の導電性を、ゲート電極4を通じて制御する縦型電界効果トランジスタを形成する。上記結合体層では微粒子10と有機半導体分子13とが交互に結合したネットワーク型の導電路が形成される。この導電路では、有機半導体分子内の導電路が微粒子内の導電路によって連結され、有機半導体分子内の移動度を最大限に利用することができる。

(もっと読む)

101 - 120 / 135

[ Back to top ]