Fターム[4M104FF22]の内容

半導体の電極 (138,591) | 構造 (12,435) | コンタクトホールの孔埋め構造 (1,175) | 2以上の物質で孔埋め (943)

Fターム[4M104FF22]の下位に属するFターム

側面のみ他物質で処理 (58)

Fターム[4M104FF22]に分類される特許

21 - 40 / 885

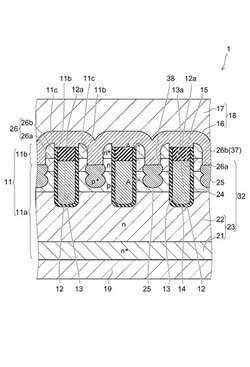

半導体装置及びその製造方法

【課題】高集積化が容易な半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、第1導電形の半導体基板の上面に複数本のトレンチを形成する工程と、前記トレンチの内面上にゲート絶縁膜を形成する工程と、前記トレンチ内の下部にゲート電極を埋め込む工程と、前記トレンチ内の上部に絶縁部材を埋め込む工程と、前記半導体基板の上層部を除去することにより、前記半導体基板の上面から前記絶縁部材を突出させる工程と、前記突出した絶縁部材を覆うように、マスク膜を形成する工程と、前記マスク膜における前記絶縁部材の側面上に形成された部分をマスクとして、前記半導体基板に不純物を注入することにより、第2導電形のキャリア排出層を形成する工程と、を備える。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置

【課題】リーク電流の少ないダイオードを提供する。

【解決手段】実施形態の半導体装置は、AlXGa1−XN(0<x<1)またはInyAl1−yN(0≦y≦1)からなる第1の半導体層2と、第1の半導体層の同一面上に、ノンドープ、n型又はp型のGaNからなる第1の電子誘起領域1、絶縁膜5とアノード電極7と、第1の電子誘起領域上にカソード電極を備え、第1の電子誘起領域、絶縁膜とアノード電極は第1の半導体層と接合し、絶縁膜は第1の半導体領域とアノード電極の間で、第1の半導体層と接合し、アノード電極と第1の半導体層との接合はオーミック接合であり、カソード電極と第1の電子誘起領域との接合はオーミック接合であることを特徴とする。

(もっと読む)

プラズマ処理による酸化物又は他の還元可能な汚染物質の基板からの除去

【課題】VLSI技術及びULSI技術において多段相互接続は、アスペクト比の高いバイアや他の相互接続が注意深く処理されることを要する。これらの相互接続の確実な形成技術を提供する。

【解決手段】窒素と水素を含有する化合物、一般にアンモニアを使用し、次層を上へ堆積するに先立ち相対的に低い温度で酸化物又は他の汚染物質を還元する、プラズマ還元プロセスを提供する。酸化物の層の典型的な物理的スパッタ洗浄プロセスと比較して、層の粘着特性が改善され酸素の存在が減少する。このプロセスは、デュアルダマシン構造、とりわけ銅が応用されている場合の複雑な要求に特に有効であろう。

(もっと読む)

半導体装置とその製造方法

【課題】 実施形態は、製造工程が簡便な手法によって製造した半導体装置を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、実施形態にかかる半導体装置は、基板と、基板上に触媒金属膜と、触媒金属膜上にグラフェンと、前記グラフェン上に層間絶縁膜と、前記層間絶縁膜を貫通するコンタクトホールと前記コンタクトホールにカーボンナノチューブを水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した前記触媒金属膜上に又は前記層間絶縁膜を貫通するカーボンナノチューブを水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した前記触媒金属膜上に備えることを特徴とする。

(もっと読む)

バリアメタル層の形成方法、及び、バリアメタル層の形成装置

【課題】金属層と、金属層上に形成された窒化金属層とからなるバリアメタル層を形成する際に、金属層の抵抗値が高められることを抑えつつ、窒化金属層を形成することのできるバリメタル層の形成方法、及びバリアメタル層の形成装置を提供する。

【解決手段】マルチチャンバ装置10は、Ti層を形成する金属層形成チャンバ13と、Ti層上に、該Ti層を構成するTiCl4と、NH*とを用いてTiN層を形成する窒化金属層形成チャンバ14とを備えている。窒化金属層形成チャンバ14では、TiN層が形成される前に、Ti層の表面が窒化される。

(もっと読む)

半導体装置の製造方法

【課題】SiCOH膜からなる層間絶縁膜に形成された埋め込み用の凹部に銅材を埋め込んで導電路を形成するにあたり、導電路の抵抗を低くすること。

【解決手段】SiCOH膜にプラズマにより凹部を形成すると表面が疎水性になる。このSiCOH膜に水素ガスのリモートプラズマを供給し、Hラジカル及びHイオンにより凹部の表面を親水性に改質する。またプラズマに代えて過酸化水素水を供給してもよく、この場合表面にOH基が形成される。次いで例えばRu3(CO)12ガスとCOガスとを用いてCVDによりRu膜4を成膜し、その後銅材5を埋め込み、CMP処理をして上層側の配線構造を形成する。また改質にあたって、グリム、DMEDAなどを用いてもよい。

(もっと読む)

成膜装置およびバリアメタル形成方法

【課題】スパッタチャンバ内を汚染することなく、バリアメタルを形成することができる成膜装置を提供すること。

【解決手段】実施形態の成膜装置は、第1のプロセスチャンバと、第2のプロセスチャンバと、第3のプロセスチャンバと、を備えている。そして、第1のプロセスチャンバは、スパッタ処理を行うことにより、基板上に第1のバリアメタルを成膜する。また、前記第2のプロセスチャンバは、前記第1のバリアメタルが成膜された前記基板上に第1のガスを導入することにより、前記第1のバリアメタルの上層部を前記第1のガスによって表面処理し、これにより前記第1のバリアメタル上に第2のバリアメタルを形成する。さらに、前記第3のプロセスチャンバは、前記第2のバリアメタルが形成された前記基板にスパッタ処理を行うことにより、前記第2のバリアメタル上に第3のバリアメタルを成膜する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

半導体装置

【課題】端子部のコンタクトホールのテーパー形状を高い精度で制御する。

【解決手段】酸化物半導体層7a、ソース配線13as、ドレイン電極13adを備えた薄膜トランジスタと、第1接続部3c、第2接続部13cおよび第2接続部上に形成された第3接続部19cを備えた端子部とからなる薄膜トランジスタである。第2接続部は、第1および第2絶縁膜5,9に設けられた第1開口部内で第1接続部と接し、第3接続部19cは、保護膜に設けられた第2開口部内で第2接続部と接する。第1開口部は、第1絶縁膜5および第2絶縁膜9を同時にエッチングすることによって形成、第2開口部は、保護膜15を前記第1および第2絶縁膜とは別個にエッチングすることによって形成される。第2接続部13cは、第1開口部における第1および第2絶縁膜の端面を覆い、かつ、第2開口部における保護膜15の端面を覆っていない。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

銅膜作製方法

【課題】下地層との密着性に優れた銅膜を製造する方法の提供。

【解決手段】成膜対象物上に下地層としてチタン膜を形成した後、この下地層を水素ガス雰囲気中で100℃以上200℃未満の温度で熱処理し、次いでその上に銅膜を作製する。このように銅膜を作製した後、さらに水素ガス雰囲気中で100℃以上200℃未満の温度で熱処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

成膜装置および成膜方法

【課題】銅めっき工程の電極に用いるCu堆積膜による貫通孔開口の閉塞状態を適切に制御できる成膜装置を提供する。

【解決手段】成膜装置100は、貫通孔が形成された基板34Bおよび銅放出源35Bを格納する真空チャンバ30と、真空チャンバ30内を所定の真空度に減圧する真空ポンプ36と、基板34Bに印加する電力を発生する電源80と、基板34Bおよび銅放出源35B間の距離の設定に用いる駆動機構と、を備える。銅放出源35Bから放出された銅材料を基板34Bの一方の主面に堆積させ、主面における貫通孔の開口を銅材料からなる堆積膜によって閉塞させるとき、堆積膜による開口の閉塞状態が、上記距離および上記電力に基づいて調整される。

(もっと読む)

炭化珪素半導体装置

【課題】少ない工程数で形成でき、耐熱性に優れた温度検出素子を備える炭化珪素(SiC)半導体装置を提供する。

【解決手段】SiC半導体装置は、SiC基板1に形成された半導体素子と、底面にバリアメタル14を備える配線層を用いて形成したソース電極15およびゲートパッド16と、その配線層のバリアメタル14の一部を用いて形成した測温抵抗体20を備える。

(もっと読む)

成膜装置及び成膜方法

【課題】 タングステン膜を成膜する際に半導体ウェーハがエッチングされることを抑制する成膜装置及び成膜方法を提供することである。

【解決手段】 実施形態に係る成膜装置は、半導体ウェーハを載置するためのステージと、前記ステージ上に載置される半導体ウェーハの周縁部を覆うように配置されるエッジカット部を備え、前記半導体ウェーハ上にタングステン膜を成膜する。前記エッジカット部は、前記半導体ウェーハの周縁部と接触可能に設けられた第1のエッジカット部と、前記第1のエッジカット部に接続され、前記半導体ウェーハと実質的に垂直な方向に上下動可能な接続部と、前記接続部に接続され、前記接続部の上下動により前記半導体ウェーハの内側面に当接するように配置された第2のエッジカット部と、を備える。

(もっと読む)

アルミニウム体を備えた基体の製造方法

【課題】基体上に成膜特性(反射率、及び密着性)に優れた膜状のアルミニウム体を形成することができるアルミニウム体を備えた基体の製造方法を提供する。

【解決手段】基体をプラズマ処理するプラズマ処理工程と、プラズマ処理された基体上に、アミン化合物と水素化アルミニウムとの錯体及び有機溶媒を含有するアルミニウム体形成用組成物を塗布して、上記基体上に上記組成物からなる塗布層を形成させる塗布工程と、上記塗布層に加熱および光照射の少なくともいずれか一方を行うことにより、膜状のアルミニウム体を形成させるアルミニウム膜形成工程と、を含むアルミニウム体を備えた基体の製造方法。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

21 - 40 / 885

[ Back to top ]