Fターム[4M104FF31]の内容

Fターム[4M104FF31]の下位に属するFターム

電極下の複数導電型部(ガードリングを除く) (230)

Fターム[4M104FF31]に分類される特許

221 - 240 / 590

電界効果型トランジスタの製造方法

【課題】酸化物半導体の活性層を、Ga等を主成分とする酸化物を含む層によって確実に保護して電界効果型トランジスタを製造する方法を提供する。

【解決手段】絶縁基板10又は絶縁層14上に、酸化物半導体層16と、該酸化物半導体層上にGaを主成分とする酸化物を含む第1の保護層18及びInを主成分とする非晶質酸化物を含む第2の保護層20をこの順に交互に少なくとも1層ずつ積層した複合保護層21とを有する積層体30をパターン形成する。次いで、積層体上に、対向配置されたソース電極40A及びドレイン電極40Bをパターン形成する。積層体のソース電極及びドレイン電極が形成されている領域以外において、複合保護層の最上部に位置する第2の保護層から、層ごとに順次エッチングして除去することにより、複合保護層の最下部に位置する第1の保護層を露出させる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲートリーク電流の増加及び出力の低下を抑制しながら、コンタクト抵抗を低減することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】電子走行層3aと、電子走行層3a上方に形成された電子供給層4b、5bと、電子供給層4b、5b上方に形成されたゲート電極11gと、ゲート電極11gを間に挟んで形成され、電子走行層3aに電圧を印加するソース電極11s及びドレイン電極11dと、ソース電極11sと電子走行層3aとの間の電流経路に位置し、ソース電極11sと接する第1の化合物半導体層6bと、ドレイン電極11dと電子走行層3aとの間の電流経路に位置し、ドレイン電極11dと接する第2の化合物半導体層6bと、が設けられている。電子走行層3aの表面は(0001)面であり、第1の化合物半導体層6b及び第2の化合物半導体層6bの表面は(000−1)面である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成された電子走行層2と、電子走行層2上方に形成された電子供給層3と、電子供給層3上方に形成されたソース電極7s、ドレイン電極7d及びゲート電極7gと、が設けられている。ソース電極7sと電子供給層3との間の抵抗は、ゲート電極7gから離間するほど低くなっており、ドレイン電極7dと電子供給層3との間の抵抗は、ゲート電極7gから離間するほど低くなっている。

(もっと読む)

SiC半導体装置及びその製造方法

【課題】製造プロセス中に基板の割れや変形が生じることのない低抵抗なSiC半導体装置と、その製造方法を提供することを目的とする。

【解決手段】本発明に係るSiC半導体装置は、第1、第2主面を有する第1導電型のSiC基板1と、SiC基板1の第1主面に形成されたトレンチ4と、前記トレンチ4内に形成されたCNT5と、を備えることを特徴とする。又、本発明に係るSiC半導体装置の製造方法は、(a)SiC基板1の第1主面上にマスク8を形成する工程と、(b)マスク8を用いて選択的に第1主面からSiC基板1にトレンチ4を形成する工程と、(c)マスク8を用いて選択的にトレンチ4内にCNT5を形成する工程と、を備える。

(もっと読む)

ショットキバリアダイオードおよびその製造方法

【課題】リーク特性および耐圧特性が総合的に優れたショットキバリアダイオードを提供する。

【解決手段】 SBD10は、GaN基板11と、GaN基板11の上にエピタキシャル成長されたGaN層13とを備えている。GaN層13には、トレンチ部14が形成され、トレンチ部14の側方にメサ部13aが存在している。メサ部13aの上に、Tiからなる第1電極15と第1電極15を覆う第2電極16とが設けられている。第2電極16は、トレンチ部14の側面,底部全体を覆っている。トレンチ部14の側面14aはm面である。この側面14aは、プラズマエッチングによるパターニング後、ウェットエッチングされている。ウェットエッチングによって、側面14aは、基板面にほぼ垂直な平滑面となっている。この構造により、リーク特性および耐圧特性が総合的に向上する。

(もっと読む)

トレンチ・シールドされた半導体デバイスおよびショットキー・バリア整流デバイスの構造およびそれらを改善するための方法

トレンチ・シールドされた電力用半導体デバイス等の性能を改良するための種々の構造および方法について記載されている。  (もっと読む)

(もっと読む)

複合基板、エピタキシャル基板、半導体デバイス及び複合基板の製造方法

【課題】支持基板上に高品質の窒化物半導体層が形成された複合基板、エピタキシャル基板、半導体デバイス及び複合基板の製造方法を提供する。

【解決手段】複合基板は、支持基板と、窒化物半導体層と、支持基板と窒化物半導体層との間に設けられた接合層とを備える。窒化物半導体層の転位密度は、1×108個/cm2以下である。窒化物半導体層は、接合層側の第1面と、第1面とは反対側の第2面とを有している。第1面における転位密度と第2面における転位密度との差が1×102個/cm2以下である。

(もっと読む)

自立基板、およびその製造方法

【課題】充分な電子デバイス特性が得ることのできる高品質な基板用GaN系半導体自立基板を提供する。

【解決手段】GaN系半導体からなる自立基板であって、前記自立基板の表面に直接Niを金属電極としてショットキーダイオードを形成した場合、電流−電圧特性における理想因子n値が1以上1.3以下となることを特徴とする自立基板。好ましくは、前記ショットキーダイオードを形成した場合、逆方向電圧−5V印加時の電流値が、熱電界放出モデルおよび熱電子放出モデルの計算値の和として計算した理論電流値の50倍以下となることを特徴とする自立基板。

(もっと読む)

ショットキーダイオード

【課題】エピタキシャル層を形成することなくIII族窒化物半導体の支持基体表面の上に直接デバイス領域を形成したショットキーダイオードを提供する。

【解決手段】本発明では、GaN系厚膜材料よりなる支持基体の表面に直接、ショットキーダイオードを形成する。支持基体であるn−GaN(40)の裏面にTi/Alのオーム性電極(50)が、表面に直径100μmのCu/Niのショットキー電極(60)が、直接形成されている。このショットキーダイオードは、理想因子(n値)が1.0以上1.3以下で、且つ、逆方向電圧−5V印加時の電流値がTFEモデルで計算した電流値の50倍以下である。なお、支持基体には、全体がGaN系厚膜材料よりなるバルク基板の他、異種材料の下地基板上にGaN系厚膜材料の層を形成した基体、或は、かかる基体から下地基板を剥離してGaN系厚膜材料の層を分離して得た基板(自立基板)などが含まれる。

(もっと読む)

半導体装置

【課題】コンタクト抵抗低減、ゲート長短縮によるドレインコンダクタンス低下を防止できる半導体装置。

【解決手段】

基板10上に順次配置された窒化物系化合物半導体層からなるバッファ層12,アルミニウム窒化ガリウム層(AlxGa1-xN)(0.1≦x≦1)からなるショットキー層14と、ショットキー層14上に配置されたソース電極16およびドレイン電極18と、ショットキー層14に形成され,チャネルを細線状に分割する複数の溝26と、溝26およびチャネルを横断するゲート電極20とを備え、溝26の側壁部に対してソース電極16との間で、オーミックコンタクトが形成されるため、ソース電極16とショットキー層14との間のコンタクト抵抗が低減でき、ゲート電極20がショットキー層14を囲むように形成され、2DEG層28内のキャリアの閉じ込め効果が高くなるため、ドレインコンダクタンスの低下を防止することができる。

(もっと読む)

エピタキシャルウエハ、窒化ガリウム系半導体デバイスを作製する方法、窒化ガリウム系半導体デバイス、及び酸化ガリウムウエハ

【課題】酸化ガリウムウエハ上設けられ平坦なc面を有する窒化ガリウム系半導体膜を含む窒化ガリウム系半導体デバイスを提供する。

【解決手段】発光ダイオードLEDは、単斜晶系酸化ガリウムからなる主面32aを有する酸化ガリウム支持基体32と、III族窒化物からなる積層構造33とを備える。積層構造33の半導体メサは、低温GaNバッファ層35、n型GaN層37、量子井戸構造の活性層39及びp型窒化ガリウム系半導体層37を含む。p型窒化ガリウム系半導体層37は、例えばp型AlGAn電子ブロック層及びp型GaNコンタクト層を含む。酸化ガリウム支持基体32の主面32aが単斜晶系酸化ガリウムの(100)面に対して2度以上4度以下の角度で傾斜する。この傾斜により、酸化ガリウム支持基体主面32a上にエピタキシャル成長された窒化ガリウム系半導体は平坦な表面を有する。

(もっと読む)

キャパシタ構造及び半導体素子

【課題】キャパシタ構造において、電極間を流れる電流を抑制しつつ電極間の絶縁層を極限まで薄層化する。

【解決手段】ゲート電極Si層10と対向する電極としてのチャネルSi層30との間に所望の電圧を印加した際に、少なくともどちらか一方の電極物質でキャリアが存在しうるエネルギー範囲に存在する両電極物質の全エネルギーバンドについて、少なくとも片方の電極の該当エネルギーバンドの一部に関して、対向して配置した面の面方向の運動量の一致するエネルギーバンドがもう一方の電極の同一エネルギーのエネルギーバンドに存在しないように接合面及び接合面に垂直な軸に関する相対的回転角度を選択することで、電極間のキャリアの透過を抑制する。本発明のキャパシタ構造では、面方向の運動量が一致しないエネルギーバンドが存在するため、このエネルギーバンドが関与するキャリアの透過による電流を抑制することができる。

(もっと読む)

半導体装置、半導体装置の製造方法および半導体装置のリーク電流低減方法

【課題】耐圧特性を向上させ且つリーク電流を低減することが可能な半導体装置、半導体装置の製造方法および半導体装置のリーク電流低減方法を提供する。

【解決手段】HFET100は、支持基板であるサファイア基板101と、サファイア基板101上のバッファ層102と、バッファ層102上のキャリア走行層103と、キャリア走行層103上のキャリア供給層104と、キャリア供給層104上に離間して設けられたソース106sおよびドレイン106dと、キャリア供給層104上におけるソース106sとドレイン106dとの間に設けられたゲート107と、キャリア供給層104上を覆う絶縁膜105と、を備える。キャリア供給層104は、カーボン濃度が2×1017cm−3以上である。

(もっと読む)

窒化物半導体装置

【課題】 簡単な構造で、極めて低い順方向立ち上り電圧と、高い逆方向耐圧特性を有する窒化物半導体装置を提供する。

【解決手段】 基板上に、III−V族窒化物半導体からなる第1及び第2の窒化物半導体層が積層形成されており、第1又は第2の窒化物半導体層に接合する第1のアノード電極と第2の窒化物半導体層に接合する第2のアノード電極を構成する電極金属を適宜選択することによって、第1のアノード電極はオーミック接合を形成し、第2のアノード電極はショットキー接合を形成する。第2のアノード電極は、カソード電極と第1のアノード電極の間に配置される。その結果、第1のアノード電極とカソード電極との電流経路の途中に、キャリアの存在しない領域を形成する構成となっている。

(もっと読む)

半導体装置及びその作製方法

【課題】チャネルが形成される第1半導体層とソース電極層及びドレイン電極層が接する界面のコンタクト抵抗が高くなる一因は、ソース電極層及びドレイン電極層となる金属材料の表面がゴミや不純物によって汚染され、電気抵抗が高い皮膜が形成される現象である。そこで、皮膜の形成から表面が保護されたソース電極層及びドレイン電極層と第1半導体層が接する半導体装置及びその作成方法を提供する。

【解決手段】成膜後の導電膜を大気にさらすことなく、導電膜上に連続して第1半導体層以下の導電率を有する第2半導体膜を含む保護膜を積層し、当該積層膜をソース電極層及びドレイン電極層に形成し、ソース電極層及びドレイン電極層が第2半導体膜を介して第1半導体層に接する。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】窒化物系III‐V化合物半導体からなるHFETのノーマリオフ化を図る。

【解決手段】GaNチャネル層3上に積層されたAl0.2Ga0.8N障壁層4に大きさおよび形状がランダムに形成された凹部8内を埋めるようにゲート電極7を形成している。こうして、2次元電子ガス(2DEG)が発生する面積を減少させ、全体の2DEG密度を低減させて、ノーマリオフ化を図ることができる。その際に、AlGaN障壁層4における転位部分(結晶欠陥部分)を選択的にウェットエッチングすることにより、ダメージを生じさせることなく大きさおよび形状がランダムな凹部8を形成し、チャネル移動度の低下を抑制してチャネル領域でのオン抵抗の増大を防止する。

(もっと読む)

終端構造及びトレンチ金属酸化膜半導体素子

【課題】パワートレンチMOS素子の終端構造を開示する。

【解決手段】MOS素子は、準備される半導体基板に応じて、IGBT、DMOSのいずれであってもよい。終端構造は、トレンチ220と、このトレンチ220の側壁にスペーサとして形成されたMOSゲート240と、スペーサ及び第2のトレンチ220の底面の一部を覆うように形成された終端構造酸化層245と、半導体基板の背面及び表面260にそれぞれ形成された第1及び第2の電極とを備える。トレンチは、活性領域の境界から半導体基板の端部に亘って形成される。トレンチMOS素子は、活性領域に形成される。第2の電極は、導電層間酸化層を介して、活性領域及びスペーサに接続し、空乏領域の湾曲領域が活性領域の境界から所定の長さ離間するように、活性領域、スペーサ及び終端構造酸化層の一部を覆うように形成されている。

(もっと読む)

半導体素子およびその製造方法

【課題】 サドルフィン形態のチャンネルを形成する際に、ゲートパターンとプラグとの間のブリッジ発生を防止することが可能な半導体素子およびその製造方法を提供する。

【解決手段】 半導体素子は、半導体基板と、半導体基板内に活性領域を限定するように形成された素子分離膜と、活性領域および素子分離膜に形成されたゲート用リセスパターンと、リセスパターン内およびリセスパターン上に形成されたゲートパターンと、ゲートパターンを覆うように形成されたゲートスペーサとを含み、ゲート用リセスパターンは、活性領域では第1深さを有し、素子分離膜では第1深さよりも深い第2深さを有し、ゲートパターンと素子分離膜のゲート用リセスパターン上部側面との間には空間が形成されて、ゲートスペーサが前記空間を埋め立てる。

(もっと読む)

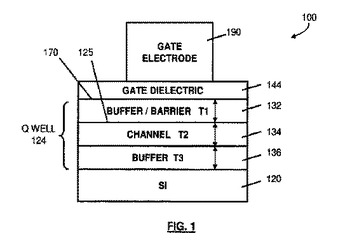

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

エピタキシャルウエハの製造方法および半導体装置の製造方法

【課題】空洞が生じることを抑制し、かつ手間およびコストを低減したスーパージャンクション構造を有するエピタキシャルウエハの製造方法および半導体装置の製造方法を提供する。

【解決手段】エピタキシャルウエハの製造方法は、スーパージャンクション構造12を有するエピタキシャルウエハ10の製造方法であって、以下の工程を備えている。基板11を準備する。基板11上に第1導電型の第1の層を形成する。第1の層にメサ構造を形成する。第1の層のメサ構造の凹部に、液相成長法により第2導電型の第2の層を形成する。半導体装置の製造方法は、以下の工程を備えている。エピタキシャルウエハ10を製造する。エピタキシャルウエハ10上に、半導体層を形成する。

(もっと読む)

221 - 240 / 590

[ Back to top ]