Fターム[4M104FF31]の内容

Fターム[4M104FF31]の下位に属するFターム

電極下の複数導電型部(ガードリングを除く) (230)

Fターム[4M104FF31]に分類される特許

301 - 320 / 590

半導体装置及びその製造方法

【課題】ゲート電極をフルシリサイド化したMISFETを有する半導体装置及びその製造方法に関し、MISFETの特性劣化を引き起こすことなくゲート電極をフルシリサイド化しうる半導体装置の製造方法、並びに、そのような製造方法を用いて形成された優れた特性のMISFETを有する半導体装置を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜18と、ゲート絶縁膜18上に形成された金属シリサイド膜56bと、金属シリサイド膜56b上に形成された金属シリサイド膜56aとを有し、金属シリサイド膜56bにおける金属元素に対するシリコンの組成が、金属シリサイド膜56aにおける金属元素に対するシリコンの組成よりも大きいゲート電極26nと、ゲート電極26nの両側の半導体基板10内に形成された不純物拡散領域対54とを含むトランジスタを有する。

(もっと読む)

半導体装置

【課題】曲げ等の外力が加わり応力が生じた場合であってもトランジスタ等の損傷を低減する半導体装置を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた第1の島状の補強膜と、第1の島状の補強膜上に、チャネル形成領域と不純物領域とを具備する半導体膜と、チャネル形成領域の上方にゲート絶縁膜を介して設けられた第1の導電膜と、第1の導電膜及びゲート絶縁膜を覆って設けられた第2の島状の補強膜とを有している。

(もっと読む)

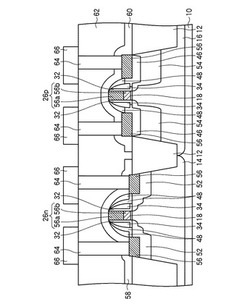

半導体装置及びその製造方法

【課題】 高耐圧性に優れた半導体装置を提供する。

【解決手段】 P型の半導体基板1上に形成されたN型の第1ドレインドリフト領域4と、第1ドレインドリフト領域4よりも底面の深さ位置が深く、且つ同領域4と連続するように形成された、同領域4より高濃度のN型の第2ドレインドリフト領域5と、第2ドレインドリフト領域5に接触して形成された、同領域5より高濃度のN型のドレイン領域7と、第1ドレインドリフト領域5と離間して半導体基板1上に形成されたN型のソース領域6と、半導体基板1の上層に形成されたゲート絶縁膜2と、ソース領域6のドレイン領域4側の端部上方から、第1ドレインドリフト領域4のソース領域6側の端部上方にかけて、ゲート絶縁膜2の上層に形成されたゲート電極3と、を備える。

(もっと読む)

ヘテロ接合電界効果型トランジスタおよびその製造方法

【課題】ソース/ドレイン電極の下側のポテンシャル障壁を低くすることにより、寄生抵抗の増大を防止することを目的とする。

【解決手段】本発明に係るヘテロ接合電界効果型トランジスタは、窒化物半導体からなるヘテロ接合電界効果型トランジスタであって、チャネル層30と、チャネル層30上にスペーサ層40を介して形成されたバリア層50を備える。そして、バリア層50上に形成されたゲート電極80と、バリア層50上に、ゲート電極80を挟んで形成されたソース/ドレイン電極70とを備える。スペーサ層40は、ゲート電極80の下側の領域に形成され、チャネル層30およびバリア層50のいずれよりもバンドギャップが大きい第1のスペーサ層41を備える。そして、スペーサ層40は、ソース/ドレイン電極70の下側の領域に形成され、第1のスペーサ層41よりもバンドギャップが小さい第2のスペーサ層42を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】電極と半導体基板との界面のコンタクト抵抗を低減した半導体装置を実現する。

【解決手段】半導体装置100は、4H構造の炭化珪素基板10と、基板10の表面に形成されている電極6を備えている。基板10の表層に、表面側の端面が電極6に接しているとともに、基板10の表面に対して斜めに伸びている3C構造層12が形成されている。3C構造層12は、4H構造の部分よりもバンドギャップが低い。従って電子は、4H構造の部分に存在する電子は、3C構造層12を通って電極6に達する。すなわち、3C構造層12の厚みが電子の通路の幅を規定する。3C構造層12の厚みによって電子の通路の幅が規定されるので、量子細線効果によって電子は理論値に近い速度で電極に達することができる。電子が電極へ高速で移動できるのですなわちコンタクト抵抗が低減される。

(もっと読む)

半導体装置

【課題】IRを低減することができ、且つ、高速リカバリー特性を有するJBS構造の半導体装置を提供する。

【解決手段】1つの半導体基板上に、ショットキー接合とPN接合とが並列に形成されたJBS構造を有する半導体装置において、粒子線照射により局所ライフタイム制御領域12を形成する。PN接合界面9から局所ライフタイム制御領域12の上面までの距離をL(単位:μm)、ショットキー接合界面が形成された半導体層の厚さをL0(単位:μm)、半導体装置に印加される逆バイアス電圧をVr(単位:V)、第1半導体層2の不純物濃度をND(単位:cm−3)、真空中の誘電率をε0(単位:F・cm−1)、第1半導体層2の比誘電率をεr、単位電荷をq(単位:C)としたとき、PN接合界面9から局所ライフタイム制御領域12の上面までの距離Lが、数式1の関係を満たすことを特徴とする。

【数1】 (もっと読む)

(もっと読む)

複合半導体装置

【課題】1つの半導体基板上に、FRDと、FRDの温度検知素子としての機能を有するSBDとを形成した複合半導体装置を提供する。

【解決手段】1つの半導体基板上に、FRDとSBDとを形成した複合半導体装置において、粒子線照射により局所ライフタイム制御領域を形成する。SBDにおけるショットキー接合界面から局所ライフタイム制御領域の上面までの距離をL(単位:μm)、ショットキー接合界面が形成される半導体層の厚さをL0(単位:μm)、SBDに印加される逆バイアス電圧をVr(単位:V)、前記半導体層の不純物濃度をND(単位:cm−3)、真空中の誘電率をε0(単位:F・cm−1)、前期半導体層の比誘電率をεr、単位電荷をq(単位:C)としたとき、ショットキー接合界面から局所ライフタイム制御領域の上面までの距離Lが、下記数式の関係を満たすことを特徴とする。 (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】p型MISFETまたはn型MISEFETを有する半導体装置において、p型MISFETまたはn型MISEFETのソース/ドレイン電極界面抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板100にp型MISFET200を備える半導体装置であって、p型MISFET200が、半導体基板100中のチャネル領域204と、チャネル領域204上に形成されたゲート絶縁膜206と、ゲート絶縁膜206上に形成されたゲート電極208と、チャネル領域204の両側の、Niを含有するシリサイド層210で形成されたソース/ドレイン電極と、ソース/ドレイン電極と半導体基板100との界面の半導体基板100側に形成された、Mg、CaまたはBaを含有する界面層230を有することを特徴とする半導体装置およびその製造方法。

(もっと読む)

GaN基板の製造方法、GaN基板及び半導体デバイス

【課題】表面における結晶軸のばらつきが少ないGaN基板の製造方法、GaN基板及びこのGaN基板を用いて作製した半導体デバイスを提供する。

【解決手段】GaN基板1の製造方法は、GaN単結晶からなる基板1の表面を、基板1表面における結晶軸x0,x1の方向a0,a1のばらつきに基づいて凹型の球面状に加工する工程を有する。GaN基板1の表面を凹型の球面状に加工することで、加工後のGaN基板1表面において、法線n0,n1に対する結晶軸x0,x1の方向a0,a1のばらつきが減少する。また、結晶軸x0,x1の方向a0,a1のばらつきが減少したGaN基板1を用いて半導体デバイスを製造することにより、一つのGaN基板1から作製される複数の半導体デバイスのデバイス特性を均一にできるため、半導体デバイスを作製する際の歩留まりを高めることができる。

(もっと読む)

半導体基板および半導体装置、半導体装置の製造方法

【課題】低抵抗SiC基板とそれを用いた半導体装置を提供する。

【解決手段】第1の不純物濃度を有する炭化珪素基板(1)と、前記炭化珪素基板上に形成され、第2の不純物濃度を有する第1の炭化珪素層(5)と、前記第1の炭化珪素層の上に形成され、第3の不純物濃度を有する第1導電型の第2の炭化珪素層(2)とを具備し、第2の不純物濃度>第1の不純物濃度>第3の不純物濃度の関係を有する。

(もっと読む)

JBSおよびMOSFET

【課題】N−エピタキシャル層2に注入される正孔の注入量を制限する。

【解決手段】ショットキー接合C1とPN接合C2とが並存する活性領域A1,A2と、その外側に配置されたガードリング領域A3とを具備するJBSにおいて、トレンチ4a,4b,4c,4d,4e,4fの側面および底面を介してN−型エピタキシャル層2にP型不純物の導入・拡散を行うことによって、横方向および縦方向の拡散深さが約0.1〜0.2μmであって濃度が1016/cm3オーダーのP型層5a,5b,5c,5d,5e,5fを形成し、トレンチ4a,4b,4c,4d,4e,4fの底面の酸化膜6に開口を形成し、濃度が1018/cm3オーダー以上のP+型ポリシリコン層7a,7b,7c,7d,7e,7fをトレンチ4a,4b,4c,4d,4e,4fの内部に形成し、P+型ポリシリコン層7a,7b,7c,7d,7e,7fおよびトレンチ4a,4b,4c,4d,4e,4fの底面の酸化膜6の開口を介してP型層5a,5b,5c,5d,5e,5fおよびN−型エピタキシャル層2に重金属を拡散した。

(もっと読む)

III族窒化物半導体結晶基板および半導体デバイス

【課題】抵抗率を低くでき、かつ抵抗率の面内分布の悪化を防止できるIII族窒化物半導体結晶基板を提供する。

【解決手段】III族窒化物半導体結晶基板は、25mm以上160mm以下の直径を有するIII族窒化物半導体結晶基板20aである。III族窒化物半導体結晶基板20aの抵抗率が1×10-4Ωcm以上0.1Ωcm以下である。III族窒化物半導体結晶基板20aの直径方向の抵抗率の分布が−30%以上30%以下である。III族窒化物半導体結晶基板20aの厚さ方向の抵抗率の分布が−16%以上16%以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】 炭素を含有したシリコン層上にシリサイド層が形成された構造を有する半導体装置の特性を向上させる。

【解決手段】 チャネル領域を有し、シリコンを主成分として含んだ第1の半導体領域13と、第1の半導体領域を挟み、炭素を含有したシリコンで形成され、第1の半導体領域に応力を印加する第2の半導体領域21と、第2の半導体領域上に設けられ、不純物元素を含有したシリコン又は不純物元素を含有したSiGeで形成され、第2の半導体領域よりも炭素濃度が低いキャップ層22と、キャップ層22上に設けられ、ニッケルシリサイド又はニッケル−プラチナ合金シリサイドで形成されたシリサイド層23とを備える。

(もっと読む)

DC−DCコンバータ

【課題】寄生インダクタンスの低減を図ることができ、ひいては、スイッチング損失の低減を図ることのできるDC−DCコンバータを提供する。

【解決手段】ゲートドライバ回路10、パワーMOSFET20a、MOSトランジスタ20b、ダイオード30a、出力平滑用コイル40a及び出力平滑用コンデンサ40bを、例えば単結晶シリコンSiからなる同一の半導体チップ60内に近接配置するとともに、この半導体チップ60に形成された配線層を通じてこれら構成要素を電気的に接続する。

(もっと読む)

半導体素子ならびに半導体素子製造法

【課題】炭化珪素を基板とする半導体素子において、基板の欠陥密度に関わらず、炭化珪素エピタキシャル層の非極性面上において、電極/炭化珪素界面、あるいは酸化膜(絶縁膜)/炭化珪素界面の電気的特性と安定性を向上させる手段を提供する。

【解決手段】炭化珪素からなる半導体基板と、前記半導体基板上に形成されるゲート絶縁膜と、前記ゲート絶縁膜上に形成されるゲート電極とを有する半導体素子。前記半導体基板表面の前記ゲート絶縁膜との接合面は、巨視的には非極性面に平行であり、かつ微視的には非極性面と極性面からなり、前記極性面ではSi面またはC面のいずれか一方の面が優勢である。炭化珪素からなる半導体基板と、前記半導体基板上に形成される電極とを有する半導体素子。前記半導体基板表面の前記電極との接合面は、巨視的には非極性面に平行であり、かつ微視的には非極性面と極性面からなり、前記極性面ではSi面またはC面のいずれか一方の面が優勢である。

(もっと読む)

III族窒化物電子デバイス及びIII族窒化物半導体エピタキシャル基板

【課題】低損失な窒化ガリウム系電子デバイスを提供する。

【解決手段】III窒化物系ヘテロ接合トランジスタ11aでは、第2のAlY1InY2Ga1−Y1−Y2N層15は、第1のAlX1InX2Ga1−X1−X2N層13aとヘテロ接合21を成す。第1の電極17は、第1のAlX1InX2Ga1−X1−X2N層13aにショットキ接合を成す。第1のAlX1InX2Ga1−X1−X2N層13a及び第2のAlY1InY2Ga1−Y1−Y2N層15は、基板23上に設けられている。電極17a、18a、19aは、それぞれ、ソース電極、ゲート電極及びドレイン電極を含む。第1のAlX1InX2Ga1−X1−X2N層13aの炭素濃度NC13は1×1017cm−3未満である。第2のAlY1InY2Ga1−Y1−Y2N層15の転位密度Dが1×108cm−2である。ヘテロ接合21により、二次元電子ガス層25が生成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 装置規模の拡大を最小限に抑制しながら、高い耐圧性を維持するとともに、現実的な製造プロセスの下で容易に製造が可能な半導体装置を提供する。

【解決手段】 第1絶縁膜3aを貫通するように基板面に直交する深さ方向に形成される導電膜14aと、第2絶縁膜3bの直上層から底面に達するまで一の外側壁に沿って深さ方向に形成される導電膜14bと、導電膜14bの底面の深さ位置から絶縁膜3a及び3bに挟まれた領域に係る基板2の上面位置に亘って、少なくとも導電膜14bの底面及び絶縁膜3bと接触していない側の外側壁と接触して形成される絶縁膜13bと、絶縁膜13bと3bに挟まれた領域内において底面から上面に向かって、第1導電型の第1不純物拡散領域6、第2導電型の第2不純物拡散領域5a、第1導電型の第3不純物拡散領域7、及び高濃度の前記第1導電型の第4不純物拡散領域17bを備える。

(もっと読む)

半導体装置

【課題】ゲート電極パッド下でのアバランシェキャリアの発生を抑制しつつオン抵抗の低減が図れる半導体装置を提供する。

【解決手段】第1導電型の第1の半導体層と、第1の半導体層の上で互いに隣接して交互に配列された第1導電型の第2の半導体層と第2導電型の第3の半導体層との周期的配列構造と、第3の半導体層の上に設けられた第2導電型の第1の半導体領域と、第1の半導体領域の表面に選択的に設けられた第1導電型の第2の半導体領域とを有し、表面と裏面との間の縦方向に主電流経路が形成される半導体構造部を備え、ゲート電極パッドの下の周期的配列構造の不純物濃度は、第1の主電極(ソース電極)の下の周期的配列構造の不純物濃度より低い。

(もっと読む)

半導体装置

【課題】接触抵抗を低減して電流密度を増大し、高周波動作を可能とする。

【解決手段】シート状炭素構造体10の所望の領域に金属領域11,12および半導体領域13を導入することができる。したがって、金属領域11,12にソース・ドレイン電極部23を、半導体領域13にゲート電極部22をそれぞれ形成することができるため、特に各電極とのコンタクト部では金属・金属接合が形成されて、低抵抗な電気伝導が得られるようになる。これにより、動作速度を高速化し、高い周波数回路への適用も可能となり、特性および信頼性が向上した半導体装置20を実現することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域における歪みを適正に増大させ、キャリア注入速度を向上させて、近時における更なる狭チャネル化にも対応したトランジスタ特性の大幅な向上を可能とする信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極101の側面に、自身は膨張性を有する応力膜からなる第1のサイドウォール111と、第1のサイドウォール111上にこれに比して応力の小さい膜からなる第2のサイドウォール112とが形成されており、半導体層、例えばSiC層104が第2のサイドウォール112により第1のサイドウォール111から離間する。

(もっと読む)

301 - 320 / 590

[ Back to top ]