Fターム[4M104HH14]の内容

Fターム[4M104HH14]に分類される特許

81 - 100 / 783

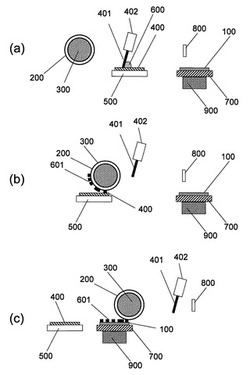

電界効果トランジスタの製造方法及びそれに用いる製造装置

【課題】生産性が高く微細な電界効果トランジスタとその製造方法ならびに製造装置を提供すること。

【解決手段】以下の工程(1)から(3)よりなる印刷工程により前記基板上へラインもしくはスペース最小幅が1から50μmであり、印刷位置精度が100ppm以下の機能性膜の形成を行うことを特徴とする電界効果トランジスタの製造方法としたもの。

工程(1) 版の画線部に相当する溝構造部にドクターブレードを用いたインキング法で、機能性材料が溶媒へ溶解もしくは分散した薬液を充填する工程。

工程(2) 転写シリンダーと前記版を接触させ、前記溝構造部の薬液を前記転写シリンダーへ転移させる工程。

工程(3) 前記転写シリンダー上の薬液を前記基板の所定の位置へ転写し、機能性膜の形成を行う工程。

(もっと読む)

半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】隔壁形成プロセスを省き、かつ、塗布法により半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタを提供する。

【解決手段】基板上に形成された梯子状の凸部を有するゲートバス電極と、ゲートバス電極の表面形状に沿うように当該ゲートバス電極上および基板上に形成されたゲート電極と、ゲート電極の凹凸に沿うようにゲート電極上および基板上に形成されたゲート絶縁体層と、ゲート絶縁体層の凹部内に形成された半導体層と、半導体層の中央に形成された保護膜と、半導体層の両端部で接続されたソース電極とドレイン電極とを備える。

(もっと読む)

配線の形成方法

【課題】側壁転写プロセスを用いて被加工膜を形成する場合に、従来に比して工程数を減少させ、製造コストの上昇を抑えることができる配線の形成方法を提供する。

【解決手段】実施形態によれば、まず、被加工膜11上にマスク膜12と所定の形状のパターンの芯材膜13とを形成し、その上にスペーサ膜14を形成する。ついで、スペーサ膜14を後のエッチング時のマスクとして残す位置から所定の距離の範囲にスペーサ膜14が位置するようにダミーのスペーサ膜143と、芯材膜13の側壁に側壁パターンとをリソグラフィ技術とエッチング技術とを用いて形成する。その後、芯材膜13を除去し、ダミーパターンが除去されるまでスペーサ膜14をエッチングし、所定の範囲に他のスペーサ膜14が存在しない位置にパターン変質部21を生成する。そして、パターン変質部21を除去し、スペーサ膜14をマスクとしてマスク膜12と被加工膜11をエッチングする。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクトと素子領域間にかかる電界を緩和し絶縁破壊を防ぐ。

【解決手段】実施形態の半導体装置は、基板上第1方向に延伸し並列し高さが同じ第1〜4分離、第1、2分離間の低い第1領域、高さが等しい第2、3分離間の第2領域、第3、4分離間の第3領域、第1領域上面、第1分離の第2分離に対向した側面および上面の一部、第2分離の第1分離に対向した側面および上面の一部に接する第1電極15−1、その第2方向で第3領域上面、第3分離の第4分離に対向した側面および上面の一部、第4分離の第3分離に対向した側面および上面の一部に接する第2電極15−2を有す。半導体装置は、第1電極の第2方向とは異なる方向に位置し第2領域上面、第2分離の第3分離に対向した側面および上面の一部、第3分離の第2分離に対向した側面および上面の一部に接する第3電極を有す。

(もっと読む)

半導体装置及びその製造方法

【課題】本実施形態は、ゲートパターン加工時のアスペクト比を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板上に、ゲート絶縁膜と下部ゲート電極と電極間絶縁膜と上部ゲート電極とハードマスクとを順次形成し、選択トランジスタの形成予定領域に、ハードマスクと上部ゲート電極と電極間絶縁膜とを貫き、下部ゲート電極まで達する溝を形成し、溝の中に選択的に下部ゲート電極の結晶構造から影響を受けつつ結晶成長させることにより、特定の結晶配向を優先的に持つ結晶構造を有し、且つ、下部ゲート電極と上部ゲート電極とを電気的に接続する接続層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細なパターンを含む半導体装置の信頼性を向上する。

【解決手段】本実施形態の半導体装置は、素子形成領域100内の半導体素子と、素子形成領域100内から引き出し領域150内に延在する複数の配線WLと、引き出し領域150内の配線WLに接続されるコンタクト部39と、を具備し、配線WLは、n番(nは1以上の整数)の側壁膜のパターンに対応する(n+1)番目の側壁膜のパターンに基づいて形成され、配線WLの配線幅WW又は素子形成領域150内の配線間隔WDに対応する第1の寸法は、リソグラフィの解像度の限界寸法より小さく、露光波長がλ、レンズの開口数がNA、プロセスパラメータがk1で示される場合、第1の寸法は、(k1/2n)×(λ/NA)以下であり、引き出し領域内で互いに隣接する配線WLの間隔WC2に対応する第2の寸法は第1の寸法より大きい。

(もっと読む)

半導体装置の製造方法

【課題】露光パターンのピッチの1/4のピッチのパターンを形成する方法でありながら、形成されたパターンの本数を4の倍数以外の数にする。

【解決手段】第2のパターンおよび第2のマスクパターンを覆うと共に第1の膜の上に第3の膜を形成する工程と、第3の膜をエッチバック処理することにより、第2のパターンおよび第2のマスクパターンの側壁に第1の側壁ラインパターンおよび第1の側壁マスクパターンをそれぞれ形成する工程と、第2のマスクパターンおよび第1の側壁マスクパターンを覆うように第3のマスクパターンを形成する工程と、第3のマスクパターンをマスクとし、第2のパターンを第1の側壁ラインパターンに対して選択的にエッチングして除去した後、第3のマスクパターンを除去する工程とを備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

パターン形成方法及びパターン形成装置

【課題】所定のパターン形成予定部に対応した良好なパターン形成をすることができるパターン形成装置及びパターン形成方法を提供することである。

【解決手段】実施形態のパターン形成方法は、インクジェット方式により対象物のパターン形成予定部の周りに撥液性を有するコーティング材を塗布する表面処理工程と、前記表面処理工程の後にインクジェット方式により前記対象物の前記パターン形成予定部にパターン形成用材を塗布するパターン形成工程と、を備える。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置および半導体装置

【課題】配線溝へのめっきの埋め込み性を安定させることができる半導体装置の製造方法等を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、めっき処理によって金属膜を埋め込んで検査パターン10を形成する形成工程と、検査パターン10の特性を検出する検出工程と、検出工程によって検出された検査パターン10の特性に基づいて、前記めっき処理の条件を調整する調整工程とを含む。前記形成工程は、3層以上の配線層11〜13に亘って形成され、かつ中間層にスタックドビア22を有するパターンを、前記検査パターン10として形成する。

(もっと読む)

半導体装置の製造方法

【課題】実施形態によれば、芯材除去後の側壁材の倒れを防ぐ半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、上端と下端との間にくびれた部分を有する芯材20を、下地層上に形成する工程を備えている。また、半導体装置の製造方法は、芯材20の側壁に、芯材20とは異なる材料の側壁材16を形成する工程を備えている。また、半導体装置の製造方法は、芯材20を除去して、側壁材16を下地層上に残す工程を備えている。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

81 - 100 / 783

[ Back to top ]