Fターム[4M104HH14]の内容

Fターム[4M104HH14]に分類される特許

161 - 180 / 783

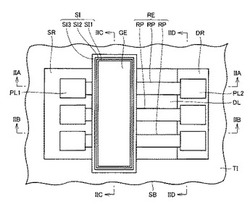

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

シーケンシャル化学気相成長法

【課題】本発明は、高い反応性をもつガス(ラジカル)を利用できるようにラジカル発生装置を用いて、いかなる元素の薄膜の成長をも容易に行うことができる方法を提供する。

【解決手段】複数のサイクルを含むシーケンシャル気相成長法による、基板上へのAl2O3薄膜の成長方法において、それぞれのサイクルは、ガス状のトリメチルアルミニウム(TMA)にパーツを接触させること、ガス状のTMAの供給を停止すること、チャンバからガス状のTMAを除去すること、及び原子状酸素にパーツを接触させることを含む。

(もっと読む)

半導体装置

【課題】並列に並ぶゲートパターンを有する半導体装置において、ゲートパターンのレイアウトを工夫することによって、光近接効果を補正しつつ、集積度を向上させる。

【解決手段】並列に並ぶゲートパターン21,22の端部と、並列に並ぶゲートパターン23,24の対向端部とにおいて、ゲートパターン21の端部はゲートパターン22の端部よりもゲートパターン23,24の方に突き出ており、ゲートパターン24の対向端部はゲートパターン23の対向端部よりも、ゲートパターン21,22の方に突き出ている。引っ込んでいる方の、ゲートパターン22の端部およびゲートパターン23の対向端部について、仕上がり形状において後退が生じない程度に、補正量を大きく設定することができる。

(もっと読む)

積層構造体、多層配線基板、アクティブマトリックス基板、画像表示装置、及び積層構造体の製造方法

【課題】インクジェット法により形成した微細な導電層の積層構造体、多層配線基板、アクティブマトリックス基板、画像表示装置、及びその製造方法を提供する。

【解決手段】濡れ性変化材料を含む濡れ性変化層を形成し、その一部にエネルギーを付与して、低表面エネルギー部を隔て互いに近接した第1の領域43と第2の領域44を含む高表面エネルギー部を形成し、導電性材料を含有する機能液61を第1の領域43にインクジェット法を用いて選択的に滴下し、機能液61を乾燥させて高表面エネルギー部上に導電層を形成する。その際、第1の領域43の中心位置と機能液61の滴下中心位置の距離Xは、機能液の飛翔時の直径D、機能液の着弾位置ばらつきα、第1の領域の幅L、第1の領域と第2の領域との間隔Sとして、X<±(L+2S−D−2α)/2(但し、L+2S>D+2α)、及び、X<±(L+D−2α)/2(但し、L+2D>D+2α)で表される。

(もっと読む)

電子デバイスの製造方法

【課題】カーボン膜の抵抗率を低減することができる電子デバイスの製造方法を提供する。

【解決手段】基板11が載置されたチャンバ4内に炭素を含有する原料ガスを供給する。基板11の周囲からチャンバ4内のアノード1に向けて電子を放出させてチャンバ4内にプラズマ14を発生させ、基板11上にグラファイト、グラフェン等のカーボン膜を形成する。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

半導体装置及び電子機器

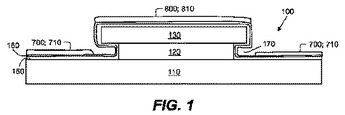

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極またはドレイン電極は、第1の導電層と、第1の導電層の端面よりチャネル長方向に伸長した領域を有する第2の導電層と、を含み、第2の導電層の伸長した領域の上に、前記伸長した領域のチャネル長方向の長さより小さいチャネル長方向の長さの底面を有するサイドウォール絶縁層を有する半導体装置である。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】エミッタメサの加工精度を損ねることなく、HBTの高速性および信頼性が向上できるようにする。

【解決手段】エミッタメサの部分の側面およびレッジ構造部105aの表面には、これらを被覆するように、SiNからなる第1絶縁層108が形成されている。また、第1絶縁層108の周囲には、酸化シリコンからなる第2絶縁層109が形成されている。第2絶縁層の下端部には、レッジ構造部1105aが形成されている領域より外側に延在し、第1絶縁層108およびレッジ構造部105aの側方のベース層104との間に空間を形成する庇部109aが形成されている。

(もっと読む)

半導体回路パターンの形成方法

【課題】スループットを短縮し、所望の回路パターンを形成することが可能な半導体回路パターンの形成方法を提供する。

【解決手段】半導体基板上に被エッチング膜を形成し、この被エッチング膜上に現像液溶解性膜を形成する。次に、現像液溶解性膜上にフォトレジスト膜を形成し、フォトマスクを介してフォトレジスト膜を露光する。さらに、現像液を用いてフォトレジスト膜を現像する。この工程では、フォトレジストパターンの下側の現像液溶解性膜を、アンダーカット状の残存部分を残すように溶解させる。次に、フォトレジスト膜を覆うように耐エッチング膜を形成したのち、フォトレジスト膜を除去することにより、被エッチング膜上に、フォトレジスト膜の開口部に対応する耐エッチング膜のパターンを形成するリフトオフ工程を行う。その後、現像液溶解性膜と耐エッチング膜とをマスクとして、被エッチング膜をエッチングする。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

半導体装置の製造方法及びフォトマスク

【課題】半導体記憶装置の製造において、パターン間隔を縮小し、レジスト膜厚、エッチング量等のバラツキに対応する。

【解決手段】半導体装置の製造方法は、基板上に被加工膜を形成する工程(a)、被加工膜上にレジスト膜を形成する工程(b)、フォトマスクのマスクパターン200bをレジスト膜に転写パターン200cとして転写する工程(c)、転写パターン200cを加工する工程(d)を含む。転写パターン200cは、所定間隔を開けて端部同士が対向して直列に並ぶ第1及び第2の転写ラインパターン201c及び202cと、これらに各々並列する第3及び第4の転写ラインパターン203c及び204cと、第2及び第3の転写ラインパターン202c及び203cの端部同士を接続する接続部212とを含む。工程(d)にて、接続部212の少なくとも一部を除去し、第2及び第3の転写ラインパターン202c及び203cを分離する。

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

成膜方法及び成膜装置

【課題】ステップカバレッジが良好で、原料を安定的に供給すると共に原料の劣化を生じさせずに実用的かつ安価に良質な金属膜を形成することができる成膜方法及び成膜装置を提供する。

【解決手段】2価のカルボン酸金属塩と一酸化炭素又はアンモニアとを反応させて1価のカルボン酸金属塩ガスを生成する工程と、基板1上に1価のカルボン酸金属塩ガスを供給して1価のカルボン酸金属塩膜2を堆積させる工程と、1価のカルボン酸金属塩膜2が堆積した基板1にエネルギーを与えて1価のカルボン酸金属塩膜2を分解し、金属膜3を形成する工程とを有する。

(もっと読む)

電極構造体の製造方法および太陽電池

【課題】スパッタリングを利用した場合でも、電極構造体に、微細な凹凸構造を欠点なく正確に、かつ簡便に形成することのできる電極構造体の製造方法、ならびに電極構造体に欠点のない微細な凹凸構造が正確に形成されてなる太陽電池を提供する。

【解決手段】表面に微細な凹凸構造を有するスタンパー1の表面上に、導電体層2を剥離可能に形成し、スタンパー1上の導電体層2と、硬化性材料4とを接触させ、その状態で硬化性材料4を硬化させて、微細な凹凸構造を有する凹凸基層5を形成するとともに、凹凸基層5と導電体層2とを接着し、スタンパー1と、凹凸基層5に接着された導電体層2とを分離し、もって凹凸基層5上に導電体層2を転写して形成し、このようにして、微細な凹凸構造を有する電極構造体10を製造する。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写技術を使用したパターニングの加工性の向上を図る。

【解決手段】ゲート電極MGを形成するための被加工膜8上にCVD法でカーボン膜9aを形成し、続いてSOG膜を形成する。カーボン膜9aをリソグラフィ技術によるレジストパターンでハーフエッチするとともに、幅寸法をWaから半分のWbにスリミングして芯材パターン部9bを形成する。全面にアモルファスシリコン膜14を形成し、エッチバック処理でスペーサパターン14aを形成し、これをマスクとして芯材パターン部9bと共にカーボン膜9aをエッチングしてマスクパターン9を形成する。レジストを芯材パターンとして用いないので高温で加工ができ、加工性が向上する。

(もっと読む)

161 - 180 / 783

[ Back to top ]