Fターム[4M104HH14]の内容

Fターム[4M104HH14]に分類される特許

101 - 120 / 783

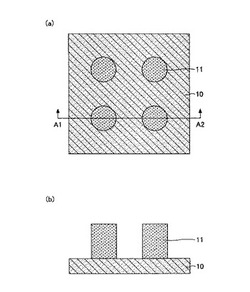

パターンの形成方法

【課題】LELEプロセスよりも少ない工程数で、フォトリソグラフィ技術を2度使用することなく、微細なホール又はトレンチパターンを形成する方法を提供すること。

【解決手段】被処理体の上にレジスト膜を成膜し、成膜した前記レジスト膜をパターニングする、レジスト膜形成工程と、前記被処理体及び前記レジスト膜を被覆するようにスペーサ膜を成膜して、前記スペーサ膜で囲まれた凹部を形成する、スペーサ膜成膜工程と、前記凹部の底面にある前記被処理体及び前記レジスト膜の上面を露出させると共に、前記レジスト膜の側面側に前記スペーサ膜が残るようにエッチングして、前記凹部から第1の開口部を形成する、第1開口部形成工程と、前記レジスト膜を除去することにより第2の開口部を形成する、第2開口部形成工程と、を含むパターンの形成方法。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。または、良好な特性を維持しつつ微細化を達成した半導体装置を提供する。

【解決手段】半導体層を形成し、半導体層上に、単層でなる第1の導電層を形成し、第1の導電層上に、365nm以下の波長の光を用いて第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電層をエッチングして、凹部を有する第2の導電層とし、第1のレジストマスクを縮小させて第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電層をエッチングして、周縁に突出部を有し、且つ突出部はテーパ形状であるソース電極及びドレイン電極を形成し、ソース電極及びドレイン電極上に、半導体層の一部と接するゲート絶縁層を形成し、ゲート絶縁層上の半導体層と重畳する位置にゲート電極を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

半導体装置の製造方法

【課題】めっき膜厚の制御を精度よく行う。

【解決手段】半導体基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含む半導体装置の製造方法において、めっき工程は、複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれる際に、所定の第1の基準電流密度を半導体基板全面における各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度でめっき処理を行う工程(S104)を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、異なる膜特性を有する絶縁膜に形成されるコンタクト形状の制御性を向上させる。

【解決手段】半導体基板に素子領域を形成し、半導体基板の第1の領域上に、第1の絶縁膜を形成し、半導体基板の第2の領域上に、膜応力及びコンタクトの形成の際のエッチング加工時のエッチングレートが、第1の絶縁膜と異なる第2の絶縁膜を形成し、少なくとも第2の絶縁膜において、コンタクトが形成されるコンタクト領域に選択的にUV光を照射し、UV光を照射した後、第1の絶縁膜及び前記第2の絶縁膜をエッチングして前記コンタクトを形成する。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

薄膜トランジスタ回路基板及びその製造方法

【課題】製造工程数を大幅に増加することなく高性能な薄膜トランジスタを備えた薄膜トランジスタ回路基板、及び、薄膜トランジスタ回路基板の製造方法を提供する。

【解決手段】 絶縁基板上に配置されたゲート電極と、前記ゲート電極の上に配置されたゲート絶縁膜と、前記ゲート絶縁膜の上に配置されたポリシリコンによって形成され、前記ゲート電極の直上に位置するチャネル領域、前記チャネル領域に隣接するとともに前記チャネル領域よりも高濃度の不純物を含む低濃度不純物領域、及び、前記低濃度不純物領域に隣接するとともに前記低濃度不純物領域よりも高濃度の不純物を含む高濃度不純物領域を含む半導体層と、前記チャネル領域及び前記低濃度不純物領域の上に配置され、前記チャネル領域の直上の膜厚が前記低濃度不純物領域の直上の膜厚よりも厚い保護膜と、前記高濃度不純物領域に電気的に接続された電極と、を備えたことを特徴とする薄膜トランジスタ回路基板。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、コントローラ150が、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御し、シード層を形成する工程における下地の加熱温度及び処理時間を、アモルファスシリコン膜を形成する工程におけるそれらよりも低く及び短くする。

(もっと読む)

エッチング液組成物

【課題】臭気の発生及び装置や被エッチング基材等の腐食劣化の問題が抑制された、特に酸化インジウム系被膜に対し、充分なエッチング速度とエッチングの選択性を示すエッチング液組成物を提供すること。

【解決手段】(A)2−ヒドロキシエタンスルホン酸又はその塩を、2−ヒドロキシエタンスルホン酸換算で5〜20質量%と、(B)フッ化水素、フッ化アンモニウム、フッ化カリウム、フッ化ナトリウム及びフッ化リチウムから選ばれる少なくとも1種類のフッ化化合物0.05〜5質量%とを含む水溶液からなることを特徴とする金属酸化物被膜のエッチング液組成物。

(もっと読む)

導電膜用エッチング液組成物

【課題】基板上に形成されたモリブデン系導電性薄膜、または、モリブデン系導電性薄膜とアルミニウム系導電性薄膜とが積層された積層導電性薄膜を、効率よく、側面が良好な順テーパー形状となるようなエッチングを行うことが可能なエッチング液、および、該エッチング液を用いたエッチング方法を提供することを目的とする。

【解決手段】(a)リン酸30〜80重量%と、(b)硝酸0.1〜20重量%と、(c)有機酸塩0.1〜20重量%と、(d)水とを含有するエッチング液を用いてエッチングを行う。

また、上記エッチング液を用いて、アルミニウム系導電性薄膜と、モリブデン系導電性薄膜とを備えてなる2層構造の積層導電性薄膜、または、アルミニウム系導電性薄膜と、アルミニウム系導電性薄膜を挟み込むようにその両主面側に配設された第1のモリブデン系導電性薄膜および第2のモリブデン系導電性薄膜を備えてなる3層構造の積層導電性薄膜をエッチングする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極の形状を精度良く形成すると共に、隣り合うゲート電極同士がショートすることを防止する。

【解決手段】開口部を有するマスク16Mを用いて、導電膜15にイオンを注入し、ミキシング膜20Xを形成する。次に、マスクを除去した後、導電膜及びミキシング膜の上に、平面形状がライン形状のレジストパターン21を形成する。次に、レジストパターンをマスクとして、導電膜及びミキシング膜をエッチングし、導電膜15aを有するゲート電極を形成すると共に、ゲート電極のゲート幅方向の側面の上に、ミキシング膜20xを残存させる。次に、熱処理により、ミキシング膜に含まれるイオンと、元素(元素は、導電膜に由来する)とを反応させて、絶縁膜24xを形成する。絶縁膜は、ゲート電極と一体に形成されている。絶縁膜により、ゲート電極と、該ゲート電極とゲート幅方向に沿って隣り合う他のゲート電極との間が電気的に分離されている。

(もっと読む)

タングステンスパッタリングターゲットおよびその製造方法

【課題】基板上に成膜したW膜の膜厚面内均一性を向上させることが可能であり、さらにはパーティクルの発生を減少させることが可能なWスパッタリングターゲットおよびその製造方法を提供する。

【解決手段】Wスパッタリングターゲットは、スパッタリングされる面のX線回折により得られた結晶面(110)のピークの半値幅が0.35以下であることを特徴とする。また、本発明の高純度Wスパッタリングターゲットの製造方法は、高純度W粉末を加圧焼結後、得られた焼結体をターゲット形状に加工後、ロータリー研磨およびポリッシングの少なくとも1種の研磨を施し、さらにエッチングおよび逆スパッタリングの少なくとも1種の研磨を施すことにより仕上げ加工することを特徴とする。

(もっと読む)

配線構造

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、エッチストッパー層を設けなくてもウェットエッチング時の加工性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、薄膜トランジスタの半導体層と、金属配線膜とを有しており、前記半導体層と前記金属配線膜との間にバリア層を有する配線構造であって、半導体層は酸化物半導体からなり、バリア層は、高融点金属系薄膜とSi薄膜の積層構造を有し、Si薄膜は半導体層と直接接続している。

(もっと読む)

半導体装置の製造方法

【課題】パターン疎密差の影響を受けないハードマスク形成法を提供する。

【解決手段】基板101上に、第1から第3の膜111,112,113およびレジスト層114を形成した後、疎部R1と密部R2が存在するパターンを前記レジスト層に形成して前記第3の膜をエッチングする。次に、前記第3の膜及び前記レジスト層をマスクとして、密部R2内では前記第2の膜が残存するが、疎部R1内では前記第1の膜が露出するまで、前記第2の膜を除去する。その後CXFYHZガスを使用して、第5の膜115を、疎部R1内に露出した前記第1の膜上に第1の膜厚T1で形成し、密部R2内に残存する前記第2の膜上には膜厚T1よりも薄い第2の膜厚T2で形成する。膜厚T1の前記第5の膜で疎部R1内に露出した前記第1の膜を保護しながら密部R2内に残存する前記第2の膜を除去し、最後に、前記第3から第5の膜を除去して前記第2の膜をハードマスクとする。

(もっと読む)

微細加工構造及び電子デバイス

【課題】プロセス工程の数が従来のリフトオフ方法より少なく、基板との密着性が良好な薄膜パターンの形成が可能な微細加工方法を提供すること。基板との密着性に優れたパターニングされた被加工薄膜を有する微細加工構造を提供すること。移動度が優れた有機トランジスタの作成が可能な微細加工方法及び電子デバイスを提供すること。

【解決手段】基体1上にレジスト膜2を形成する工程、レジスト膜2をパターン露光する工程、現像を行うことなくレジスト膜2上に被加工薄膜4を形成する工程、レジスト膜2の非露光部2bとその上の被加工薄膜4とをリフトオフする工程、を順次行うことを特徴とする。パターン化された被加工薄膜4aと基板1との間に、露光されたレジストパターン2aが介在していることを特徴とする。

(もっと読む)

101 - 120 / 783

[ Back to top ]