Fターム[4M104HH14]の内容

Fターム[4M104HH14]に分類される特許

201 - 220 / 783

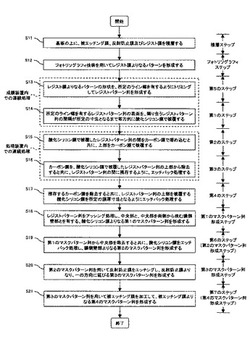

マスクパターンの形成方法及び半導体装置の製造方法

【課題】SWPによりマスクパターンを形成する場合に、反射防止膜のエッチング工程を省略し、マスクパターンのパターン倒れを防止することができるマスクパターンの形成方法を提供する。

【解決手段】レジストパターン列の表面を等方的に酸化シリコン膜で被覆するステップS14と、レジストパターン列の間をカーボン膜で埋め込むと共に、上部をカーボン膜で被覆するステップS15と、カーボン膜を、レジストパターン列の上部から除去すると共に、レジストパターン列の間に残存するようにエッチバック処理するステップS16と、残存するカーボン膜を除去すると共に、レジストパターン列の上部を被覆する酸化シリコン膜をエッチバック処理するステップS17と、レジストパターン列をアッシング処理し、中央部と、中央部を両側から挟む膜側壁部とを有する、酸化シリコン膜よりなる第1のマスクパターン列を形成するステップS18とを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一とする。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成された表示部用配線とを有すればよい。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

半導体装置

半導体装置が半導体基板上のゲートを含む。ゲートの1つの側壁が少なくとも1つの突出部を含んでいてもよく、ゲートの反対側壁が少なくとも1つの凹部を含んでいてもよい。接触部が、ゲート上に配置された絶縁層を通して形成されている。接触部は、ゲートの少なくとも1つの突出部に少なくとも部分的に重なっている。金属層が絶縁層上に配置されている。金属層は、ゲートの第1の側に移動した第1の構造を含む。接触部が絶縁層を通して第1の構造をゲートに電気的に連結するように、第1の構造は接触部に少なくとも部分的に重なっている。 (もっと読む)

ショットキーダイオードの製造方法

【課題】所望の逆耐圧を容易に設定できるショットキーダイオードの製造方法を提供することを課題とする。

【解決手段】

本発明はショットキーダイオードの製造方法において、半導体基板を準備する工程と;前記半導体基板上に第1導電型埋め込み酸化膜及び第1導電型エピタキシャル層を形成する工程と;前記第1導電型エピタキシャル層内に、前記第1導電型埋め込み酸化膜に接続された第1導電型拡散層を形成する工程と;前記第1導電型エピタキシャル層上に絶縁膜を形成する工程と;前記絶縁膜をマスクとしたイオン注入により、ショットキーダイオード端部の電界集中を緩和する第2導電型拡散層を形成する工程と;前記第2導電型拡散層の上部に、シリサイド層(金属層)を形成する工程と;前記絶縁層内に、前記第1導電型拡散層に接続されるコンタクトを形成する工程と;前記絶縁層上に前記コンタクトと接続される配線層を形成する工程とを含むことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジスタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレイン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

半導体装置の製造方法。

【課題】 金属膜やHigh−k膜の膜質の劣化を抑制できる半導体装置の製造方法を提供すること。

【解決手段】 第1の薄膜2上に、第1の薄膜2とは異なる第2の薄膜3を形成し、第2の薄膜3上に、第2の薄膜3とは異なる膜からなる犠牲膜5を形成し、犠牲膜5をエッチングにより所望の間隔を持つパターンに加工し、犠牲膜パターンを形成し、シリコン含有プリカーサー、酸素含有ガスを基板上に間欠的に供給して、犠牲膜パターンにシリコン酸化膜6を被覆し、シリコン酸化膜6をエッチングにより犠牲膜5の側壁上に側壁スペーサー6aを形成し、犠牲膜5を除去し、側壁スペーサー6aをマスクとして用いて第1の薄膜2および第2の薄膜3を加工する。

(もっと読む)

高アスペクト比のフィーチャーへのタングステン堆積方法

【課題】高アスペクト比のフィーチャーをタングステン含有材料で充填する。

【解決手段】部分的に製造された半導体基板上の高アスペクト比のフィーチャーをタングステン含有材料で充填する方法が提供される。ある実施形態においては、当該方法は高アスペクト比のフィーチャーにタングステン含有材料を部分的に充填する工程とフィーチャー空洞から部分的に充填された材料を選択的に除去する工程とを有する。これらの方法を用いて処理された基板においては、高アスペクト比のフィーチャーに充填されたタングステン含有材料のステップカバレッジが改善され、シームの大きさが低減する。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたGe:0.3原子%〜1.2原子%、Co:0.05原子%〜2.0原子%、Laおよび/またはNd:0.1原子%〜0.5 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体絶縁膜及びメタルゲート電極を有する半導体装置において、高仕事関数を得ると共にNBTI信頼性劣化を低減する。

【解決手段】半導体装置100において、基板101上に、高誘電体ゲート絶縁膜109を介してメタルゲート電極110が形成されている。高誘電体ゲート絶縁膜109とメタルゲート電極110との界面におけるメタルゲート電極110の側に、ハロゲン元素が偏析している。

(もっと読む)

配線形成方法

【課題】樹脂基板上に、接着層等を形成するための別の工程を加えることなく、基板との密着性の高い導電性配線を簡単に形成することができる配線形成方法を提供することを目的とする。

【解決手段】樹脂基板1上に、導電性微粒子を含有する分散溶液の塗布層3を形成する工程と、レーザ光6を塗布層3の特定領域に連続的に照射していくことで、導電性微細配線4を形成する工程と、導電性微細配線4以外の領域の材料を除去する工程とを備え、塗布層3の厚さをd、塗布層3の光吸収係数をα、レーザ光6の入射光強度をI0、樹脂基板1上に到達するレーザ光6の透過光強度をI1とするとき、以下の関係式から成り立つことを特徴とする。

log(I1/I0)=−αd

(もっと読む)

半導体装置の製造方法

【課題】新規な半導体装置の製造方法を提供する。

【解決手段】SiN層にPおよびOを注入する工程と、前記SiN層に注入されたPおよびOをH2Oと反応させ、前記SiN層をエッチングする工程とを有する方法により、半導体装置を製造する。特に、半導体装置を形成するにあたり、狭スペースで高アスペクト比の溝サイドウォールを形成する工程や、埋め込み型ビット線を形成する工程に、上記のようにSiN層をエッチングすることができる。

(もっと読む)

半導体装置

【課題】パワーMISFETのゲート抵抗を低減し、装置の特性の向上を図る。

【解決手段】チップ領域CAのY方向にストライプ状に形成された複数の溝の内部の多結晶シリコン膜よりなるゲート部と電気的に接続されるゲート電極GEを、前記ストライプ状の溝の間に形成されるソース領域と電気的に接続されるソース電極SEと同層の膜で形成し、さらに、ゲート電極GEを、チップ領域CAの周辺に沿って形成されたゲート電極部G1と、チップ領域CAをX方向に2分割するよう配置されたゲートフィンガー部G2とで構成し、ソース電極SEを、ゲートフィンガー部G2の上部に位置する部分と、下部に位置する部分とで構成し、ゲート電極GEおよびソース電極SEをバンプ電極を介してリードフレームと接続する。

(もっと読む)

半導体装置の製造方法

【課題】低コストで微細パターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、被加工体10上に第1のレジスト11を形成し、第1のレジスト11をパターニングする工程と、第1のレジスト11のパターニングの後、被加工体10上に第2のレジスト12を形成し、第2のレジスト12に対する選択的露光、ベーク及び現像を行い、その現像時に被加工体10上に残っている第1のレジスト11を除去するとともに、第2のレジスト12の一部を選択的に除去して、第2のレジスト12をパターニングする工程と、パターニングされた第2のレジスト12をマスクにして被加工体10を加工する工程と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】Siピラーの上部の面積を十分に確保でき、さらなるシュリンク(小型化)に対応できる半導体装置を提供する。

【解決手段】半導体基板1上に配置された複数の半導体ピラー部2と、半導体基板1上の第1方向における各半導体ピラー部2間に埋設された絶縁体ピラー部3と、半導体ピラー部2の側壁2cおよび絶縁体ピラー部3の側壁3cに第1方向に沿って連続して設けられた第1配線用凹部4と、半導体ピラー部2の第1配線用凹部4の内壁に設けられた第1絶縁膜と、第1配線用凹部4内に埋設された配線層6とを備える半導体装置とする。

(もっと読む)

基板処理方法

【課題】半導体デバイスの小型化要求を満たす寸法の開口部をマスク層又は中間層に形成することができる制御性に優れた基板処理方法を提供する。

【解決手段】アモルファスカーボン膜51、SiON膜52,BARC膜53及びフォトレジスト膜54が順に積層されたウエハWを処理する基板処理方法であって、CHF3ガスと、CF3Iガスと、H2ガス及びN2ガスの混合ガスから生成されたプラズマによって、フォトレジスト膜54の開口部55のCD値を縮小しつつ開口部底部のSiON膜をエッチングするシュリンクエッチングステップと、開口部55の側壁面へのデポの堆積を促進させて各CD値のばらつきを吸収するばらつき吸収ステップと、開口部の内面に薄膜を形成して各開口部の開口幅を縮小させる開口幅縮小ステップとを1ステップで行う。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写加工技術を用いる場合に、転写用のマスクが非対称な形状となることに起因した不具合を極力防止する

【解決手段】半導体基板1上に、ゲート電極を形成するための膜を積層形成する。第1膜としてシリコン窒化膜8a、第2膜としてシリコン酸化膜9aを積層形成する。シリコン酸化膜9aを加工して芯材パターン9を形成する。ウェット処理によりシリコン窒化膜8aを選択的エッチングして、所定深さまで除去すると共に、芯材パターン9の直下に括れ部8bを形成する。非晶質シリコン膜11aを形成し、エッチバックによりスペーサパターン11を形成する。芯材パターン9をエッチングにより除去すると独立したスペーサパターン11を得ることができ、これをマスクとしてシリコン窒化膜8aをRIEエッチング加工しマスクパターン8を形成する。イオンが斜入しても芯材パターン9の直下部分が偏ったエッチング状態とならない。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

半導体装置の製造方法

【課題】短いゲート長を加工可能にする半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法の一形態は、シリコン基板2上にシリコン酸化膜34を形成し、酸化膜34上に所定幅T1を有する多結晶シリコン膜35aを形成し、少なくとも多結晶シリコン膜35aの両側部を酸化し、所定幅T1よりも狭い幅を有する酸化膜34の部分を多結晶シリコン膜35aの下に残すように、酸化膜34を、多結晶シリコン膜35aの酸化された部分と共にエッチングし、酸化された部分がエッチングされた多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入し、多結晶シリコン膜35aの両側に側壁絶縁膜14を形成し、側壁絶縁膜14が形成された多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入する、工程を有する。

(もっと読む)

201 - 220 / 783

[ Back to top ]