Fターム[4M104HH16]の内容

Fターム[4M104HH16]に分類される特許

801 - 810 / 810

多層配線構造の製造方法

【課題】高集積化、微細化されたパターンにおいて、ビアホール等を良好に埋め込み、かつ電気抵抗率の低い埋め込み型の多層配線構造を提供する。

【解決手段】埋め込み型の多層配線構造の製造方法が、絶縁層に孔部を形成する工程と、孔部の表面に、物理的真空堆積法で、平均膜厚が0.2nm以上で10nm以下である触媒層6、または触媒層の平均膜厚が、触媒層の材料原子の1原子層以上で10nm以下である触媒層6、を形成する工程と、触媒層を触媒に用いた無電解めっき法により、孔部の表面に無電解めっき層7を形成する工程と、無電解めっき層をシード層に用いた電解めっき法で、孔部を電解めっき層8で埋め込む工程とを含む。

(もっと読む)

高いfTおよびfmaxを有するバイポーラ・トランジスタおよびこれを製造する方法

【課題】 ベース抵抗を低減したバイポーラ・トランジスタを提供する。

【解決手段】 高いfTおよびfmaxを有するバイポーラ・トランジスタ(100)は、エミッタ(104)、ベース(120)、およびコレクタ(116)を含む。エミッタは、下部(108)と、この下部を越えて延在する上部(112)とを有する。ベースは、真性ベース(140)および外部ベース(144)を含む。真性ベースは、エミッタの下部とコレクタとの間に位置する。外部ベースは、エミッタの下部からエミッタの上部を越えて延在し、エミッタの上部の下からエミッタの上部の下よりも外側まで延在する連続導体(148)を含む。連続導体は、ベース・コンタクト(図示せず)から固有ベースまでの低電気抵抗の経路を提供する。このトランジスタは、第2の導体(152)を含むことができ、これは、エミッタの上部の下に延在せず、これによって、外部ベースを介した電気抵抗を更に低減する。

(もっと読む)

銅メタライゼーションのためのALD窒化タンタルの集積

窒化タンタル/タンタルバリア層を堆積させるための方法および装置が、集積処理ツールでの使用のために提供される。遠隔発生プラズマによる洗浄ステップの後、窒化タンタルは原子層堆積法で堆積され、タンタルはPVDで堆積される。窒化タンタル/タンタルは、堆積された窒化タンタルの下の導電性材料を露呈するために、誘電体層の部材の底部から除去される。場合によって、さらなるタンタル層が、除去ステップの後に物理気相堆積法で堆積されてもよい。場合によって、窒化タンタル堆積およびタンタル堆積は同一の処理チャンバで生じてもよい。シード層が最後に堆積される。 (もっと読む)

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長の短いゲート電極を有し、しかも低抵抗で高周波特性が優れている半導体装置およびその製造方法を提供する。

【解決手段】少なくともノンドープInGaP層又はノンドープInAlGaP層からなる上層半導体層12と、この上層半導体層直下にGaAs層またはAlGaAs層からなる下層半導体層11を含む半導体基板に、上層半導体層表面から上層半導体層への浸入が、下層半導体層で略停止するショットキーゲート電極15と、このショットキーゲート電極部に接続して第1の電極の抵抗を低減する第2の電極部16からなるT字型ゲート電極を形成する。

(もっと読む)

MOSトランジスタ

【課題】 再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供する。

【解決手段】 半導体基板1に形成したソース及びドレイン領域10a,10bと、酸化膜3bを介して形成したゲート電極5と、前記ソース及びドレイン領域10a,10bとチャネル形成領域30の間に前記ソース及びドレイン領域10a,10bを取り囲むソース及びドレイン低濃度領域6a’,6b’とを有するMOSトランジスタにおいて、前記酸化膜3bを介して前記ソース及びドレイン低濃度領域6a’,6b’に接する導電性である2つのサイドスペーサ9aと、前記ゲート電極5及び前記サイドスペーサ9a上に形成された導電性薄膜15とを有する。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

電極構造体の形成方法及び半導体装置の製造方法

【課題】 ポリメタル構造を有するゲート電極において、ポリシリコン膜と高融点金属膜との間の界面抵抗を低くする。

【解決手段】 半導体基板10上にゲート絶縁膜11を介してポリシリコン膜12を堆積した後、該ポリシリコン膜12の上に、第1の窒化チタン膜14、チタン膜15及び第2の窒化チタン膜16からなるバリア膜を形成する。バリア膜の上にタングステン膜18を堆積して、ポリシリコン膜12、第1の窒化チタン膜14、チタン膜15、第2の窒化チタン膜16及びタングステン膜18からなる電極構造体を形成した後、該電極構造体に対して750℃以上の熱処理を施す。このようにすると、第1の窒化チタン膜14中の窒素がチタン膜15及びポリシリコン膜12に拡散して、ポリシリコン膜12とタングステン膜18との間に新たな窒化チタン膜19が形成されると共に、ポリシリコン膜12の表面に窒化シリコンからなり厚さの小さい反応層20が形成される。

(もっと読む)

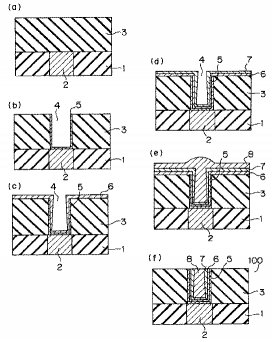

薄膜トランジスタとその製造方法

【課題】 ソース/ドレイン電極材料に銅を用いた場合の加工時のバリアメタル層のアンダーカットに起因する特性不良を防止し、低抵抗配線が充分に実現できるTFTの構造とその製造方法を提供する。

【解決手段】 本発明のTFTの構造は、ガラス基板2上のゲート電極3と、ゲート絶縁膜4と、ゲート絶縁膜4上にゲート電極3に対向配置された半導体能動層5と、半導体能動層5の両端部上に設けられたオーミックコンタクト層6と、各オーミックコンタクト層6を介して半導体能動層5に電気的に接続されたソース電極7、ドレイン電極8とを有している。そして、ソース電極7およびドレイン電極8が銅で形成され、これらソース電極7、ドレイン電極8の下面のうち、各オーミックコンタクト層6の上面上に位置する領域にのみバリアメタル層9が設けられている。

(もっと読む)

Cu−CVDプロセス用原料とCu−CVD装置

【課題】Cu(hfac)(tmvs)カクテルを原料としてCVD法でCu膜を形成するとき、熱安定性を良くし、核発生が良好に誘起され、低温であっても低抵抗でマイクロボイドが発生しにくくする。

【解決手段】Cu−CVDプロセス用原料はCu(hfac)(tmvs)に対してtmvsとHhfac・2H2 Oを添加して作られる液体原料であり、Cu(hfac)(tmvs)に対するtmvsの添加割合が1〜10wt%の範囲に含まれ、触媒であるHhfac・2H2 Oの添加割合が0.1〜0.01wt%の範囲に含まれる。好ましくはtmvsの添加割合が5wt%であり、Hhfac・2H2 Oの添加割合が0.04wt%である。

(もっと読む)

801 - 810 / 810

[ Back to top ]