Fターム[4M106AB17]の内容

半導体等の試験・測定 (39,904) | チェック素子の細部 (1,099) | 形成方法 (210)

Fターム[4M106AB17]に分類される特許

201 - 210 / 210

信頼性評価用半導体装置

【課題】実際の製品により近い複雑な配線パターンを有し、半導体製造プロセスにおける信頼性評価を正確に行うことのできる信頼性評価用半導体装置を提供すること。

【解決手段】配線経路40aは、メモリ回路10からの出力信号をインバータ44によって反転した反転信号と、反転されていない非反転信号との相補関係となる2つの信号を伝搬するように、信号線L1,L2とを有する、配線パターンが二重化された二重化パターンとして形成される。信号線L1においては、インバータ44の出力部にセレクタ61が、セレクタ49の入力部にセレクタ62が、それぞれ介挿されている。

(もっと読む)

デバイス評価用素子、テグ、半導体ウエハー、半導体デバイス評価方法および半導体デバイス製造方法

【課題】 微小な半導体デバイスであっても、短時間で製造工程途中のプロセス評価を実現するデバイス評価用素子等を提供する。

【解決手段】 電子ビームあるいは光によって位置合わせを行うアライメントマークを備え、該アライメントマークから特定距離離れた位置に電子ビーム受容領域を備えた半導体デバイス評価素子を配置する。

(もっと読む)

異物検出用TEG、異物検出装置及び異物検出方法

【課題】 半導体装置が形成されている半導体基板あるいはグレインサイズが大きい金属膜を有する半導体基板においてより確実に異物の検出を行うことができる異物検出用TEG、異物検出装置及び異物検出方法を提供する。

【解決手段】1つの直線状の電気配線4と、その電気配線4の片側に測定電極3を備えた配線ユニット2を備え、その配線ユニット2を測定電極3が互い違いになるように櫛型に配置したTEG1で電気的測定を行う。このTEG1の電気的測定を行うと、導電性の異物が2つ以上の電気配線4と接触している場合には、TEG1の配線ユニット2の間が短絡する。異物が存在しない、あるいは配線ユニット2の間の距離以下の異物しか存在しない場合には、配線ユニット2の間には電気が流れない断線の状態となる。

(もっと読む)

半導体装置の製造方法,半導体装置、エッチング条件の設定方法、導電膜除去条件の設定方法、及びレチクル

【課題】 導電膜が正常にパターニングされて配線が形成されていることを、少ない労力で確認することができるようにする。

【解決手段】 層間絶縁膜8上に導電膜を形成する工程と、前記導電膜をパターニングすることにより、チップ領域1aに配線10a〜10cを形成すると共に、スクライブライン1b上に、複数のダミー配線31〜33を互いに平行に形成する工程と、複数のダミー配線31〜33相互間の抵抗値を測定する工程とを具備する。最外側に位置するダミー配線31,33それぞれに接続するパッド34,35を形成し、このパッド34,35に抵抗計の端子を接触させてもよい。

(もっと読む)

トランジスタの製造プロセス評価方法及び、トランジスタの製造プロセス評価素子

【課題】 トランジスタの電気的特性に異常がある場合に、その不良解析に要する時間を短縮することができるようにしたトランジスタの製造プロセス評価方法及び、トランジスタの製造プロセス評価素子を提供する。

【解決手段】 ウエーハWに形成されたICチップ100に含まれる代表的なMOSトランジスタ1の製造プロセスを評価するための評価素子10であって、MOSトランジスタ1と同一の製造プロセスによってウエーハWに形成された通常のMOSトランジスタ10aと、この製造プロセスからチャネルドープ工程だけを除いた不完全製造プロセスによって当該ウエーハWに形成されたネイティブトランジスタ10bと、を備えたものである。通常のMOSトランジスタ10aの閾値等に異常があった場合に、その値とネイティブトランジスタ10bの閾値等とを比較することで、その原因がチャネルドープ工程に有るか否かを容易に判断することができる。

(もっと読む)

プラズマチャージ評価基板、プラズマチャージ評価方法及び半導体装置の製造方法

【課題】少ない労力でプラズマチャージ量が基準値より多いか否かを評価することができるようにする。

【解決手段】プラズマチャージ評価基板を、半導体装置の製造工程で使用されるプラズマに曝露する工程と、プラズマチャージ評価基板を調べることにより、プラズマが基板に与えるプラズマチャージ量を評価する工程とを具備する。プラズマチャージ評価基板は、半導体基板1に形成された放電領域1aと、半導体基板1上に形成された層間絶縁膜2と、層間絶縁膜2に形成され、放電領域1a上に位置する接続孔2aと、層間絶縁膜2上に形成されたアンテナ用導電膜3と、層間絶縁膜2上に形成され、接続孔2aを介してアンテナ用導電膜3と放電領域1aとを接続するヒューズ用配線4とを備える。ヒューズ用配線4が溶断している場合には、プラズマチャージ量が基準値より多いと評価する。

(もっと読む)

拡散層の横方向拡散の測定

ウェーハ加工プロセスにおける更なるステップとして、ドーピングされた層の横方向急峻性を監視するために、どのような半導体ウェーハ加工プロセスをも変更することができる。一実施形態においては、1つ以上のドーピングされた領域を含むテスト構造が、製品ウェーハに形成され(例えば、1つ以上のトランジスタと同時に)、テスト構造の1つ以上の寸法が測定され、ウェーハのその他のドーピング領域における、例えば、同時に形成されたトランジスタにおける横方向急峻性の判断として使用される。テスト構造におけるドーピングされる領域は、お互いに一定の間隔を置いて規則正しく配置することができ、あるいは、隣接するドーピングされた領域間の間隔を変化させて配置されてもよい。あるいは、または、それに加えて、複数のテスト構造が、単一ウェーハに形成されてもよく、それぞれのテスト構造においては、ドーピングされた領域は、一定の空間的間隔で配置され、異なるテスト構造は、異なる空間的間隔を有する。  (もっと読む)

(もっと読む)

エッチング条件の設定方法、半導体装置の製造方法、及び半導体装置

【課題】 少ない労力でビアホール等を形成するときのエッチング条件が適切か否かを確認できるようにする。

【解決手段】 基準部、該基準部より低地である低地部、及び前記基準部より高地である高地部を有する半導体基板1上に、導電膜2及び層間絶縁膜3を形成し、層間絶縁膜3の表面を平坦化する。層間絶縁膜3をエッチングすることにより、低地部の上方に位置する第1及び第2の接続孔3a、前記基準部の上方に位置する第3の接続孔3b、及び高地部の上方に位置する第4の接続孔3cを同時に形成する。第1〜第4の接続孔3a〜3cそれぞれに、第1〜第4の導電体4a〜4cを埋め込む。層間絶縁膜3上に、第1の導電体3a、第3の導電体4b及び第4の導電体4cを互いに接続する上部電極5bを形成し、上部電極5bと、第1の導電体3aとの間の抵抗を測定する。

(もっと読む)

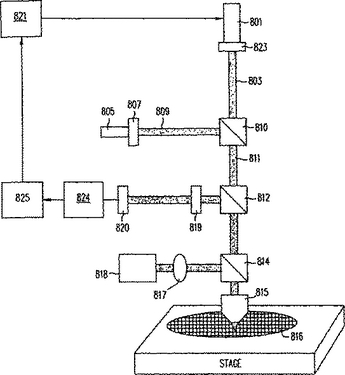

機械学習システムを用いた半導体ウェハ上に形成された構造の光学測定

半導体ウェハ上に形成された構造を、測定装置を用いて測定された第1の回折信号を取得することにより検査する。第2の回折信号は、機械学習システムを用いて生成される。機械学習システムは、第2の回折信号を生成するために、構造のプロファイルを特徴付ける1以上のパラメータを入力として受け取る。第1の回折信号と第2の回折信号は比較される。第1の回折信号と第2の回折信号が一致基準の範囲内で一致する場合、構造の形状は、第2の回折信号を生成するために機械学習システムで使用されたプロファイル又は1以上のパラメータに基づいて求められる。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法及び試験方法

【課題】本発明は、複数の半導体素子が連なった状態で封止され、画像認識により位置決めされて試験に供される半導体装置、半導体装置の試験製造方法及び半導体装置の試験方法に関し、既存のウェーハプローバで認識可能なアライメントマークを容易に形成することを課題とする。

【解決手段】 半導体チップ14の電極を所定の位置に配置された電極パッドに接続するための再配線層18を半導体チップ14上に形成する。ハンダボール22が形成されるメタルポスト16を再配線層の電極パッド上に形成する。再配線18上に、メタルポスト16と所定の位置関係で配置されたアライメントマークを提供するマーク部材24を形成する。マーク部材24はメタルポスト16と同じ材質で形成される。

(もっと読む)

201 - 210 / 210

[ Back to top ]