Fターム[4M106AB17]の内容

半導体等の試験・測定 (39,904) | チェック素子の細部 (1,099) | 形成方法 (210)

Fターム[4M106AB17]に分類される特許

161 - 180 / 210

半導体装置

【課題】 スクライブTEGの電極端子によるLSIチップのウエハ上での取れ数削減を抑制して、低コスト化を実現する。

【解決手段】 半導体素子からなる内部回路が集積して形成されたLSIチップ1と、LSIチップ周辺のスクライブ領域4上に形成され、評価素子5と電極端子6が形成されたスクライブTEGとを備え、スクライブTEGの評価素子5の少なくとも一つとスクライブTEGの電極端子6とが、それぞれスクライブ領域4内の異なる領域に分離して形成され、互いに電気的に接続されている。これにより、スクライブTEGの電極端子と評価素子の接続の制約が緩和され、結果的にスクライブ領域面積の縮小ができ、LSIチップの低コスト化を実現できる。

(もっと読む)

大規模集積回路のウェハおよびその製造方法

【課題】 スクライブライン幅を増加することなく、半導体装置を容易に短時間で評価することができるように改良された大規模集積回路のウェハを提供する。

【解決手段】 第1のスクライブライン12aが延びる方向に、複数個の半導体装置1が並んで半導体装置の列を形成している。半導体装置の列は、第1のスクライブライン12aと直交する第2のスクライブライン12bが延びる方向に複数並んで設けられる。第2のスクライブライン12b内に、各半導体装置1と対になるように、中継回路9が設けられる。中継回路9と半導体装置1は、ポリシリコン配線13で接続される。中継回路9にその一方端が接続された第2層配線6が、第2スクライブライン12b内に延びている。テストチップ3内に形成されたパッド電極4aにその一方端が接続された第3層配線5cが、第1のスクライブライン12a内に延びている。第2層配線6と第3層配線5aは、ビアホール10を介して電気的に接続されている。

(もっと読む)

半導体ウエハ、その製造方法及びマスク

【課題】 半導体素子のパターン寸法を検証する際の検証精度を高め、且つ、その歩留ま りを損なうことなく検証するためのTEGを形成する。

【解決手段】 半導体ウエハの製造にあたり、2つの素子形成領域12と、素子形成領域12を相互に区画するスクライブ線領域13とが1つのレチクルショット11で形成される。各レチクルショット11の4隅のスクライブ線領域13上、及び、中央のスクライブ線領域13上に、スクライブ線領域13の幅の1/2以下の寸法を有するTEG14を形成する。各TEG14には、素子形成領域12内の半導体素子のパターンと同じ形状で、且つ、相互に同一形状のパターンが形成される。各スクライブ線領域13上で隣接する2つのTEG14は、スクライブ線領域13の長手方向に離間して配置される。

(もっと読む)

半導体装置とその製造方法、半導体装置の設計を支援する装置と方法、半導体装置の動作検証方法

【課題】本来の論理機能のための論理回路に加えて、論理機能とは関係のないテスト用のプロービング回路が設けられた半導体装置を提供する。

【解決手段】 半導体装置は、複数の論理回路を有し、所定の論理機能を達成する論理回路部(C11〜C33)と、前記論理回路部に接続されるように設けられた少なくとも1つのプロービング回路(PB)とを備えている。前記プロービング回路は、前記所定の論理機能とは関係が無く、前記プロービング回路の拡散層は、LVP(Laser Voltage Probing)法で使用される。

(もっと読む)

半導体装置及び評価パターンの評価方法

【課題】 薄膜状の評価サンプルに確実に評価パターンを含ませるようにする。また、評価サンプルの薄膜化を図って評価パターンの構造解析精度を向上させる。

【解決手段】 基板上に一列に複数の評価パターン104が形成され、各評価パターン104を含むように基板と垂直な膜状の評価サンプル102が切り取られて評価パターン104の断面観察に供される半導体装置100であって、各評価パターン104の並び方向と評価サンプル102の延在方向がずれるよう構成された。

(もっと読む)

半導体装置の評価用TEG及び評価用マスク

【課題】 半導体装置のプロセスマージンの評価及び信頼性評価を、時間的にもコスト的にも、従来の評価よりも低減するための評価用TEG及び評価用マスクを提供する。

【解決手段】 容量ブロック10毎にMOSFETの寸法が異なり、かつ、容量ブロック10毎に電気測定するための測定用パッド12を有するTEGを形成する。さらに、通常の半導体装置の製品と構成が近くなるように、入力部と、記憶部と、出力部と、電源回路とを有する。

(もっと読む)

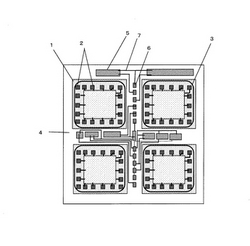

半導体集積回路ウェハ、その試験方法および半導体集積回路部品の製造方法

【課題】 ウェハからの半導体素子の取り数を減少させず、ウェハ段階で複数チップのリークテストを一括して行って良品率を簡単に予測してウェハ検査を簡略化する。

【解決手段】 スクライブライン3上に制御信号用配線31a、電源用配線31bおよび接地用配線31cを配置して、これらをそれぞれブロック内の複数の半導体素子2の各端子21a〜21cにそれぞれ接続させ、ブロック内に設けられたTEG4内の各測定用端子41a〜41cにそれぞれ接続して、ブロック毎に一括してリーク電流を測定する。リーク電流が設定値未満の場合には、ブロック内の半導体素子の良品率が高いと判断して、ウェハ状態で個々の半導体素子の個別テストを省略する。リーク電流が所定値以上の場合には、ブロック内の半導体素子の良品率が低いと判断して、半導体素子2の各端子21a〜21cから、ウェハ状態で個々の半導体素子の個別テストを行う。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線に対する接続孔の位置ずれ量及び位置ずれ方向を精度よく測定することができる半導体装置の製造方法を提供する。

【解決手段】本半導体装置の製造方法では、第1の絶縁膜上に、複数の第1のTEG用配線10dを形成する。第1の絶縁膜上及び複数の第1のTEG用配線10d上に、第2の絶縁膜11を形成する。第2の絶縁膜11に、複数の第1のTEG用配線10dの端部それぞれ上又はその近傍に位置し、前記複数の端部に対する相対位置が同一方向にずれている複数のTEG用接続孔11bを形成する。第2の絶縁膜11上に、複数のTEG用接続孔11bそれぞれに接続する複数の第2のTEG用配線13bを形成する。いずれの第1のTEG用配線10dと第2のTEG用配線13bが相互に導通しているか検査することにより、第1のTEG用配線10dとTEG用接続孔11bの位置ずれが検査される。

(もっと読む)

トランジスタの特性を測定する回路

【課題】 ウエハ上に形成されるトランジスタの特性ばらつきを測定する回路の面積効率を向上させる。

【解決手段】 m×n個のセル回路2がマトリックスに配置されている。各セル回路2は、それぞれ第1および第2のトランジスタを含んで構成される。制御回路3は、セル回路マトリックスの行ごとに対応するセル回路2を制御する。制御回路4は、セル回路マトリックスの列ごとに対応するセル回路2を制御する。各セル回路2において、第1のトランジスタの特性を測定するときは、第2のトランジスタがスイッチとして使用され、第2のトランジスタの特性を測定するときは、第1のトランジスタがスイッチとして使用される。

(もっと読む)

剥離特性評価方法

【課題】 半導体素子における多層絶縁膜の密着性に関する正確な情報が得られる、特に、半導体素子の材料開発、中でも、low−k材の開発に非常に役立つ情報が得られる技術を提供することである。

【解決手段】 基板上に積層された積層膜の剥離特性を評価する方法であって、

剥離特性が対象となる膜の界面に到達する深さの傷を付ける傷付工程と、

前記傷付工程の後、前記傷付部分を覆うように粘着性テープを前記積層膜表面に貼付する粘着性テープ貼付工程と、

前記粘着性テープ貼付工程の後、前記貼付された粘着性テープを引き剥がし、前記対象の膜の界面において剥離する際の力を測定する剥離力測定工程

とを具備する。

(もっと読む)

膜密着力測定方法、膜密着力測定装置、及び電子装置

【課題】 半導体素子における多層絶縁膜の密着具合に関する正確な情報を得ることが出来る技術を提供することである。

【解決手段】 積層膜における膜の密着力を測定する方法であって、

前記積層膜における所定の膜Xを間に挟んで互いに略平行に設けられた導体M1,M2に、各々、電流を流して前記導体間の膜Xに斥力を作用させる斥力作用工程と、

前記積層膜の積層方向に沿って設けられた導体M0に電流を流して抵抗値を測定する膜密着力測定工程とを有する。

(もっと読む)

電気抵抗測定用構造体およびコンタクト抵抗評価方法

【課題】オーミック電極と半導体基板との間のコンタクト抵抗を簡便に、かつ実用上充分な正確度で求めること。

【解決手段】2個のオーミック電極52,52間の電気抵抗より、オーミック電極と半導体基板12とのコンタクト抵抗を求める電気抵抗測定用構造体50において、半導体基板上に、互いに離間して配置されている2個のオーミック電極と、オーミック電極間に設けられていた別オーミック電極の除去痕である矩形のダミー変質層54と、を備えた構造体50が2種類以上形成されており、2種類以上の構造体は、変質層の直線Cに沿う方向の辺の長さの和が、それぞれ異なっていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 FIBを行わなくても半導体素子の特性の検査ができるようにする。

【解決手段】本発明に係る半導体装置の製造方法は、製品用半導体基板に半導体装置を形成する工程と、モニター用半導体基板11にモニター用半導体装置を形成し、該モニター用半導体装置の電気的特性を検査する工程とを具備する。モニター用半導体装置の電気的特性を検査する工程は、モニター用半導体素子上に、絶縁膜20を形成する工程と、絶縁膜20に、半導体装置の接続孔とは異なるレイアウトで配置され、モニター用半導体素子上に位置する第2の接続孔20d,20e,20fを形成する工程と、絶縁膜20上に、第2の接続孔20d,20e,20fを介してモニター用半導体素子に接続する電極22d,22e,22fを形成する工程と、電極22d,22e,22fに検査用の端子を接続して信号を入力する工程とを有する。

(もっと読む)

配線不良検出素子及び配線不良検出方法

【課題】 インライン中及び最終工程後の両方においてオープン/ショートの電気的評価を行うことのできる配線不良検出素子を提供する。

【解決手段】 配線不良検出素子10は、基板と、前記基板上に形成され、電気的にフローティング状態である複数の第1の導体層121−124と、前記複数の第1の導体層の各々と近接して順次取り囲むように設けられた第2の導体層13と、前記第2の導体層の一端部に接続された金属パッド14とから構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】膜厚測定を簡易化出来る半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板10の第1領域に、設けられた第1の半導体層13と、半導体基板10の第2領域上に、絶縁膜11を介在して設けられた第2の半導体層12と、半導体基板10の第3領域上に、絶縁膜11及び第2の半導体層12を介在して設けられた第3の半導体層13とを備え、第3領域内の第3の半導体層13の上面の高さは第2領域内の第2の半導体層12の上面の高さよりも高いことを特徴としている。

(もっと読む)

半導体装置の製造方法

【課題】処理室、搬送室およびロードロック室を備えた半導体製造装置において半導体ウエハ上に付着するマイナス電荷に帯電した異物を検出することのできる技術を提供する。

【解決手段】シリコン単結晶基板9と、その上に形成された、例えば酸化シリコン、窒化シリコンまたは酸窒化シリコンを主成分とする絶縁膜10とによって構成された異物検査用ダミーウエハSWdを用いることにより、プラズマCVD装置の反応室内または搬送室内のマイナス電荷に帯電したSiO微粒子を検出する。

(もっと読む)

半導体不良分析のための分析構造体

【課題】半導体不良分析のための分析構造体を提供する。

【解決手段】半導体基板の所定領域に配置された複数の分析領域と、ゲート電極及び不純物領域を備えながら分析領域に配置される、アレイ構造の半導体トランジスタと、分析領域に配置されて、半導体トランジスタを横方向に連結するワードラインと、ビットライン及びビットラインと不純物領域を連結する垂直配線構造体を備えながら、半導体トランジスタの不純物領域を縦方向に連結するビットライン構造体と、を含む。この時、ビットラインは、分析領域の位置によって異なる高さであることを特徴とする。これにより、配線不良に関する早くて正確な分析が可能であるため、半導体装置の開発期間を最小化できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 感度校正精度の再現性を確保しつつ、異物測定器の感度校正精度を向上させる。

【解決手段】 開口部13が形成された酸化防止膜12をマスクとして半導体基板11の熱酸化を行うことにより、酸化膜にて構成された突起状擬似異物14を半導体基板11に散点状に形成し、この突起状擬似異物14が形成された半導体ウェハを、異物測定器の感度校正を行うための感度チェック用ウェハとして用いる。

(もっと読む)

損傷検出装置、電子素子、及び素子集合体

【課題】 損傷の判断を正確に提供できる技術を提供することである。

【解決手段】 基板と、前記基板に設けられた第1の櫛状導体パターンと、前記第1の櫛状導体パターンとは非導通で前記基板に設けられた第2の櫛状導体パターンとを具備し、

前記第1の櫛状導体パターン及び前記第2の櫛状導体パターンは、その櫛状先端部側が櫛状基部側より外側に位置するよう設けられてなる損傷検出装置。

(もっと読む)

基板及び微小構造物並びに基準スケールの作製方法及び微小構造物の測長方法

【課題】 測長対象物の姿勢に関わらず、正確且つ容易に測長を行うこと。

【解決手段】 測定対象物3が表面5aに形成される基板本体5と、該基板本体5の表面上5aで、測定対象物3が形成される領域近傍に少なくとも一方向に延びるよう設けられた基準スケール6とを備え、該基準スケール6が、集束イオンビームFIBを利用して形成され、予め決められた間隔毎に隣接配置された複数の目盛り7を有している基板2を提供する。

(もっと読む)

161 - 180 / 210

[ Back to top ]