大規模集積回路のウェハおよびその製造方法

【課題】 スクライブライン幅を増加することなく、半導体装置を容易に短時間で評価することができるように改良された大規模集積回路のウェハを提供する。

【解決手段】 第1のスクライブライン12aが延びる方向に、複数個の半導体装置1が並んで半導体装置の列を形成している。半導体装置の列は、第1のスクライブライン12aと直交する第2のスクライブライン12bが延びる方向に複数並んで設けられる。第2のスクライブライン12b内に、各半導体装置1と対になるように、中継回路9が設けられる。中継回路9と半導体装置1は、ポリシリコン配線13で接続される。中継回路9にその一方端が接続された第2層配線6が、第2スクライブライン12b内に延びている。テストチップ3内に形成されたパッド電極4aにその一方端が接続された第3層配線5cが、第1のスクライブライン12a内に延びている。第2層配線6と第3層配線5aは、ビアホール10を介して電気的に接続されている。

【解決手段】 第1のスクライブライン12aが延びる方向に、複数個の半導体装置1が並んで半導体装置の列を形成している。半導体装置の列は、第1のスクライブライン12aと直交する第2のスクライブライン12bが延びる方向に複数並んで設けられる。第2のスクライブライン12b内に、各半導体装置1と対になるように、中継回路9が設けられる。中継回路9と半導体装置1は、ポリシリコン配線13で接続される。中継回路9にその一方端が接続された第2層配線6が、第2スクライブライン12b内に延びている。テストチップ3内に形成されたパッド電極4aにその一方端が接続された第3層配線5cが、第1のスクライブライン12a内に延びている。第2層配線6と第3層配線5aは、ビアホール10を介して電気的に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は一般に大規模集積回路のウェハに関し、より特定的には、スクライブライン幅を増加することなく、半導体装置を容易に短時間で評価することができるように改良された大規模集積回路のウェハに関する。この発明はまたそのような大規模集積回路のウェハの製造方法に関する。より具体的には、半導体装置の製造工程におけるスクライブライン内の配線層の形成技術と、複数の半導体装置の特定電極を電気的に繋ぎ一括テストする評価技術とに関し、さらに具体的には、基板上に設けられる複数の半導体装置をいくつかの電気的に独立したブロックに分割し、各々のブロック毎に、テスト専用チップを繋ぐ配線層の形成技術に関する。

【背景技術】

【0002】

半導体装置のサイズは、微細化の進展とともに縮小し、一方半導体装置を製造する基板は大口径化し、結果として基板1枚当たりに製造される半導体装置の数は増加する傾向にあり、1000ヶ以上ある場合も珍しくは無い。また、製造方法の完成度は向上し、基板1枚当たりの良品半導体装置の比率(歩留まり)は90%を超えている。しかし、このような状況下でも、半導体装置の評価は、基板上に製造された全ての半導体装置に対して実施している。従って、半導体装置の評価時間が多大なものとなり、TAT、評価設備の保有台数に負荷を与えている。さらに、基板からダイシングによって個片化された半導体装置は、テープなどに実装された後、再び評価されている。

【0003】

このような状況下、半導体装置の評価方法について、いくつかの提案がなされている。

【0004】

特許文献1においては、基板レベルでの一括バーンインを実現するため、基板上の全ての半導体装置の特定パッドを接続する試みがされている。特許文献2では、基板上にテストチップを設置し、これと半導体装置とを接続することで一括テストを可能とする試みがなされている。また、特許文献3では、1つの半導体装置に1つのテストパッドを設置することでテスト時間短縮の試みがされている。

【0005】

特許文献2に開示された技術を、図7〜図10を参照して、説明する。

【0006】

図7は、テストの対象であるウェハ710を示し、図8はその一部を拡大して示している。これらの図を参照して、ウェハ710上に、複数の被テストデバイスチップ711が設けられている。複数のデバイスチップ711はさらに複数ずつ組になっており、1組のデバイスチップ711に対し、1つのテスト専用チップ712が設けられている。そして、テスト専用チップ712とその組に属する複数のデバイスチップ711がテスト用バス713で結ばれている。各組のテスト専用チップ712には、複数のワイヤボンディングパッド714が設けられている。

【0007】

図9は、1つのテスト専用チップ712の概略構成を示し、図10は1つのデバイスチップ711の概略構成を示している。

【0008】

図9に示すように、テスト専用チップ712には、デコーダ915、テスト信号発生部916、マルチプレクサ917、n個(その組のデバイスチップ711の数)のドライバ918、期待値発生部919、判定部920およびラッチ回路921が設けられている。ドライバ918およびラッチ回路921は、バス713を介してデバイスチップ711に接続されている。

【0009】

図10に示すように、デバイスチップ711には、被テスト回路1022、テスト結果圧縮回路1023およびテストパターン・結果スキャン回路1024が設けられている。テストを行なう場合、1つの組のテスト専用チップ712にプロービングし、テスタを接続する。テスト専用チップ712に電源が印加され、デコーダ915にクロックS1、テストスタート信号S2、コマンドS3が印加されると、テスト専用チップ712はデバイスチップ711に対してテストモード信号S4を発する。テスト専用チップ712からテストモード信号S4が印加されると、デバイスチップ711はテスト専用チップ712に対してテストモードアクティブ信号S5を出力し、テストモードになる。

【0010】

このようにデバイスチップ711よりテストモードアクティブ信号S5が返ってくることにより、テスト専用チップ712とデバイスチップ711の通信が確かめられる。そして、テスト専用チップ712はテストモードアクティブ信号S5を受け、テストモード信号S4に対してテストモードアクティブ信号S5が返ってきたデバイスチップ711すなわちテスト可能デバイスチップ711の数をカウントし、テスト可能デバイスチップ711について次のようにテストを行なう。

【0011】

まず、デコーダ915はテスタより送られてくるコマンドS3のデコードを開始する。テスト信号発生部916はデコードされたコマンドに従いテスト信号を発生する。このテストパターンは、マルチプレクサ917およびドライバ918を介してテスト可能デバイスチップ711につながっているバス713に印加され、テスト信号S6としてテスト可能デバイスチップ711に送られる。デバイスチップ711では、テスト専用チップ712からのテスト信号S6がスキャン回路1024に印加され、スキャン回路1024は被テスト回路1022の各入力端子にテストパターンを分配し、テストが実行される。

【0012】

そのテスト信号S6に対する出力であるテスト結果は、再びスキャン回路1024に収集され、テスト結果信号S7としてテスト結果圧縮回路1023に送られる。テスト結果信号S7はテスト結果圧縮回路1023にて圧縮され、テスト結果圧縮信号S8がテスト専用チップ712に送られる。テスト専用チップ712においては、上記のようにテスト信号S6を出力すると同時に、期待値発生部919から期待値を発生し、デバイスチップ711からのテスト結果圧縮信号S8をラッチ回路921でラッチし、これが判定部920で期待値と比較判定される。テストの結果、不良デバイスチップ711がある場合、不良デバイスチップ711の座標が判定結果と同時に出力される。予めカウントされていたテスト可能デバイスチップ711全てのテストが終了すれば、テストエンド信号を出力して、その組のテストを終了する。そして、次の組のテスト専用デバイス712にプロービングし、同様にテストが行なわれる。

【0013】

【特許文献1】特開平5-55327号公報

【0014】

【特許文献2】特開平6-13445号公報

【0015】

【特許文献3】特開2001-85480号公報

【発明の開示】

【発明が解決しようとする課題】

【0016】

特許文献1で提案された手法においては、基板上の全ての半導体装置に接続されるため、バーンインなどの電圧供給には支障が無いが、微小リークなどの評価を実施する際には基板上の、少数ではあるが必ず存在する、不良品から生じる大電流により、適正な評価が困難となる。

【0017】

この問題を解消すべく、特許文献2においては、図7に示すように、テスト専用チップ712とその組に入る複数のデバイスチップ711がテスト用バス713で結ばれているが、このバス713は同一配線層で形成されている。そのために、1つのテスト専用チップ712で接続するデバイスチップ711の数が増えると、テスト用バス713の本数が増加し、スクライブライン内に設置すべき配線の数が増え、ひいてはスクライブライン幅の増大を招き、結果として基板から得られる半導体装置の数の減少を招く結果となる。

【0018】

たとえばテスト用バス713を20個の半導体装置に接続する場合、スクライブライン内に設けられる配線の幅を2um、配線間スペースを1umとした場合、スクライブライン内に形成される配線/配線間スペース領域の幅は59umとなる。これは半導体装置を個片化することを考えた場合、ダイシング時にメタル材料を完全に除去したうえで、ダイシングによるチッピングを半導体装置内に影響しないようにするためには、約110um幅のスクライブラインの形成を必要とする。20個以上の半導体装置を一括して1つのテスト専用チップに接続しようとした場合には、スクライブライ内の配線数が増加し、スクライブライン幅を110um幅より広くすることが必要になり、結果として基板上に形成できる半導体装置の数が減少してしまう。また、テスト専用チップ712内は複雑な回路が形成されるため面積が必要となる。したがって、トランジスタ単体の評価が行えるよう従来からある専用チップを同時に形成した場合、テストチップの面積は増大し、基板上に形成される半導体装置の数は減少する。

【0019】

同様に特許文献3で提案された手法では、基板上に形成される半導体装置の数が増えることで、テストチップの数の増大を招き、半導体装置の数は減少する結果となっている。

【0020】

さらに、いずれの提案においても、配線材料に関しての記載が無い。しかし、大型TFT液晶モニター用ドライバなどにおいては、基板上に形成された半導体装置をダイシングにより個片化した後、テープへ実装する場合がある。そのようなとき、スクライブライン内にメタル材料が存在する場合は、メタル材料が存在する領域を全て取り除き、個片化された半導体装置の端部にメタル材料を残さないようにしている。これは半導体装置の端部にメタル材質が存在すると、ダイシングによりメタル材質が露出し、テープへの実装時にテープに形成された配線を短絡させることがあり、ひいては半導体装置の信頼性を著しく低下させるからである。このためスクライブライン内に存在するメタル材料は、スクライブラインの中心から30um以内の領域に形成するのが一般的である。

【0021】

テスト専用チップと半導体装置を接続する場合、スクライブラインから半導体装置内へ接続するための配線が必ず存在し、この配線材料にメタル材料を用いると、半導体装置の個片化のためのダイシングを実施した場合、必ずメタル材料を切断する領域が発生する。しかし、メタル材料は材質特性的に安定した切断面を形成できず、その一部が半導体装置の端部に露出し、信頼性を著しく低下させることになる。

【0022】

この発明は上記のような問題点を解決するためになされたもので、半導体装置のテスト時間の短縮を、基板上に形成される半導体装置の数を減少させることなく実現することができるように改良された大規模集積回路のウェハを提供することを目的とする。

【0023】

この発明の他の目的は、基板上に形成される半導体装置の数が1000ヶを超えるような場合においても、スクライブライン幅を増大することなく、すなわち基板上に形成される半導体装置の数を減少させることなく、個々の半導体装置のテスト評価を大幅に簡略化することができるように改良された大規模集積回路のウェハを提供することを目的とする。

【0024】

本発明のさらに他の目的は、テープへの実装後もその信頼性を損なわないように改良された大規模集積回路のウェハを提供することにある。

【0025】

この発明の他の目的は、そのような大規模集積回路のウェハの製造方法を提供することにある。

【課題を解決するための手段】

【0026】

この発明に従う大規模集積回路のウェハは、半導体基板の上に設けられ、半導体装置のテストを行うための、パッド電極を含むテストチップと、上記半導体基板の上に、上記テストチップを間に挟んで、第1のスクライブラインが延びる方向に、複数個の半導体装置が並んでなる半導体装置の列とを備える。上記半導体装置の列は、上記第1のスクライブラインと直交する第2のスクライブラインが延びる方向に複数並んで設けられている。上記第2のスクライブライン内に、各半導体装置と対になるように、該半導体装置と上記テストチップを中継する中継回路が設けられている。上記半導体装置は、該半導体装置の最も基板側に形成された第1層配線を有する。上記中継回路と上記半導体装置は、ポリシリコン配線で接続されている。上記中継回路にその一方端が接続された第2層配線が、上記第2スクライブライン内に延びている。上記テストチップ内に形成された上記パッド電極にその一方端が接続された第3層配線が、上記第1のスクライブライン内に延びている。上記第2層配線と上記第3層配線は、その間に設けられた絶縁膜を介して上下に隔てて形成されており、かつ該絶縁膜中に設けられたビアホールを介して電気的に接続されている。

【0027】

このように構成することにより、1つのテストチップに接続すべき半導体装置の数が増大しても、スクライブライン内の配線数は増大しない。

【0028】

この発明の好ましい実施態様によれば、上記ビアホールの形成位置は上記第1スクライブラインと上記第2スクライブラインが直交する領域である。

【0029】

上記第2層配線及び第3層配線の配線幅は、それぞれ1〜2μmであるのが好ましい。

【0030】

上記第2層配線及び第3層配線は、それぞれ複数本形成されており、配線の間隔は1〜2μmであるのが好ましい。

【0031】

上記第2層配線及び第3層配線は、それぞれ6本以上形成されているのが好ましい。

【0032】

上記ポリシリコン配線はトランジスタのゲート電極の構成と同一であるのが好ましい。

【0033】

上記テストチップ1つに対し、接続する上記半導体装置の数が20以上であることが好ましい。

【0034】

上記テストチップ内に設けられた上記テストパッド電極は2列に配置されるのが好ましい。このように構成することにより、テスト工程において、上記テストパッド電極にテスト針を接触させることで、上記テストパッドの左右に形成された上記半導体装置を一度に一括して短時間でテストすることが可能になる。

【0035】

この発明の他の局面に従う大規模集積回路のウェハの製造方法は、半導体基板の上に、テストチップを間に挟んで、第1のスクライブラインが延びる方向に、第1層配線を有する半導体装置が複数個並んでなる半導体装置の列を、前記第1のスクライブラインと直交する第2のスクライブラインが延びる方向に複数並べて設ける工程と、前記第2のスクライブライン内に、前記半導体装置と前記テストチップを中継する中継回路を設ける工程と、前記中継回路と前記半導体装置を、ポリシリコン配線で接続する工程と、前記中継回路にその一方端が接続され、かつ前記第2スクライブライン内に延びるように第2層配線を形成する工程と、前記第2層配線を覆うように前記半導体基板の上に絶縁層を形成する工程と、前記絶縁層中に、前記第2層配線に至るビアホールを形成する工程と、前記テストチップ内に形成されたパッド電極にその一方端が接続されるように、かつ前記ビアホールに接触させながら前記第1のスクライブライン内に延びるように、上記絶縁層の上に第3層配線を形成する工程とを備える。

【0036】

上記ビアホールの形成位置を、上記第1スクライブラインと前記第2スクライブラインが直交する領域に選ぶのが好ましい。

【発明の効果】

【0037】

テストチップ内に設置されたテスト専用チップのパッド電極を介して、各ブロック内で接続された半導体装置の全てを一括テストすることが可能となり、基板上に製造された半導体装置の評価を大幅に簡素化できた。この評価は、スクライブラインの幅を増大することなく、すなわち、基板上に設置可能な半導体装置の数を減少させることなく実現できた。

【0038】

より具体的には、テストチップ内に設置された専用チップ(半導体装置を構成する単体のトランジスタ等の特性を評価するチップ)の評価をするときに合わせて、今回設置したテスト専用チップの評価を行うことができ、従来実施していた、各半導体装置の個別の評価をする工程を削除することができた。

【0039】

さらに各半導体装置を基板上から個片化し、テープへの実装をする際にも、ポリシリコン材料を用いることで、テープ側の配線を短絡させることなく、実装することができ、デバイスの信頼性を確保することができた。

【発明を実施するための最良の形態】

【0040】

この発明は、一つのテスト専用チップに複数の半導体装置を電気的に接続してなるブロックを、基板上に複数個形成する手段を提供する。これにより、基板上に形成される半導体装置の数が1000ヶを超えるような場合においても、スクライブラインの幅を増大することなく、すなわち基板上に形成される半導体装置の数を減少させることなく、個々の半導体装置のテスト評価を行え、評価作業が大幅に簡略化する。

【0041】

本発明においては、まず基板上に半導体装置とテストチップ(テスト専用チップを含む)を形成する。垂直方向に延びる第2スクライブライン内であって、上記半導体装置の直近に、該半導体装置と対になるように、上記テストチップと上記半導体装置を中継する中継回路を設ける。中継回路と半導体装置はポリシリコン配線で接続する。

【0042】

第2スクライブラインに沿って、上記各半導体装置の直近までメタル配線(最上層−1層目メタル配線)を形成した後、この最上層−1層目メタル配線を、上記中継回路へ接続することで終端させる。次に、後に形成される最上層メタル配線と上記最上層−1層目メタル配線とを接続するビアーホールを形成する。これらの工程は、ステッパ露光装置の1ショット内であって、垂直方向に形成される第2スクライブライン内に、ビアホール及び最上層−1層目メタル配線を形成することで実現できる。

【0043】

次に、テストチップ内に形成されたパッド(最上層メタルで形成される)にその一方端が接続された最上層メタル配線を、上記ビアホールに接続させながら、水平方向に形成された第1スクライブライン内に延びるように形成する。これは、ステッパ露光装置の1ショット内にて、2段に形成された半導体装置の間に水平方向に形成される第1スクライブライン内に、配線を形成することで実現可能である。

【0044】

また、テストチップ内に設置するパッド(評価時にテスト針を接触させるもの)は2列に形成する。左側の列のパッドに、テストチップの左側に設置された各半導体装置を1つのブロックとして、これに電流を送り込むように配線を形成する。右側の列のパッドに、テストチップの右側に設置された各半導体装置を同様に1つのブロックとして、これに電流を送り込むように配線を形成する。これにより、1つのテストチップの設置により、電気的に分離された2つのブロックが接続されることとなる。テストチップを基板上にn個設置することで、電気的に分離されたブロックを2n個形成できることとなる。

【0045】

そして、1つのテストチップに接続すべき半導体装置の数が増大しても、スクライブライン内の配線数は増大しない。そのため、1テストチップ(基板上で電気的に独立して複数個形成される)と複数(少なくとも20以上)の半導体装置の接続を、スクライブライン幅の増大を招くことなく実現できる。その結果、スクライブライン幅の増大を招くことなく、各テストチップを介して電気的に接続された、複数個の半導体装置を一括して評価することが可能となる。

【0046】

なお、テストチップ内に、半導体装置内で構成される各個別能動素子、受動素子単体および、それらを組み合わせて構成される基本回路の電気的特性を評価するための各回路および各パッドを形成することで、半導体装置の一括評価と同時に、これらの評価も可能となり、さらに半導体装置の評価時間の短縮が可能となる。

【0047】

さらに、上記中継回路から各半導体装置内に設置されたパッドへの電気的接続を実現する配線に、メタル配線層より下層にて形成されるポリシリコン材料による配線を用いることで、ダイシング完了時点での個片化された半導体装置の端面にメタル材料が露出することはなくなる。ひいては、メタル材料を介して、テープ側に形成された配線が短絡するという不具合は発生しなくなる。

【0048】

以下この発明の実施例を図面を用いて説明する。

【実施例1】

【0049】

本実施例では、メタル配線層を3層、ポリシリコン配線を1層で形成する大規模集積回路のウェハに適用した場合について説明する。

【0050】

本明細書において、第3層メタル配線とは半導体装置のもっとも表面側に形成される配線をいう。第2層メタル配線とは、第3層メタル配線より1層下に形成される配線をいう。第1層メタル配線とは半導体装置の中でもっとも基板側に形成されるメタル配線をいう。ポリシリコン配線は第1層メタル配線よりさらに下層に形成される。

【0051】

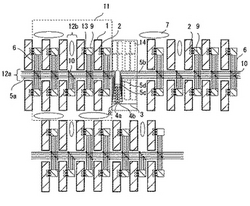

図1は、基板上に複数の半導体装置およびスクライブラインを作りこむための、ステッパ露光装置の1ショットの各層の重ね合わせ(マスクセット)を示す概念図である。

【0052】

図1を参照して、1ショット内には、水平方向に形成された第1のスクライブライン12aが延びる方向に、4個の半導体装置1が並んでなる半導体装置1の列が形成される。半導体装置1の列は、第2のスクライブライン12b(第1のスクライブライン12aと直交する)が延びる方向に、2段に並んで設けられる。図1では、8つの半導体装置を一括して露光する場合を図示しているが、この数に制限されるものではない。

【0053】

図1に示すように、テストチップ3の中に、テスト専用チップ8が設置される。テスト専用チップ8には、第3層配線材にて形成されたパッド電極4が12ヶ(6ヶ×2列)設置される。第3層配線5cは、各々のパッド電極4に接続される。テストチップ3内には、テスト専用チップ8以外に、半導体装置内で使用されるトランジスタのスレッシュ電圧等を測定するための特性テストチップ14が10ヶ設置される。

【0054】

図1に示すように、半導体装置の上下の列の間に形成された水平方向に延びる第1スクライブライン12a内に、第3層メタル配線5が形成される。本実施例では2um幅の第3層メタル配線3本と1um幅の第3層メタル配線3本を配線間スペース1umで形成することで、第1スクライブライン12a内のメタル材料の存在する領域は14um幅にすることができた。本実施例では水平方向に延びる第1スクライブラン12aの幅としては110umを採用した。この配線本数、配線幅、配線間スペースには制限を加えるものではない。

【0055】

図1に示すように、第1スクライブライン12aと第2スクライブライン12bとの交差領域にビアホール10が形成される。ビアホール10によって、第1スクライブライン12a内に形成された第3層メタル配線5と、第2スクライブライン12b内に形成された第2層メタル配線6が接続される。本実施例では2um幅の第2層メタル配線3本と1um幅の第2層メタル配線3本を配線間スペース1umで形成したことで、第2スクライブライン12b内のメタル材料の存在する領域は14um幅にすることができた。本実施例では垂直方向のスクライブラン12b幅としては110umを採用した。この配線本数、配線幅、配線間スペースには制限を加えるものではない。

【0056】

図1に示すように、第2層メタル配線6は、第2スクライブライン12b内に形成された中継回路9に接続されており、この中継回路9内で3つのポリシリコン配線13(半導体装置内の第1層メタル配線よりも下層に形成されている)に接続され、この3つのポリシリコン配線13は各半導体装置の3つの特定パッド2に接続されている。図1では、各半導体装置の特定電極として3つの特定パッド2を示しているが、その数に制限されるものではない。

【0057】

図1に示すようなスクライブライン内に多層配線を形成するにあたり、半導体装置の製造工程と全く同一の工程フローでこれを実現するために、スクライブライン内の配線は、半導体装置を形成するために用いた多層メタル配線材を用いて形成される。

【0058】

なお、図1に示すように、ステッパ用のマーク類7(露光時に下地との位置合わせをするためのもの)が、1ショットの領域11内に設置されており、この部分には配線を設置しない。

【0059】

次に図2から図5を参照して、上記の露光用マスクセットを用いて、基板上に半導体装置およびテストチップを形成する工程を説明する。半導体装置1内には第1層メタル配線を用いてパターンが形成されるが、図示しない。

【0060】

図2は、第1層メタル配線(図示しない)を形成した後の、基板上のパターンの概念図を示す。

図2に示すように、基板の上に、まず、半導体装置1と、一つのテスト専用チップ8と10ケのトランジスタ等特性テストチップ14を含むテストチップ3を形成する。垂直方向に延びる第2スクライブライン12b内であって、半導体装置1の直近に、該半導体装置1と対になるように、テストチップ3と半導体装置1を中継するための中継回路9を設ける。第2スクライブライン12b内において、中継回路9と半導体装置1とをポリシリコン配線13で接続した。これにより基板上の各半導体装置1の個片化を目的としたダイシングを実施したとき、ダイシングラインをまたぐのはポリシリコン配線のみとすることができる。

【0061】

本実施例においては、中継回路9を、後述する第2層メタル配線(テストチップ3内に形成されたテスト専用チップ8から延び、第2スクライブライン12b内を通って形成されるもの)と半導体装置1の特定電極との電気的接続をon/offさせる、スイッチング回路で形成した。しかし、中継回路9は、このような回路に制限されるものではない。この後、第1層メタル配線層(図示せず)まで形成することで、中継回路9が完成する。なお、図中、下の2列の半導体装置の列は、基板内の平坦性を確保するためのダミーである。

【0062】

図3は、第1層メタル配線(図示せず)と第2層メタル配線6をつなぐビアホール(図示せず)を形成後に、第2層メタル配線6まで形成した工程における、基板上のパターンの概念図を示す。図3に示すように、第2スクライブライン12b内に形成された第2層メタル配線6は、各半導体装置1の直近に形成された中継回路9に接続されている。第2層メタル配線6は、中継回路9へ接続することで終端させている。図示しないが、第2層メタル配線6を覆うように絶縁膜が形成される。

【0063】

図4は、第2層メタル配線6と第3層メタル配線(図示せず)を接続するためのビアホール10を上記絶縁膜中に形成した後の、基板上のパターンの概念図を示す。図4に示すように、ビアホール10は、第1スクライブライン12aと第2スクライブライン12bが直交する領域内に形成される。

【0064】

図5は、第3層メタル配線5aまで形成した工程における、基板上のパターンの概念図を示す。図5に示すように、テスト専用チップ8内のパッド電極4aから延びる第3層メタル配線5c(6本)が、水平方向に延びる第1スクライブライン12a内の第3層メタル配線5a(6本)と基板上で接続されることになる。

【0065】

さらに、第3層メタル配線5a(6本)は、対応するビアホール10および第2層メタル配線6(6本)を経由し、各半導体装置1の直近に設けられた中継回路9に平行して接続されることになる。さらに、中継回路9からポリシリコン配線13を用いて半導体装置1の特定パッド2へ接続されることになる。

【0066】

また同様に図5で示すようにテストチップ3内に設置されたテスト専用チップ8中の右列側に設置されたの6つの電極4bから第3層メタル配線5d(6本)が延び、そしてこの第3層メタル配線5d(6本)は、基板上で対応する第3層メタル配線5b(6本)に接続され、さらに、対応するビアホール10および第2層メタル配線6(6本)を経由し、各半導体装置1の直近に設けられた中継回路9に平行して接続される。さらに、中継回路9からポリシリコン配線13を用いて半導体装置の特定パッド2へ接続されることになる。

【0067】

この際、図5に示すように、第3層メタル配線5aは、第1スクライブライン12a内を横方向に延びていき、ビアーホール10を介して、横方向に並んで形成される第2層メタル配線6のそれぞれに順次接続されていき、最後に基板の最外周に設けられた半導体装置1にまで接続されることになる。よって、テストチップ3の左側に形成された全ての半導体装置1は、テスト専用チップ8内の6つの電極4aに電気的に接続されることになる。同様にテストチップの右側でも全ての半導体装置1は、6つの電極4bに電気的に接続されることになる。

【0068】

結果的に図5に示すようにテストチップ3の左右に、2つの、電気的に独立に接続されたブロックが形成された。

【0069】

本実施例では、図6に示すように、基板60上に、テスト専用チップを含むテストチップ62を3つ形成し、6つの電気的に独立に接続されたブロック61を形成した。本実施例では、1つのテストチップ3内に形成されたテスト専用チップ8の左側のパッド電極4aを、最大56ヶの半導体装置の特定パッド2に接続した。この場合でも本手法を用いることで、スクライブライン内の配線数は6本のみで形成されるので、スクライブライン幅を大きくする必要がない。

【0070】

テスト工程においては、テストチップ3内に形成されたテスト専用チップ8の左側のパッド電極4aおよび右側のパッド電極4bに対してテスト針を接触させることで、テストチップ3の左右に形成された半導体装置を一度に一括してテストすることが可能となり、基板の歩留まりを容易に短時間で評価することが可能となった。

【0071】

半導体装置を基板60から個片化するダイシング工程においても、スクライブライン内に形成されたメタル配線の存在領域は第1、第2スクライブライン12a,12b共に,スクライブラインの中心から7umまでの領域に抑えられており、かつ、第2スクライブライン12bから半導体装置1内へ接続するための配線はメタル材料ではなく、ポリシリコン材料であるので、半導体装置1の個片化のためのダイシングを実施した場合、ポリシリコン材料は安定した断面形状を形成するので、半導体装置1の端にまで露出することはない。また、メタル材料は存在しないのでメタル材料の露出もなく、テープへの実装時にテープに形成された配線を短絡させることのない半導体装置が得られ、半導体装置の高い信頼性が確保される。

【0072】

今回開示された実施例はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【産業上の利用可能性】

【0073】

本発明は、特に大型TFT液晶モニター用ドライバなど、基板上に形成された半導体装置をダイシングにより個片化した後、テープへ実装する場合に有効である。

【図面の簡単な説明】

【0074】

【図1】本発明の実施例にかかる、基板上に複数の半導体装置およびスクライブラインを作りこむための、ステッパ露光装置の1ショットの各層の重ね合わせ(マスクセット)を示す概念図(基板上に形成された半導体装置、スクライブライン、およびテストチップの概念図)である。

【図2】第1層配線形成工程後の、基板上に形成された半導体装置、スクライブライン、およびテストチップの概念図を示す。

【図3】第1層配線と第2層配線をつなぐビアホールを形成後に第2配線層まで形成した工程における、基板上に形成された半導体装置、スクライブライン、およびテストチップの概念図を示す。

【図4】第2配線層と第3配線層を接続するためのビアホールを形成した工程における、基板上に形成された半導体装置、スクライブライン、およびテストチップの概念図を示す。

【図5】第3配線層まで形成した工程における、基板上に形成された半導体装置、スクライブライン、およびテストチップの概念図を示す。

【図6】本実施例にかかる、基板上に形成された、テストチップと、6つの電気的に独立に接続されたブロック(半導体装置の集合体)を示す図である。

【図7】従来の規模集積回路のウェハーの平面図である。

【図8】図7のウェハーの一部を拡大して示す平面図である。

【図9】従来のテスト専用チップのブロック図である。

【図10】従来の被テストデバイスのブロック図である。

【符号の説明】

【0075】

1 半導体装置

2 パッド電極

3 テストチップ

4 第3層配線材にて形成されたパッド電極

4a 第3層配線材にて形成された左列側のパッド電極

4b 第3層配線材にて形成された右列側のパッド電極

5 第3層メタル配線

5a テストチップより左側に形成された第3層メタル配線

5b テストチップより右側に形成された第3層メタル配線

5c テストチップ内に形成された第3層メタル配線

5d テストチップ内に形成された第3層メタル配線

6 第2層メタル配線

7 ステッパ用マーク類

8 テスト専用チップ

9 スクライブライン内に設置した中継回路

10 ビアホール

11 ステッパによる1ショットの領域

12a 水平方向に延びる第1のスクライブライン

12b 垂直方向に延びる第2のスクライブライン

13 ポリシリコン配線

14 テストチップ内のトランジスタ等特性テストチップ

61 半導体装置の集合体

62 テストチップ

【技術分野】

【0001】

本発明は一般に大規模集積回路のウェハに関し、より特定的には、スクライブライン幅を増加することなく、半導体装置を容易に短時間で評価することができるように改良された大規模集積回路のウェハに関する。この発明はまたそのような大規模集積回路のウェハの製造方法に関する。より具体的には、半導体装置の製造工程におけるスクライブライン内の配線層の形成技術と、複数の半導体装置の特定電極を電気的に繋ぎ一括テストする評価技術とに関し、さらに具体的には、基板上に設けられる複数の半導体装置をいくつかの電気的に独立したブロックに分割し、各々のブロック毎に、テスト専用チップを繋ぐ配線層の形成技術に関する。

【背景技術】

【0002】

半導体装置のサイズは、微細化の進展とともに縮小し、一方半導体装置を製造する基板は大口径化し、結果として基板1枚当たりに製造される半導体装置の数は増加する傾向にあり、1000ヶ以上ある場合も珍しくは無い。また、製造方法の完成度は向上し、基板1枚当たりの良品半導体装置の比率(歩留まり)は90%を超えている。しかし、このような状況下でも、半導体装置の評価は、基板上に製造された全ての半導体装置に対して実施している。従って、半導体装置の評価時間が多大なものとなり、TAT、評価設備の保有台数に負荷を与えている。さらに、基板からダイシングによって個片化された半導体装置は、テープなどに実装された後、再び評価されている。

【0003】

このような状況下、半導体装置の評価方法について、いくつかの提案がなされている。

【0004】

特許文献1においては、基板レベルでの一括バーンインを実現するため、基板上の全ての半導体装置の特定パッドを接続する試みがされている。特許文献2では、基板上にテストチップを設置し、これと半導体装置とを接続することで一括テストを可能とする試みがなされている。また、特許文献3では、1つの半導体装置に1つのテストパッドを設置することでテスト時間短縮の試みがされている。

【0005】

特許文献2に開示された技術を、図7〜図10を参照して、説明する。

【0006】

図7は、テストの対象であるウェハ710を示し、図8はその一部を拡大して示している。これらの図を参照して、ウェハ710上に、複数の被テストデバイスチップ711が設けられている。複数のデバイスチップ711はさらに複数ずつ組になっており、1組のデバイスチップ711に対し、1つのテスト専用チップ712が設けられている。そして、テスト専用チップ712とその組に属する複数のデバイスチップ711がテスト用バス713で結ばれている。各組のテスト専用チップ712には、複数のワイヤボンディングパッド714が設けられている。

【0007】

図9は、1つのテスト専用チップ712の概略構成を示し、図10は1つのデバイスチップ711の概略構成を示している。

【0008】

図9に示すように、テスト専用チップ712には、デコーダ915、テスト信号発生部916、マルチプレクサ917、n個(その組のデバイスチップ711の数)のドライバ918、期待値発生部919、判定部920およびラッチ回路921が設けられている。ドライバ918およびラッチ回路921は、バス713を介してデバイスチップ711に接続されている。

【0009】

図10に示すように、デバイスチップ711には、被テスト回路1022、テスト結果圧縮回路1023およびテストパターン・結果スキャン回路1024が設けられている。テストを行なう場合、1つの組のテスト専用チップ712にプロービングし、テスタを接続する。テスト専用チップ712に電源が印加され、デコーダ915にクロックS1、テストスタート信号S2、コマンドS3が印加されると、テスト専用チップ712はデバイスチップ711に対してテストモード信号S4を発する。テスト専用チップ712からテストモード信号S4が印加されると、デバイスチップ711はテスト専用チップ712に対してテストモードアクティブ信号S5を出力し、テストモードになる。

【0010】

このようにデバイスチップ711よりテストモードアクティブ信号S5が返ってくることにより、テスト専用チップ712とデバイスチップ711の通信が確かめられる。そして、テスト専用チップ712はテストモードアクティブ信号S5を受け、テストモード信号S4に対してテストモードアクティブ信号S5が返ってきたデバイスチップ711すなわちテスト可能デバイスチップ711の数をカウントし、テスト可能デバイスチップ711について次のようにテストを行なう。

【0011】

まず、デコーダ915はテスタより送られてくるコマンドS3のデコードを開始する。テスト信号発生部916はデコードされたコマンドに従いテスト信号を発生する。このテストパターンは、マルチプレクサ917およびドライバ918を介してテスト可能デバイスチップ711につながっているバス713に印加され、テスト信号S6としてテスト可能デバイスチップ711に送られる。デバイスチップ711では、テスト専用チップ712からのテスト信号S6がスキャン回路1024に印加され、スキャン回路1024は被テスト回路1022の各入力端子にテストパターンを分配し、テストが実行される。

【0012】

そのテスト信号S6に対する出力であるテスト結果は、再びスキャン回路1024に収集され、テスト結果信号S7としてテスト結果圧縮回路1023に送られる。テスト結果信号S7はテスト結果圧縮回路1023にて圧縮され、テスト結果圧縮信号S8がテスト専用チップ712に送られる。テスト専用チップ712においては、上記のようにテスト信号S6を出力すると同時に、期待値発生部919から期待値を発生し、デバイスチップ711からのテスト結果圧縮信号S8をラッチ回路921でラッチし、これが判定部920で期待値と比較判定される。テストの結果、不良デバイスチップ711がある場合、不良デバイスチップ711の座標が判定結果と同時に出力される。予めカウントされていたテスト可能デバイスチップ711全てのテストが終了すれば、テストエンド信号を出力して、その組のテストを終了する。そして、次の組のテスト専用デバイス712にプロービングし、同様にテストが行なわれる。

【0013】

【特許文献1】特開平5-55327号公報

【0014】

【特許文献2】特開平6-13445号公報

【0015】

【特許文献3】特開2001-85480号公報

【発明の開示】

【発明が解決しようとする課題】

【0016】

特許文献1で提案された手法においては、基板上の全ての半導体装置に接続されるため、バーンインなどの電圧供給には支障が無いが、微小リークなどの評価を実施する際には基板上の、少数ではあるが必ず存在する、不良品から生じる大電流により、適正な評価が困難となる。

【0017】

この問題を解消すべく、特許文献2においては、図7に示すように、テスト専用チップ712とその組に入る複数のデバイスチップ711がテスト用バス713で結ばれているが、このバス713は同一配線層で形成されている。そのために、1つのテスト専用チップ712で接続するデバイスチップ711の数が増えると、テスト用バス713の本数が増加し、スクライブライン内に設置すべき配線の数が増え、ひいてはスクライブライン幅の増大を招き、結果として基板から得られる半導体装置の数の減少を招く結果となる。

【0018】

たとえばテスト用バス713を20個の半導体装置に接続する場合、スクライブライン内に設けられる配線の幅を2um、配線間スペースを1umとした場合、スクライブライン内に形成される配線/配線間スペース領域の幅は59umとなる。これは半導体装置を個片化することを考えた場合、ダイシング時にメタル材料を完全に除去したうえで、ダイシングによるチッピングを半導体装置内に影響しないようにするためには、約110um幅のスクライブラインの形成を必要とする。20個以上の半導体装置を一括して1つのテスト専用チップに接続しようとした場合には、スクライブライ内の配線数が増加し、スクライブライン幅を110um幅より広くすることが必要になり、結果として基板上に形成できる半導体装置の数が減少してしまう。また、テスト専用チップ712内は複雑な回路が形成されるため面積が必要となる。したがって、トランジスタ単体の評価が行えるよう従来からある専用チップを同時に形成した場合、テストチップの面積は増大し、基板上に形成される半導体装置の数は減少する。

【0019】

同様に特許文献3で提案された手法では、基板上に形成される半導体装置の数が増えることで、テストチップの数の増大を招き、半導体装置の数は減少する結果となっている。

【0020】

さらに、いずれの提案においても、配線材料に関しての記載が無い。しかし、大型TFT液晶モニター用ドライバなどにおいては、基板上に形成された半導体装置をダイシングにより個片化した後、テープへ実装する場合がある。そのようなとき、スクライブライン内にメタル材料が存在する場合は、メタル材料が存在する領域を全て取り除き、個片化された半導体装置の端部にメタル材料を残さないようにしている。これは半導体装置の端部にメタル材質が存在すると、ダイシングによりメタル材質が露出し、テープへの実装時にテープに形成された配線を短絡させることがあり、ひいては半導体装置の信頼性を著しく低下させるからである。このためスクライブライン内に存在するメタル材料は、スクライブラインの中心から30um以内の領域に形成するのが一般的である。

【0021】

テスト専用チップと半導体装置を接続する場合、スクライブラインから半導体装置内へ接続するための配線が必ず存在し、この配線材料にメタル材料を用いると、半導体装置の個片化のためのダイシングを実施した場合、必ずメタル材料を切断する領域が発生する。しかし、メタル材料は材質特性的に安定した切断面を形成できず、その一部が半導体装置の端部に露出し、信頼性を著しく低下させることになる。

【0022】

この発明は上記のような問題点を解決するためになされたもので、半導体装置のテスト時間の短縮を、基板上に形成される半導体装置の数を減少させることなく実現することができるように改良された大規模集積回路のウェハを提供することを目的とする。

【0023】

この発明の他の目的は、基板上に形成される半導体装置の数が1000ヶを超えるような場合においても、スクライブライン幅を増大することなく、すなわち基板上に形成される半導体装置の数を減少させることなく、個々の半導体装置のテスト評価を大幅に簡略化することができるように改良された大規模集積回路のウェハを提供することを目的とする。

【0024】

本発明のさらに他の目的は、テープへの実装後もその信頼性を損なわないように改良された大規模集積回路のウェハを提供することにある。

【0025】

この発明の他の目的は、そのような大規模集積回路のウェハの製造方法を提供することにある。

【課題を解決するための手段】

【0026】

この発明に従う大規模集積回路のウェハは、半導体基板の上に設けられ、半導体装置のテストを行うための、パッド電極を含むテストチップと、上記半導体基板の上に、上記テストチップを間に挟んで、第1のスクライブラインが延びる方向に、複数個の半導体装置が並んでなる半導体装置の列とを備える。上記半導体装置の列は、上記第1のスクライブラインと直交する第2のスクライブラインが延びる方向に複数並んで設けられている。上記第2のスクライブライン内に、各半導体装置と対になるように、該半導体装置と上記テストチップを中継する中継回路が設けられている。上記半導体装置は、該半導体装置の最も基板側に形成された第1層配線を有する。上記中継回路と上記半導体装置は、ポリシリコン配線で接続されている。上記中継回路にその一方端が接続された第2層配線が、上記第2スクライブライン内に延びている。上記テストチップ内に形成された上記パッド電極にその一方端が接続された第3層配線が、上記第1のスクライブライン内に延びている。上記第2層配線と上記第3層配線は、その間に設けられた絶縁膜を介して上下に隔てて形成されており、かつ該絶縁膜中に設けられたビアホールを介して電気的に接続されている。

【0027】

このように構成することにより、1つのテストチップに接続すべき半導体装置の数が増大しても、スクライブライン内の配線数は増大しない。

【0028】

この発明の好ましい実施態様によれば、上記ビアホールの形成位置は上記第1スクライブラインと上記第2スクライブラインが直交する領域である。

【0029】

上記第2層配線及び第3層配線の配線幅は、それぞれ1〜2μmであるのが好ましい。

【0030】

上記第2層配線及び第3層配線は、それぞれ複数本形成されており、配線の間隔は1〜2μmであるのが好ましい。

【0031】

上記第2層配線及び第3層配線は、それぞれ6本以上形成されているのが好ましい。

【0032】

上記ポリシリコン配線はトランジスタのゲート電極の構成と同一であるのが好ましい。

【0033】

上記テストチップ1つに対し、接続する上記半導体装置の数が20以上であることが好ましい。

【0034】

上記テストチップ内に設けられた上記テストパッド電極は2列に配置されるのが好ましい。このように構成することにより、テスト工程において、上記テストパッド電極にテスト針を接触させることで、上記テストパッドの左右に形成された上記半導体装置を一度に一括して短時間でテストすることが可能になる。

【0035】

この発明の他の局面に従う大規模集積回路のウェハの製造方法は、半導体基板の上に、テストチップを間に挟んで、第1のスクライブラインが延びる方向に、第1層配線を有する半導体装置が複数個並んでなる半導体装置の列を、前記第1のスクライブラインと直交する第2のスクライブラインが延びる方向に複数並べて設ける工程と、前記第2のスクライブライン内に、前記半導体装置と前記テストチップを中継する中継回路を設ける工程と、前記中継回路と前記半導体装置を、ポリシリコン配線で接続する工程と、前記中継回路にその一方端が接続され、かつ前記第2スクライブライン内に延びるように第2層配線を形成する工程と、前記第2層配線を覆うように前記半導体基板の上に絶縁層を形成する工程と、前記絶縁層中に、前記第2層配線に至るビアホールを形成する工程と、前記テストチップ内に形成されたパッド電極にその一方端が接続されるように、かつ前記ビアホールに接触させながら前記第1のスクライブライン内に延びるように、上記絶縁層の上に第3層配線を形成する工程とを備える。

【0036】

上記ビアホールの形成位置を、上記第1スクライブラインと前記第2スクライブラインが直交する領域に選ぶのが好ましい。

【発明の効果】

【0037】

テストチップ内に設置されたテスト専用チップのパッド電極を介して、各ブロック内で接続された半導体装置の全てを一括テストすることが可能となり、基板上に製造された半導体装置の評価を大幅に簡素化できた。この評価は、スクライブラインの幅を増大することなく、すなわち、基板上に設置可能な半導体装置の数を減少させることなく実現できた。

【0038】

より具体的には、テストチップ内に設置された専用チップ(半導体装置を構成する単体のトランジスタ等の特性を評価するチップ)の評価をするときに合わせて、今回設置したテスト専用チップの評価を行うことができ、従来実施していた、各半導体装置の個別の評価をする工程を削除することができた。

【0039】

さらに各半導体装置を基板上から個片化し、テープへの実装をする際にも、ポリシリコン材料を用いることで、テープ側の配線を短絡させることなく、実装することができ、デバイスの信頼性を確保することができた。

【発明を実施するための最良の形態】

【0040】

この発明は、一つのテスト専用チップに複数の半導体装置を電気的に接続してなるブロックを、基板上に複数個形成する手段を提供する。これにより、基板上に形成される半導体装置の数が1000ヶを超えるような場合においても、スクライブラインの幅を増大することなく、すなわち基板上に形成される半導体装置の数を減少させることなく、個々の半導体装置のテスト評価を行え、評価作業が大幅に簡略化する。

【0041】

本発明においては、まず基板上に半導体装置とテストチップ(テスト専用チップを含む)を形成する。垂直方向に延びる第2スクライブライン内であって、上記半導体装置の直近に、該半導体装置と対になるように、上記テストチップと上記半導体装置を中継する中継回路を設ける。中継回路と半導体装置はポリシリコン配線で接続する。

【0042】

第2スクライブラインに沿って、上記各半導体装置の直近までメタル配線(最上層−1層目メタル配線)を形成した後、この最上層−1層目メタル配線を、上記中継回路へ接続することで終端させる。次に、後に形成される最上層メタル配線と上記最上層−1層目メタル配線とを接続するビアーホールを形成する。これらの工程は、ステッパ露光装置の1ショット内であって、垂直方向に形成される第2スクライブライン内に、ビアホール及び最上層−1層目メタル配線を形成することで実現できる。

【0043】

次に、テストチップ内に形成されたパッド(最上層メタルで形成される)にその一方端が接続された最上層メタル配線を、上記ビアホールに接続させながら、水平方向に形成された第1スクライブライン内に延びるように形成する。これは、ステッパ露光装置の1ショット内にて、2段に形成された半導体装置の間に水平方向に形成される第1スクライブライン内に、配線を形成することで実現可能である。

【0044】

また、テストチップ内に設置するパッド(評価時にテスト針を接触させるもの)は2列に形成する。左側の列のパッドに、テストチップの左側に設置された各半導体装置を1つのブロックとして、これに電流を送り込むように配線を形成する。右側の列のパッドに、テストチップの右側に設置された各半導体装置を同様に1つのブロックとして、これに電流を送り込むように配線を形成する。これにより、1つのテストチップの設置により、電気的に分離された2つのブロックが接続されることとなる。テストチップを基板上にn個設置することで、電気的に分離されたブロックを2n個形成できることとなる。

【0045】

そして、1つのテストチップに接続すべき半導体装置の数が増大しても、スクライブライン内の配線数は増大しない。そのため、1テストチップ(基板上で電気的に独立して複数個形成される)と複数(少なくとも20以上)の半導体装置の接続を、スクライブライン幅の増大を招くことなく実現できる。その結果、スクライブライン幅の増大を招くことなく、各テストチップを介して電気的に接続された、複数個の半導体装置を一括して評価することが可能となる。

【0046】

なお、テストチップ内に、半導体装置内で構成される各個別能動素子、受動素子単体および、それらを組み合わせて構成される基本回路の電気的特性を評価するための各回路および各パッドを形成することで、半導体装置の一括評価と同時に、これらの評価も可能となり、さらに半導体装置の評価時間の短縮が可能となる。

【0047】

さらに、上記中継回路から各半導体装置内に設置されたパッドへの電気的接続を実現する配線に、メタル配線層より下層にて形成されるポリシリコン材料による配線を用いることで、ダイシング完了時点での個片化された半導体装置の端面にメタル材料が露出することはなくなる。ひいては、メタル材料を介して、テープ側に形成された配線が短絡するという不具合は発生しなくなる。

【0048】

以下この発明の実施例を図面を用いて説明する。

【実施例1】

【0049】

本実施例では、メタル配線層を3層、ポリシリコン配線を1層で形成する大規模集積回路のウェハに適用した場合について説明する。

【0050】

本明細書において、第3層メタル配線とは半導体装置のもっとも表面側に形成される配線をいう。第2層メタル配線とは、第3層メタル配線より1層下に形成される配線をいう。第1層メタル配線とは半導体装置の中でもっとも基板側に形成されるメタル配線をいう。ポリシリコン配線は第1層メタル配線よりさらに下層に形成される。

【0051】

図1は、基板上に複数の半導体装置およびスクライブラインを作りこむための、ステッパ露光装置の1ショットの各層の重ね合わせ(マスクセット)を示す概念図である。

【0052】

図1を参照して、1ショット内には、水平方向に形成された第1のスクライブライン12aが延びる方向に、4個の半導体装置1が並んでなる半導体装置1の列が形成される。半導体装置1の列は、第2のスクライブライン12b(第1のスクライブライン12aと直交する)が延びる方向に、2段に並んで設けられる。図1では、8つの半導体装置を一括して露光する場合を図示しているが、この数に制限されるものではない。

【0053】

図1に示すように、テストチップ3の中に、テスト専用チップ8が設置される。テスト専用チップ8には、第3層配線材にて形成されたパッド電極4が12ヶ(6ヶ×2列)設置される。第3層配線5cは、各々のパッド電極4に接続される。テストチップ3内には、テスト専用チップ8以外に、半導体装置内で使用されるトランジスタのスレッシュ電圧等を測定するための特性テストチップ14が10ヶ設置される。

【0054】

図1に示すように、半導体装置の上下の列の間に形成された水平方向に延びる第1スクライブライン12a内に、第3層メタル配線5が形成される。本実施例では2um幅の第3層メタル配線3本と1um幅の第3層メタル配線3本を配線間スペース1umで形成することで、第1スクライブライン12a内のメタル材料の存在する領域は14um幅にすることができた。本実施例では水平方向に延びる第1スクライブラン12aの幅としては110umを採用した。この配線本数、配線幅、配線間スペースには制限を加えるものではない。

【0055】

図1に示すように、第1スクライブライン12aと第2スクライブライン12bとの交差領域にビアホール10が形成される。ビアホール10によって、第1スクライブライン12a内に形成された第3層メタル配線5と、第2スクライブライン12b内に形成された第2層メタル配線6が接続される。本実施例では2um幅の第2層メタル配線3本と1um幅の第2層メタル配線3本を配線間スペース1umで形成したことで、第2スクライブライン12b内のメタル材料の存在する領域は14um幅にすることができた。本実施例では垂直方向のスクライブラン12b幅としては110umを採用した。この配線本数、配線幅、配線間スペースには制限を加えるものではない。

【0056】

図1に示すように、第2層メタル配線6は、第2スクライブライン12b内に形成された中継回路9に接続されており、この中継回路9内で3つのポリシリコン配線13(半導体装置内の第1層メタル配線よりも下層に形成されている)に接続され、この3つのポリシリコン配線13は各半導体装置の3つの特定パッド2に接続されている。図1では、各半導体装置の特定電極として3つの特定パッド2を示しているが、その数に制限されるものではない。

【0057】

図1に示すようなスクライブライン内に多層配線を形成するにあたり、半導体装置の製造工程と全く同一の工程フローでこれを実現するために、スクライブライン内の配線は、半導体装置を形成するために用いた多層メタル配線材を用いて形成される。

【0058】

なお、図1に示すように、ステッパ用のマーク類7(露光時に下地との位置合わせをするためのもの)が、1ショットの領域11内に設置されており、この部分には配線を設置しない。

【0059】

次に図2から図5を参照して、上記の露光用マスクセットを用いて、基板上に半導体装置およびテストチップを形成する工程を説明する。半導体装置1内には第1層メタル配線を用いてパターンが形成されるが、図示しない。

【0060】

図2は、第1層メタル配線(図示しない)を形成した後の、基板上のパターンの概念図を示す。

図2に示すように、基板の上に、まず、半導体装置1と、一つのテスト専用チップ8と10ケのトランジスタ等特性テストチップ14を含むテストチップ3を形成する。垂直方向に延びる第2スクライブライン12b内であって、半導体装置1の直近に、該半導体装置1と対になるように、テストチップ3と半導体装置1を中継するための中継回路9を設ける。第2スクライブライン12b内において、中継回路9と半導体装置1とをポリシリコン配線13で接続した。これにより基板上の各半導体装置1の個片化を目的としたダイシングを実施したとき、ダイシングラインをまたぐのはポリシリコン配線のみとすることができる。

【0061】

本実施例においては、中継回路9を、後述する第2層メタル配線(テストチップ3内に形成されたテスト専用チップ8から延び、第2スクライブライン12b内を通って形成されるもの)と半導体装置1の特定電極との電気的接続をon/offさせる、スイッチング回路で形成した。しかし、中継回路9は、このような回路に制限されるものではない。この後、第1層メタル配線層(図示せず)まで形成することで、中継回路9が完成する。なお、図中、下の2列の半導体装置の列は、基板内の平坦性を確保するためのダミーである。

【0062】

図3は、第1層メタル配線(図示せず)と第2層メタル配線6をつなぐビアホール(図示せず)を形成後に、第2層メタル配線6まで形成した工程における、基板上のパターンの概念図を示す。図3に示すように、第2スクライブライン12b内に形成された第2層メタル配線6は、各半導体装置1の直近に形成された中継回路9に接続されている。第2層メタル配線6は、中継回路9へ接続することで終端させている。図示しないが、第2層メタル配線6を覆うように絶縁膜が形成される。

【0063】

図4は、第2層メタル配線6と第3層メタル配線(図示せず)を接続するためのビアホール10を上記絶縁膜中に形成した後の、基板上のパターンの概念図を示す。図4に示すように、ビアホール10は、第1スクライブライン12aと第2スクライブライン12bが直交する領域内に形成される。

【0064】

図5は、第3層メタル配線5aまで形成した工程における、基板上のパターンの概念図を示す。図5に示すように、テスト専用チップ8内のパッド電極4aから延びる第3層メタル配線5c(6本)が、水平方向に延びる第1スクライブライン12a内の第3層メタル配線5a(6本)と基板上で接続されることになる。

【0065】

さらに、第3層メタル配線5a(6本)は、対応するビアホール10および第2層メタル配線6(6本)を経由し、各半導体装置1の直近に設けられた中継回路9に平行して接続されることになる。さらに、中継回路9からポリシリコン配線13を用いて半導体装置1の特定パッド2へ接続されることになる。

【0066】

また同様に図5で示すようにテストチップ3内に設置されたテスト専用チップ8中の右列側に設置されたの6つの電極4bから第3層メタル配線5d(6本)が延び、そしてこの第3層メタル配線5d(6本)は、基板上で対応する第3層メタル配線5b(6本)に接続され、さらに、対応するビアホール10および第2層メタル配線6(6本)を経由し、各半導体装置1の直近に設けられた中継回路9に平行して接続される。さらに、中継回路9からポリシリコン配線13を用いて半導体装置の特定パッド2へ接続されることになる。

【0067】

この際、図5に示すように、第3層メタル配線5aは、第1スクライブライン12a内を横方向に延びていき、ビアーホール10を介して、横方向に並んで形成される第2層メタル配線6のそれぞれに順次接続されていき、最後に基板の最外周に設けられた半導体装置1にまで接続されることになる。よって、テストチップ3の左側に形成された全ての半導体装置1は、テスト専用チップ8内の6つの電極4aに電気的に接続されることになる。同様にテストチップの右側でも全ての半導体装置1は、6つの電極4bに電気的に接続されることになる。

【0068】

結果的に図5に示すようにテストチップ3の左右に、2つの、電気的に独立に接続されたブロックが形成された。

【0069】

本実施例では、図6に示すように、基板60上に、テスト専用チップを含むテストチップ62を3つ形成し、6つの電気的に独立に接続されたブロック61を形成した。本実施例では、1つのテストチップ3内に形成されたテスト専用チップ8の左側のパッド電極4aを、最大56ヶの半導体装置の特定パッド2に接続した。この場合でも本手法を用いることで、スクライブライン内の配線数は6本のみで形成されるので、スクライブライン幅を大きくする必要がない。

【0070】

テスト工程においては、テストチップ3内に形成されたテスト専用チップ8の左側のパッド電極4aおよび右側のパッド電極4bに対してテスト針を接触させることで、テストチップ3の左右に形成された半導体装置を一度に一括してテストすることが可能となり、基板の歩留まりを容易に短時間で評価することが可能となった。

【0071】

半導体装置を基板60から個片化するダイシング工程においても、スクライブライン内に形成されたメタル配線の存在領域は第1、第2スクライブライン12a,12b共に,スクライブラインの中心から7umまでの領域に抑えられており、かつ、第2スクライブライン12bから半導体装置1内へ接続するための配線はメタル材料ではなく、ポリシリコン材料であるので、半導体装置1の個片化のためのダイシングを実施した場合、ポリシリコン材料は安定した断面形状を形成するので、半導体装置1の端にまで露出することはない。また、メタル材料は存在しないのでメタル材料の露出もなく、テープへの実装時にテープに形成された配線を短絡させることのない半導体装置が得られ、半導体装置の高い信頼性が確保される。

【0072】

今回開示された実施例はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【産業上の利用可能性】

【0073】

本発明は、特に大型TFT液晶モニター用ドライバなど、基板上に形成された半導体装置をダイシングにより個片化した後、テープへ実装する場合に有効である。

【図面の簡単な説明】

【0074】

【図1】本発明の実施例にかかる、基板上に複数の半導体装置およびスクライブラインを作りこむための、ステッパ露光装置の1ショットの各層の重ね合わせ(マスクセット)を示す概念図(基板上に形成された半導体装置、スクライブライン、およびテストチップの概念図)である。

【図2】第1層配線形成工程後の、基板上に形成された半導体装置、スクライブライン、およびテストチップの概念図を示す。

【図3】第1層配線と第2層配線をつなぐビアホールを形成後に第2配線層まで形成した工程における、基板上に形成された半導体装置、スクライブライン、およびテストチップの概念図を示す。

【図4】第2配線層と第3配線層を接続するためのビアホールを形成した工程における、基板上に形成された半導体装置、スクライブライン、およびテストチップの概念図を示す。

【図5】第3配線層まで形成した工程における、基板上に形成された半導体装置、スクライブライン、およびテストチップの概念図を示す。

【図6】本実施例にかかる、基板上に形成された、テストチップと、6つの電気的に独立に接続されたブロック(半導体装置の集合体)を示す図である。

【図7】従来の規模集積回路のウェハーの平面図である。

【図8】図7のウェハーの一部を拡大して示す平面図である。

【図9】従来のテスト専用チップのブロック図である。

【図10】従来の被テストデバイスのブロック図である。

【符号の説明】

【0075】

1 半導体装置

2 パッド電極

3 テストチップ

4 第3層配線材にて形成されたパッド電極

4a 第3層配線材にて形成された左列側のパッド電極

4b 第3層配線材にて形成された右列側のパッド電極

5 第3層メタル配線

5a テストチップより左側に形成された第3層メタル配線

5b テストチップより右側に形成された第3層メタル配線

5c テストチップ内に形成された第3層メタル配線

5d テストチップ内に形成された第3層メタル配線

6 第2層メタル配線

7 ステッパ用マーク類

8 テスト専用チップ

9 スクライブライン内に設置した中継回路

10 ビアホール

11 ステッパによる1ショットの領域

12a 水平方向に延びる第1のスクライブライン

12b 垂直方向に延びる第2のスクライブライン

13 ポリシリコン配線

14 テストチップ内のトランジスタ等特性テストチップ

61 半導体装置の集合体

62 テストチップ

【特許請求の範囲】

【請求項1】

半導体基板の上に設けられ、半導体装置のテストを行うための、パッド電極を含むテストチップと、

前記半導体基板の上に、前記テストチップを間に挟んで、第1のスクライブラインが延びる方向に、複数個の半導体装置が並んでなる半導体装置の列とを備え、

前記半導体装置の列は、前記第1のスクライブラインと直交する第2のスクライブラインが延びる方向に複数並んで設けられ、

前記第2のスクライブライン内に、各半導体装置と対になるように、該半導体装置と前記テストチップを中継する中継回路が設けられ、

前記半導体装置は、該半導体装置の最も基板側に形成された第1層配線を有し、

前記中継回路と前記半導体装置は、ポリシリコン配線で接続されており、

前記中継回路にその一方端が接続された第2層配線が、前記第2スクライブライン内に延びており、

前記テストチップ内に形成された前記パッド電極にその一方端が接続された第3層配線が、前記第1のスクライブライン内に延びており、

前記第2層配線と前記第3層配線は、その間に設けられた絶縁膜を介して上下に隔てて形成されており、かつ該絶縁膜中に設けられたビアホールを介して電気的に接続されている大規模集積回路のウェハ。

【請求項2】

前記ビアホールの形成位置は前記第1スクライブラインと前記第2スクライブラインが直交する領域である請求項1に記載の大規模集積回路のウェハ。

【請求項3】

前記第2層配線及び第3層配線の配線幅は、それぞれ1〜2μmである、請求項1または2に記載の大規模集積回路のウェハ。

【請求項4】

前記第2層配線及び第3層配線は、それぞれ複数本形成されており、該配線の間隔は1〜2μmである請求項1から3のいずれか1項に記載の大規模集積回路のウェハ。

【請求項5】

前記第2層配線及び第3層配線は、それぞれ6本以上形成されている請求項4に記載のの大規模集積回路のウェハ。

【請求項6】

前記ポリシリコン配線はトランジスタのゲート電極の構成と同一である請求項1に記載の大規模集積回路のウェハ。

【請求項7】

前記テストチップ1つに対し、接続する前記半導体装置の数が20以上であることを特徴とする請求項1に記載の大規模集積回路のウェハ。

【請求項8】

前記テストチップ内に設けられた前記テストパッド電極は2列に配置され、

テスト工程において、前記テストパッド電極にテスト針を接触させることで、前記テストパッドの左右に形成された前記半導体装置を一度に一括してテストすることが可能にされた請求項1から7のいずれか1項に記載の大規模集積回路のウェハ。

【請求項9】

半導体基板の上に、テストチップを間に挟んで、第1のスクライブラインが延びる方向に、第1層配線を有する半導体装置が複数個並んでなる半導体装置の列を、前記第1のスクライブラインと直交する第2のスクライブラインが延びる方向に複数並べて設ける工程と、

前記第2のスクライブライン内に、前記半導体装置と前記テストチップを中継する中継回路を設ける工程と、

前記中継回路と前記半導体装置を、ポリシリコン配線で接続する工程と、

前記中継回路にその一方端が接続され、かつ前記第2スクライブライン内に延びるように第2層配線を形成する工程と、

前記第2層配線を覆うように前記半導体基板の上に絶縁層を形成する工程と、

前記絶縁層中に、前記第2層配線に至るビアホールを形成する工程と、

前記テストチップ内に形成されたパッド電極にその一方端が接続されるように、かつ前記ビアホールに接触させながら前記第1のスクライブライン内に延びるように、前記絶縁層の上に第3層配線を形成する工程とを備えた大規模集積回路のウェハの製造方法。

【請求項10】

前記ビアホールの形成位置を、前記第1スクライブラインと前記第2スクライブラインが直交する領域に選ぶ請求項9に記載の大規模集積回路のウェハの製造方法。

【請求項1】

半導体基板の上に設けられ、半導体装置のテストを行うための、パッド電極を含むテストチップと、

前記半導体基板の上に、前記テストチップを間に挟んで、第1のスクライブラインが延びる方向に、複数個の半導体装置が並んでなる半導体装置の列とを備え、

前記半導体装置の列は、前記第1のスクライブラインと直交する第2のスクライブラインが延びる方向に複数並んで設けられ、

前記第2のスクライブライン内に、各半導体装置と対になるように、該半導体装置と前記テストチップを中継する中継回路が設けられ、

前記半導体装置は、該半導体装置の最も基板側に形成された第1層配線を有し、

前記中継回路と前記半導体装置は、ポリシリコン配線で接続されており、

前記中継回路にその一方端が接続された第2層配線が、前記第2スクライブライン内に延びており、

前記テストチップ内に形成された前記パッド電極にその一方端が接続された第3層配線が、前記第1のスクライブライン内に延びており、

前記第2層配線と前記第3層配線は、その間に設けられた絶縁膜を介して上下に隔てて形成されており、かつ該絶縁膜中に設けられたビアホールを介して電気的に接続されている大規模集積回路のウェハ。

【請求項2】

前記ビアホールの形成位置は前記第1スクライブラインと前記第2スクライブラインが直交する領域である請求項1に記載の大規模集積回路のウェハ。

【請求項3】

前記第2層配線及び第3層配線の配線幅は、それぞれ1〜2μmである、請求項1または2に記載の大規模集積回路のウェハ。

【請求項4】

前記第2層配線及び第3層配線は、それぞれ複数本形成されており、該配線の間隔は1〜2μmである請求項1から3のいずれか1項に記載の大規模集積回路のウェハ。

【請求項5】

前記第2層配線及び第3層配線は、それぞれ6本以上形成されている請求項4に記載のの大規模集積回路のウェハ。

【請求項6】

前記ポリシリコン配線はトランジスタのゲート電極の構成と同一である請求項1に記載の大規模集積回路のウェハ。

【請求項7】

前記テストチップ1つに対し、接続する前記半導体装置の数が20以上であることを特徴とする請求項1に記載の大規模集積回路のウェハ。

【請求項8】

前記テストチップ内に設けられた前記テストパッド電極は2列に配置され、

テスト工程において、前記テストパッド電極にテスト針を接触させることで、前記テストパッドの左右に形成された前記半導体装置を一度に一括してテストすることが可能にされた請求項1から7のいずれか1項に記載の大規模集積回路のウェハ。

【請求項9】

半導体基板の上に、テストチップを間に挟んで、第1のスクライブラインが延びる方向に、第1層配線を有する半導体装置が複数個並んでなる半導体装置の列を、前記第1のスクライブラインと直交する第2のスクライブラインが延びる方向に複数並べて設ける工程と、

前記第2のスクライブライン内に、前記半導体装置と前記テストチップを中継する中継回路を設ける工程と、

前記中継回路と前記半導体装置を、ポリシリコン配線で接続する工程と、

前記中継回路にその一方端が接続され、かつ前記第2スクライブライン内に延びるように第2層配線を形成する工程と、

前記第2層配線を覆うように前記半導体基板の上に絶縁層を形成する工程と、

前記絶縁層中に、前記第2層配線に至るビアホールを形成する工程と、

前記テストチップ内に形成されたパッド電極にその一方端が接続されるように、かつ前記ビアホールに接触させながら前記第1のスクライブライン内に延びるように、前記絶縁層の上に第3層配線を形成する工程とを備えた大規模集積回路のウェハの製造方法。

【請求項10】

前記ビアホールの形成位置を、前記第1スクライブラインと前記第2スクライブラインが直交する領域に選ぶ請求項9に記載の大規模集積回路のウェハの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2006−339228(P2006−339228A)

【公開日】平成18年12月14日(2006.12.14)

【国際特許分類】

【出願番号】特願2005−159084(P2005−159084)

【出願日】平成17年5月31日(2005.5.31)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成18年12月14日(2006.12.14)

【国際特許分類】

【出願日】平成17年5月31日(2005.5.31)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]