Fターム[4M106AC07]の内容

半導体等の試験・測定 (39,904) | テスト用回路 (391) | チップ内テスト回路 (154)

Fターム[4M106AC07]の下位に属するFターム

Fターム[4M106AC07]に分類される特許

1 - 20 / 46

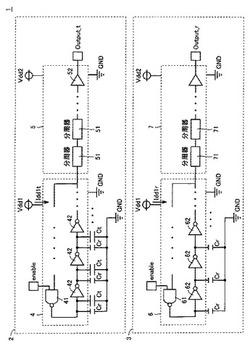

容量測定回路、半導体装置および容量測定方法

【課題】本発明は、特別な装置を用いずに、微細素子の容量を直接測定することができる容量測定回路、半導体装置および容量測定方法を提供する。

【解決手段】本発明に係る容量測定回路1は、少なくとも1つの第1リングオシレータ(測定用リングオシレータ4)と、第1周辺回路部(測定用周辺回路部5)と、第2リングオシレータ(参照用リングオシレータ6)と、第2周辺回路部(参照用周辺回路部7)とを備えている。第1リングオシレータおよび第2リングオシレータに電力を供給する電源と、第1周辺回路部および第2周辺回路部に電力を供給する電源とは異なる。容量測定回路1は、第1出力信号の周波数および第1リングオシレータに流れる電流値より算出した第1容量から、第2出力信号の周波数および第2リングオシレータに流れる電流値より算出した第2容量を差引くことで測定対象の容量を測定することができる。

(もっと読む)

半導体集積回路のテスト回路及び方法

【課題】ウェハ上の単一チップに形成された貫通ビアの不良の可否をテストすることができ、またパッケージングされた半導体集積回路に形成された貫通ビアの不良の可否をテストすることができる半導体集積回路のテスト回路及び方法を提供する。

【解決手段】半導体集積回路のテスト回路1は貫通ビア100、電圧駆動部200及び判定部300を含む。前記貫通ビア100は入力電圧V1を受信する。前記電圧駆動部200は前記貫通ビア100と連結されて前記入力電圧V1を受信し、テスト制御信号EN_P,EN_Nに応答して前記入力電圧V1のレベルを変化させてテスト電圧VTを生成する。前記判定部300は前記入力電圧V1及び前記テスト電圧VTを比較して結果信号を出力する。

(もっと読む)

半導体記憶装置

【課題】メモリセルの非アクティブ(非選択)時に定常的なリーク電流が発生するのを防止する半導体記憶装置を提供する。

【解決手段】ビット線(BIT/BITB)と、前記ビット線に接続されるメモリ要素(メモリセルまたはローカルセンスアンプ)と、ワード線が活性化(WL=H)されることにより前記メモリ要素がアクティブ状態とされる直前の所定期間(PRE=L)だけ前記ビット線に所定電圧(VDD)を印加するプリチャージ回路と、を有する。

(もっと読む)

試験装置

【課題】プローブ検査においても、理想の電源環境を提供する。

【解決手段】試験装置は、ウエハ上に形成されたDUT1を試験する。電源補償回路20は、制御信号SCNT1、SCNT2に応じて制御されるソーススイッチSW1、シンクスイッチSW2を含み、それぞれがオンした状態において補償パルス電流ISRC、ISINKを生成し、補償パルス電流ISRCをメイン電源とは別経路からDUT1の電源端子P1に注入し、またはメイン電源からDUT1へ流れる電源電流から、補償パルス電流ISINKをDUT1とは別経路に引きこむ。電源補償回路20のうち、ソーススイッチSW1、シンクスイッチSW2を含む一部は、ウエハW上に形成される。ウエハには、ウエハ上に形成される電源補償回路20の一部に信号を印加するためのパッドP5〜P7が設けられる。

(もっと読む)

集積回路およびウェーハを試験する無線周波数技術構造および方法

【課題】集積回路を有するウェーハの無線試験を行うためのウェーハ上に形成された試験回路を含む装置および方法を提供する。

【解決手段】ウェーハ16の外部にある試験ユニット12、および集積回路を含むウェーハ上に製造された少なくとも1つの試験回路14を含む。試験ユニット12は、RF信号を送信し、試験回路14に電力を供給する。試験回路14は、可変リング発振器を含み、集積回路の公称動作周波数での一連のパラメータ試験を実行し、試験結果を分析のために試験ユニット12に送信する。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップのテスト時間を短縮可能な半導体装置の製造方法を提供する。

【解決手段】半導体ウエハ10a,10bに、パッドとを有し、且つパッドが半導体チップ11a,11bの主面に形成されたパッド16a,16bと半導体チップの主面と相対向する半導体ウエハの主面に形成されてパッドと電気的接続されたパッド17a,17bとを有するテスト回路を内蔵した半導体チップを複数、形成する工程と、複数の半導体ウエハを、隣接する半導体ウエハにおける半導体チップの入力パッドの各々を互いに接触させて検査装置40のステージ上に載置する工程と、載置された複数の半導体ウエハのうち外側の半導体ウエハにおける半導体チップのパッドに検査装置40のプローブ針43を接触し、半導体チップの各々を一括でテストする工程とを備えることを特徴とする半導体装置。

(もっと読む)

半導体装置、半導体装置の製造精度判定方法及びその装置

【課題】短時間でウエハー面内分布などの数多くのパターン変換差に係るデータを収集することができ、適切に半導体装置の製造精度判定或いは管理を行い得る。

【解決手段】複数の異なる面積を有するキャパシタを、半導体素子生成工程においてアクティブエリアに形成し、各キャパシタに電圧を印加して、夫々のキャパシタ電流を検出し、検出された電流値と対応するキャパシタの面積とからアクティブエリアのパターン変換差を算出し、パターン変換差に基づき製造精度を判定する。

(もっと読む)

半導体集積回路及び半導体集積回路の試験方法

【課題】実際の動作条件下においてエレクトロマイグレーションの劣化現象を検知すると共に、故障の兆候を検知することが可能な半導体集積回路を提供することである。

【解決手段】本発明にかかる半導体集積回路10は、カウンタ回路6と、遅延クロック信号56を生成する遅延素子5と、クロック信号52のクロックサイクル毎にトグルするデータを入力する第1のフリップフロップ1と、第1のフリップフロップ1からの出力信号を入力する配線4と、遅延クロック信号56に基づき駆動し、配線4からの出力信号を入力する第2のフリップフロップ2と、クロック信号52に基づき駆動し、第1のフリップフロップ1からの出力信号を入力する第3のフリップフロップ3と、第2及び第3のフリップフロップ2、3からの出力信号の排他的論理和を出力する排他的論理和回路7と、を有する。

(もっと読む)

剥離テスト装置及び剥離テスト方法

【課題】剥離が発生した段階を知ることのできるテスト方法の提供。

【解決手段】前記複数の剥離補強ブロック2−1,2,3,4の各々は、複数の配線層に形成された配線群と、前記複数の配線層間で前記配線群を電気的に接続する、導体ホールとを備える。前記テスト回路1は、前記複数の剥離補強ブロックに対応して設けられた、複数のデータ保持回路と、前記複数の剥離補強ブロックの各々の一端に、テスト信号を供給する、テスト信号供給端と、前記複数のデータ保持回路に接続された、不揮発性の記憶回路とを備える。前記複数のデータ保持回路の各々は、対応する前記各剥離補強ブロックの他端から前記テスト信号に応じて出力される信号をテスト結果データとして保持する。前記不揮発性の記憶回路は、前記各データ保持回路に保持された前記テスト結果データを、前記各データ保持回路と対応付けて記憶するように、前記各データ保持回路と接続されている。

(もっと読む)

プロセス、電圧、および温度センサ

集積回路は、プロセスセンサと温度センサと電圧センサとを含む。プロセスセンサは、集積回路が形成される半導体プロセスを示すプロセスパラメータを検知し検知されたプロセスパラメータに基づいて上記半導体プロセスの特徴をプロセスセンサの出力に与えるように構成される。温度センサは、集積回路の温度の表示を温度センサの出力に与えるように構成され、電圧センサは、集積回路の電源電圧レベルの表示を電圧センサの出力に与えるように構成される。プロセスセンサの出力は、温度センサおよび電圧センサのうち少なくとも一方に結合されて、温度の表示および電源電圧レベルの表示のうち少なくとも一方を補償する。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造管理方法

【課題】製造マージンの評価や製造マージンの管理を容易にする半導体装置を提供する。

【解決手段】セルアレイを含む半導体装置において、セルアレイの周囲に設けられたダミー領域にセルアレイのセルと略同一形状のレイアウトパターンを有するプロセス不良検出回路を設ける。特に、プロセス不良検出回路がセルアレイの周辺部に設けられたダミーパターンとしての機能を備えることによって、プロセス不良検出回路によるチップ面積を抑制できる。

(もっと読む)

半導体製品ダイのテスト方法及び同テストのためのテストダイを含むアセンブリ

【課題】製品ダイ(2011,300)の製品回路(202,302,304)をテストするためのテストアセンブリ(2000)を提供すること。

【解決手段】一実施形態では、テストアセンブリは、テストダイ(2010,400)及び該テストダイをホストコントローラ(2002)へ電気的に結合する相互接続基板(2008)を含む。該テストダイは、テスト回路(202A,402,404)及び製品回路を統合化された設計(102)に同時に設計するステップを含むテストダイ及び製品ダイに関する設計方法論(100)に従って設計可能である。テスト回路は、該テスト回路により必要とされるシリコン領域の量にほぼ関係なく、対応する製品回路に関して高度の欠陥検出範囲を提供するよう設計可能である。次いで該設計方法論は、統合化された設計をテストダイ及び製品ダイへと分割する(104)。テストダイはテスト回路を含み、製品ダイは製品回路を含む。

(もっと読む)

半導体装置の検査方法及び半導体装置

【課題】個々の半導体装置について、試験工程での書き換え回数を信頼性高く管理できるようにした半導体装置の検査方法及び半導体装置を提供する。

【解決手段】データの書き換えが可能なメモリ回路23を備えるICチップの検査方法であって、メモリ回路23に、ユーザによって使用される主記憶領域31と、試験用記憶領域33とを用意しておき、主記憶領域31に対してデータの書き換え試験を行う工程と、書き換え試験を行う工程で主記憶領域31に対して実際に行われたデータの書き換え回数を試験用記憶領域33に記録する工程と、を含む。このような方法によれば、個々のICチップについて、その出荷前の試験工程で実際に行われたデータの書き換え回数を正確に管理することができる。

(もっと読む)

チェックパターン及び実装評価装置

【課題】ガードリングの外側に発生した損傷を簡単で確実に検出して、半導体チップの実装評価を行うことができるチェックパターン及び実装評価装置を提供する。

【解決手段】ダイシングを行うためのスクライブ領域6からガードリング4の外側領域に、半導体チップ5aの内側に向かって電気回路2を所定の間隔を隔てて複数並列接続、又は複数並列配置されてなる検出部20と、当該検出部20に接続され、前記ガードリング4の外側に配設される出力端子3とを備え、電気回路2の断線によるインピーダンスの変化量に基づいて、ガードリング4の外側領域に発生した損傷の状態を解析する。

(もっと読む)

ウエハレベルCSPにおける絶縁性テスト方法及びこれに用いるTEGパターン

【課題】本発明の課題は、絶縁性能の判定精度の向上を図り得るTEGチップを提供することにある。

【解決手段】本発明の第1の態様は、TEGパターンを用いたウエハレベルCSPの絶縁性テスト方法において、渦巻き状のTEGパターンを用いたことを特徴とする。また、本発明の第2の態様は、インダクタ素子を有するウエハレベルCSPの絶縁性テストに使用されるTEGパターンにおいて、前記TEGパターンは、渦巻き状に成形されていることを特徴とする。

(もっと読む)

半導体装置及びその試験方法

【課題】大掛かりな装置を付加使用することなく可及的に簡易な構成により半導体チップ単位における試験用針の接触回数を容易且つ確実に把握して管理することができ、ひいては製造コストの削減及び製造時間の短縮化を可能とする。

【解決手段】スクライブ領域3上に、半導体チップ2ごとに対応して、第1の電極パッド11にプローブ針が接触した接触回数、更には試験回数を記憶する記憶部である複数のヒューズ13が設けられている。そして、半導体チップ2上で第1の電極パッド11に隣接して、ヒューズ13に対して接触回数及び試験回数の読み取り及び書き込みを行うための複数の第2の電極パッド12が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】デバイスと高さの異なるモニタが同一ウェハに設けられた半導体装置において、デバイスに成膜された半導体膜を研磨する際に、膜厚のばらつきを抑えること。

【解決手段】シリコン基板であるウェハ1内に、デバイス形成領域2とPCM形成領域3とが設けられたチップ11を形成し、デバイス形成領域2にエピタキシャル層を形成する際に、PCM形成領域3にはエピタキシャル層を形成しない。ついで、エピタキシャル層を所定の厚さにするために、ウェハ1と研磨パッド6とを加圧して研磨する。ついで、デバイス形成領域2に形成されたエピタキシャル層と、PCM形成領域3におけるシリコン基板とに、同条件で、同時期に、イオンを注入する。

(もっと読む)

ウエハ及びその温度試験方法

【課題】設備コストを増大させることなくウエハレベルの温度試験を実施すること。

【解決手段】複数の半導体チップ5が形成されたウエハ1が提供される。そのウエハ1は、ウエハ1に埋め込まれ周囲の温度を所定の目標温度に制御する温度制御回路20と、温度制御回路20を起動するための起動信号STが外部から入力されるパッド10と、を備える。温度制御回路20は、起動信号STに応答して起動した後、他の制御信号を受けることなく自動的に温度制御を行う。

(もっと読む)

劣化検知回路及び半導体集積回路

【課題】出荷後のLSIにおけるエレクトロマイグレーション劣化現象を検知することが可能な半導体集積回路を提供する。

【解決手段】エレクトロマイグレーション現象による配線劣化を検知する劣化検知回路(1)をN(但し、Nは、2以上の整数)個含んで構成する半導体集積回路であり、劣化検知回路(1)は、クロック信号を入力し、当該クロック信号の2倍の周波数を持つ倍周信号を生成する倍周回路(10)と、クロック信号の半分の周波数をもつ分周信号を生成する分周回路(11)と、分周信号を入力し、配線劣化を検知するテスト回路(17)と、倍周信号を入力し、テスト回路(17)を加熱するヒータ回路(16)と、を有することを特徴とする。

(もっと読む)

半導体集積回路

【課題】ウエハテスト用パッドとボンディングパッドを兼用していたので、パッドのサイズおよびピッチを縮小することが困難で、チップ面積が大きくなり、かつ高周波特性を改善することができなかったという課題を解決する手段の提供。

【解決手段】差動出力部11の出力によって操作される選択スイッチを内蔵した状態検出部20によって差動出力部の出力状態を検出できるようにし、かつウエハテスト用パッド21とボンディングパッド22および23とを分離した。ボンディングパッド22および23のサイズとピッチを縮小することができるので、チップ面積を小さくすることができると共に、高周波特性を改善することができる。また、ウエハテスト用パッド21の配置の自由度が増すので、チップ面積をさらに縮小できる。

(もっと読む)

1 - 20 / 46

[ Back to top ]