Fターム[4M106CA01]の内容

半導体等の試験・測定 (39,904) | 検査内容 (5,684) | 電圧−電流特性 (1,196)

Fターム[4M106CA01]に分類される特許

61 - 80 / 1,196

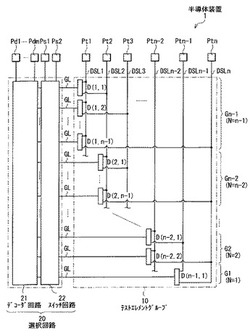

テストエレメントグループおよび半導体装置

【課題】小さな面積でより多くの素子を搭載することができ、さらに、素子特性を精度良く測定することの可能なテストエレメントグループおよびそれを備えた半導体装置を提供する。

【解決手段】各グループGNにおいて、全ての入力端子INが共通のドレインソース線DSLに接続されている。各グループGNにおいて、全ての出力端子OUTが入力端子INに非接続のドレインソース線DSLに、他の出力端子OUTと非共有で接続されている。さらに、一のグループGNにおける共通のドレインソース線DSLと、他のグループGNにおける共通のドレインソース線DSLとが互いに異なっている。

(もっと読む)

半導体回路装置、半導体回路装置の測定方法

【課題】マイクロバンプに対応した測定用のパッドを有する半導体回路装置のアクセス時間tACの測定がより高精度に行えるようにする。

【解決手段】測定クロック生成回路200はメモリ部140の動作クロックCLK2のタイミングを変化させることで測定クロックCLK3を生成する。フリップフロップ154と排他的論理和ゲート155から成る部位は、比較結果信号XOR1として、出力データDoutの位相が測定クロックCLKに対して進んでいるときと遅れているときとで異なる値の信号を出力するように動作する。そこで、測定クロックCLK3のタイミングを変化させながら出力データDoutと測定クロックCLKの位相が一致するタイミングを特定し、アクセス時間tACを求める。

(もっと読む)

半導体装置の製造方法

【課題】検査コストや解析コスト、製品コストを低減可能な半導体装置の製造方法を提供する。

【解決手段】例えば、ウエハ検査工程(S1003)で、半導体ウエハ上のロジック回路を対象とした電気的検査(ロジック部テスト)(S1003a)と、メモリ回路を対象とした電気的検査(メモリ部テスト)(S1003b)を行い、それぞれの検査結果から得られた故障箇所を複合マップ24上に重ねて表示する。この複合マップ24を用いると、例えば、ロジック故障22とメモリ故障23が併存して分布する領域を判別でき、この領域に対してメモリ故障23に対する詳細解析を優先的に行うことで、特にロジック故障22とメモリ故障23の故障原因が共通であった場合に効率的な詳細解析を行うことが可能となる。

(もっと読む)

インターポーザ基板

【課題】 測定端子を固定するための基板の変形が少なく、測定端子が半導体チップとなる部分の電気特性を正確に測定することができ、かつアライメントマークを認識しやすくするためのインターポーザ基板を提供する。

【解決手段】 セラミックスからなるインターポーザ基板の主面に、アライメントマークとしての有底穴を有し、有底穴の底面が中心に向かって深くなっている凹状であることとしたことから、インターポーザ基板の強度がアライメントマークが貫通穴である場合に比べて増加し製品の撓みが抑えられ、高精度な位置決めを行なうことができる。さらに有底穴の底面のフラットに近い面積が小さくなるため、画像認識のための反射光を減少させることができ、アライメントマークと主面とのコントラストを大きくすることができアライメントマークの認識性を向上できる。

(もっと読む)

プローブカード及びそれを備えた半導体装置の検査装置並びに半導体装置の検査方法

【課題】接触方式及び非接触方式の両方式を用いて供給することが可能な半導体装置の検査において、異なる種類の半導体装置を検査する際の検査に要するコストが増大し、さらに、微細ピッチで配置された半導体装置を検査できない。

【解決手段】本発明のプローブカードは、基板と、基板上に、第1の方向に第1の間隔で配置された複数の接触端子部と、基板上に、第1の方向に第2の間隔で配置された複数の非接触インタフェースと、を備え、非接触インタフェースが第1の方向に第2の間隔で配置された領域に含まれる有効プローブカード領域であって、有効プローブカード領域の両端に配置された非接触インタフェース間の距離である有効プローブカード長さが、第1の間隔と第2の間隔の最小公倍数の整数倍である。

(もっと読む)

ウエハチャックの傾き補正方法及びプローブ装置

【課題】半導体ウエハに形成された複数の半導体チップの全領域を覆うプローブカードでもウエハチャックの傾きを確実に補正することができるウエハチャックの傾き補正方法及びプローブ装置を提供する。

【解決手段】本発明のウエハチャックの傾き補正方法は、複数の半導体チップTに、半導体チップ一つ分の接触荷重を付与した時の上記ウエハチャックの傾きを補正する補正量を予め算出し、上記各補正量をデータ記憶部に記憶させる第1の工程と、複数のプローブ14Aと半導体ウエハWを電気的に接触させる第2の工程と、複数のプロープ14Aと半導体ウエハWが電気的に接触した時に、複数のプローブ14Aが接触する複数の半導体チップTそれぞれの補正量を計算し、これらの補正量を加算してウエハチャックの傾きの補正量としての全補正量を算出する第3の工程と、全補正量に基づいてウエハチャック13の傾きを補正する第4の工程と、を備えている。

(もっと読む)

半導体装置の検査用素子及びその製造方法。

【課題】半導体装置の検査装置においては、非接触通信に適した構成を得ることが困難で、かつ高い信頼性を得ることが困難である。

【解決手段】本発明の半導体装置の検査用素子は、基材と、基材上に配置され検査回路と非接触結合回路を備えた回路層を有する検査回路基板と、検査回路基板との一の主面に接続され貫通電極を備えた支持基板とを有する。

(もっと読む)

被検査装置用インタフェース回路

【課題】 半導体装置の大型化を抑制できる被検査装置用インタフェース回路を提供する。

【解決手段】 検査装置4により検査される被検査装置5に設けられた端子回路7と接続されて、検査装置4と非接触で通信する第1の入出力回路6を備え、かつ、端子回路7が被検査装置5に信号を入力する回路の場合には、第1の入出力回路6は入力回路により形成され、端子回路7が被検査装置5から信号を出力する回路の場合には、第1の入出力回路6は出力回路により形成されている。

(もっと読む)

半導体装置

【課題】 ウエハ上に形成された半導体チップを試験するときに、プローブの移動回数を最小限にし、試験時間を短縮する。

【解決手段】 半導体装置は複数の半導体チップを有し、各半導体チップは、試験信号に応じて試験される回路ブロックと、回路ブロックから出力される試験結果を、隣接する半導体チップの少なくともいずれかと試験結果出力端子とに出力するとともに、隣接する半導体チップから転送される試験結果を隣接する別の半導体チップと試験結果出力端子とに出力する転送回路とを有する。これにより、半導体チップの試験結果を隣接する半導体チップに順次に転送できるため、全ての半導体チップの試験結果を1つの半導体チップの試験結果出力端子から出力できる。

(もっと読む)

評価素子

【課題】チャージアップした電荷を検出する感度を向上させること。

【解決手段】半導体基板10上に形成された絶縁膜14と、前記絶縁膜内に形成され、延伸方向に延伸した延伸部22を含む第1配線20と、前記絶縁膜内に設けられ、前記半導体基板と前記延伸部とを電気的に接続するコンタクト26と、前記絶縁膜内に形成され、前記延伸部と前記半導体基板の面方向に対向し前記延伸部より長さの短い対向部32と、前記対向部から前記第1配線の反対方向に引き出される引き出し部34と、を含む第2配線30と、前記引き出し部に電気的に接続されたアンテナ電極40と、含む評価素子。

(もっと読む)

半導体製造装置の管理方法及び管理システム

【課題】ウェハの分類等に関し各種の不良領域の高精度な分類等を可能とする。

【解決手段】本方法及びシステムでは、フェイルビット解析結果やクリティカルエリア等の情報を用いて、ウェハ領域を、異物不良領域(E1)、同心円状不良領域(E2)、及びクラスタ不良領域(E3)に分類する処理を行う。そして、各領域の不良率(工程ごと、フェイルビットモードごと等)を求め、その結果情報を出力する。分類処理は、ウェハ領域分割(S501)、チップ単位の不良数の算出(S502)、ヒストグラム作成(S503)、領域合成・異常値チップ除外(S504)、第1の分類(E1,E2)(S505)、第2の分類(E3)(S506)、分類確定(S507)等から成る。

(もっと読む)

半導体装置およびその検査方法

【課題】半導体基板上に形成された周辺回路上にさらに多層配線層が形成された構造の半導体装置において、周辺回路を構成する素子の特性を変化させずに周辺回路の不良解析を行うことができる半導体装置を提供する。

【解決手段】半導体基板11と、半導体基板11上に層間絶縁膜30を介して形成される多層配線構造を有する不揮発性メモリ層14と、半導体基板11上に形成され、不揮発性メモリ層14中のメモリセルを制御する回路を含む周辺回路12と、を備え、周辺回路12を構成する素子に接続され、周辺回路12の外部に引き出される配線35と、配線35の形成位置に対応する半導体基板11の上面から所定の深さまで設けられる拡散層27と、配線35と拡散層27との間を接続するコンタクト31と、を有する電極加工部15が、半導体基板11上の周辺回路12の形成領域R1以外の領域R2に形成される。

(もっと読む)

検査用半導体装置および半導体装置の検査方法

【課題】非接触インタフェースを備えた半導体装置において、異なる種類の半導体装置を検査する際のコストが増大する。

【解決手段】

検査用半導体装置は、検査用LSIを備え、その検査用LSIは検査対象半導体装置との間で非接触で信号を通信するための複数の非接触インタフェースと、非接触インタフェースに接続された通信部と、通信部を制御する通信制御部と、を有する。通信制御部は、検査対象半導体装置の構成に応じて通信部の動作状態を制御する。

(もっと読む)

プローブカード

【課題】隣接するプローブ間で電気的な結合が生じ難く、半導体チップの電気的特性を精度良く測定できるプローブカードを提供する。

【解決手段】本発明に係るプローブカード1は、被検査物(半導体チップ100、200、300)のパッドに接触させる、傾斜プローブ20と、垂直プローブ30と、が基板(第1基板10、第2基板11)に設けられたプローブカードである。傾斜プローブ20は、第1周波数で信号が伝送される1個若しくは隣接して配置される複数の第1信号パッドから構成された第1パッドグループ、又は第1パッドグループに隣接して配置される第2パッドグループのいずれか一方のパッドグループを構成するパッドに電気的に接触可能に配置される。垂直プローブ30は、他方のパッドグループを構成するパッドに電気的に接触可能に配置される。

(もっと読む)

半導体素子及び半導体装置の製造方法

【課題】隣接した半導体素子領域(IC領域)を同時に検査しても、検査用のプローブが外部電極から食み出し難くい、半導体素子、半導体ウエハ、及び半導体装置の製造方法を提供する。

【解決手段】外周に沿って配置された複数の外部電極28を有する、矩形の半導体素子38であって、前記外部電極の対向する二辺が、前記半導体素子の一の対角線34に垂直な方向36を向いている半導体素子。

(もっと読む)

プローブ装置

【課題】 ロジック回路とアナログ回路を混載したシステムLSIのそれぞれの電気的特性を高速テスタを投資することなく低速テスタで、信号伝送速度4Gbps以上の高速テストが可能なプローブ装置を提供する。

【解決手段】 ロジック回路とアナログ回路を混載したシステムLSI3aの電気的特性をテストする電気的測定回路20を搭載したプローブ装置1であって、プローブ装置は、ロジック回路テスト用およびアナログ回路テスト用の電気的測定回路20の少なくとも一方を搭載したロードボード5を備え、ロードボードの上面および下面の少なくとも一方には電気的測定回路20が複数積層され、信号伝送速度4Gbps以上の高周波伝送機能を備えるスパイラル状接触子2、12と、積層可能なスタック式のインターコネクタ16、17,18を備えたプローブ装置。

(もっと読む)

コンタクトプローブ及びこれを用いた電子回路試験装置

【課題】コンタクトプローブのメンテナンスを簡単且つ安価に行うことが可能なコンタクトプローブ及びこれを用いた電子回路試験装置を提供する。

【解決手段】導電性の筒状体からなるスリーブと、 該スリーブ内に摺動自在に嵌合する導電性のプランジャーと、前記スリーブ内に配置され該プランジャーを軸方向に付勢するスプリングとを備え、前記プランジャーは貴金属の中実ムク材によって形成され前記スリーブと着脱可能に構成されている。

(もっと読む)

集積回路及び集積回路の選別テスト方法

【課題】従来では外部機器にテストデータを保持、管理するため、管理精度の確実性に対する問題や管理コストが増大する問題があった。

【解決手段】不揮発性記憶回路と、第1の回路と、を備える集積回路の選別テスト方法であって、少なくとも前記第1の回路に対して第1の条件でテストを行い、前記第1の条件でのテストの第1の結果を前記不揮発性記憶回路に書き込み、前記第1の結果に応じて、前記第1の回路に対して第2の条件でのテストを行い、前記第2の条件でのテストが行われた場合の第2の結果を前記不揮発性記憶回路に書き込み、前記第1の結果もしくは前記第2の結果から前記集積回路を複数のグレードにランク分けする集積回路の選別テスト方法。

(もっと読む)

プローブカードの製造方法およびプローブカード

【課題】プローブ先端の高さ方向および平面方向に関して高精度に位置決め可能なプローブカードの製造方法およびプローブカードを提供する。

【解決手段】プローブが配置された複数のプローブ基板をプローブカードの第1の基板上に固定する工程を含むプローブカードの製造方法であって、前記複数のプローブ基板に配置されたプローブの先端の高さ方向の位置を揃えた状態で、前記複数のプローブ基板を配置する工程と、前記複数のプローブ基板のプローブが配置されていない方の面に、弾性変形し得るスペーサを配置し、固定用樹脂を塗布する工程と、前記弾性変形し得るスペーサが配置され前記固定用樹脂が塗布された前記複数のプローブ基板の面側に前記第1の基板を載せて加圧し、前記弾性変形し得るスペーサを変形させた状態で前記複数のプローブ基板を前記第1の基板に固定する工程とを備える。

(もっと読む)

プローブカード用配線基板およびこれを用いたプローブカード

【課題】 熱負荷試験時において、プローブカード用配線基板に設けられた測定端子とSiウェハの表面に形成された測定パッドとの位置ずれが小さく、電気特性の検査に好適に使用できるプローブカード用配線基板とこれを用いたプローブカードを提供する。

【解決手段】絶縁基体と、この絶縁基体の内部に設けられた銅とタングステンとの複合導体からなる内部配線層とを備えたプローブカード用配線基板であって、絶縁基体を、ムライトを主成分とし、スピネル、ジルコニアおよびフォルステライトから選ばれる1種を有するセラミック焼結体により形成する。

(もっと読む)

61 - 80 / 1,196

[ Back to top ]