Fターム[4M118CA04]の内容

固体撮像素子 (108,909) | 受光部構造 (13,175) | 素子形態 (8,858) | ダイオード (7,206) | pn接合 (3,436) | 埋込層の利用(埋込ダイオード等) (1,894)

Fターム[4M118CA04]に分類される特許

1 - 20 / 1,894

増幅回路および製造方法、撮像素子、並びに電子機器

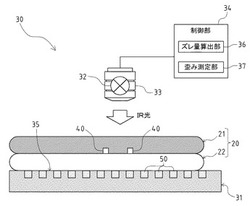

基板の歪み測定装置、基板の歪み測定方法、および半導体装置の製造方法

【課題】基板におけるチップ面積の確保を容易に行うことができ、基板の保持方法による影響を受けることなく、また、高価な計測機器を用いることなく、高精度かつ簡便に、基板の歪みを測定することができる基板の歪み測定装置を提供する。

【解決手段】基板20を保持する保持面に、前記基板20に設けられた位置ズレ測定用のマーク40の比較対象となる基準マーク50を有する基板保持部31と、前記基板20を透過する光を照射する光源部32と、前記光源部32により前記光が前記基板20に照射されることで得られる前記位置ズレ測定用のマーク40と前記基準マーク50との重なりを観察する観察部33と、前記観察部33により観察された前記重なりから、前記基準マーク50に対する前記位置ズレ測定用のマーク40のズレ量を算出する算出部36と、前記算出部36により算出された前記ズレ量から、前記基板の歪みを測定する測定部37とを備える測定装置。

(もっと読む)

固体撮像装置

【課題】固体撮像装置の感度の低下を抑制しつつ、混色を低減させる。

【解決手段】赤色用イメージセンサ3rの光電変換部12rは、青色用イメージセンサ3bの光電変換部12bおよび緑色用イメージセンサ3gの光電変換部12gに対して光入射面から深い位置に配置する。

(もっと読む)

固体撮像素子および製造方法、並びに、電子機器

【課題】良好な感度特性およびスミア特性を両立する撮像機能を備えた電子機器を提供する。

【解決手段】画素21は、全ての画素21において同時に光電変換部31で発生した電荷をメモリ部33に転送し、メタルゲート61、62を有する転送部32、34と、転送部32、34の周囲の層間絶縁膜67を掘り込むことにより形成された溝部にメタル66を埋め込むことにより形成される遮光部とを有する。また、遮光部は、その先端部が、転送部の周囲において、層間絶縁膜67と半導体基板51との間に形成されるライナー膜65の膜厚よりも半導体基板側に突出するように形成される。

(もっと読む)

固体撮像装置及びその製造方法

【課題】フォトダイオードに蓄積された電荷をより正確に読み出す。

【解決手段】固体撮像装置は、半導体基板11と、半導体基板11内に設けられ、第1導電型の半導体層を有するフォトダイオード16と、フォトダイオード16上に設けられ、上部又は全体が第2導電型の半導体層からなるシールド層27と、半導体基板11に設けられ、フォトダイオード16に蓄積された電荷を浮遊拡散層に転送する転送トランジスタ20とを含む。シールド層27の上面は、半導体基板11の上面より高い。

(もっと読む)

撮像装置及び撮像装置の制御方法

【課題】 垂直転送レジスタの電荷の掃き出し駆動を行う際に発生する、撮像素子のポテンシャル電位の揺れ量を軽減し、撮像素子の信号電荷の飽和容量が減少することを抑制する。

【解決手段】 ダイナミックレンジを必要とするときには、垂直CCD23に存在する偽信号電荷を排出するための垂直CCD23の駆動周波数が、ダイナミックレンジを必要としないときを下回り、且つ、信号電荷を転送するときよりも高くなるようにする。

(もっと読む)

固体撮像素子の製造方法及び固体撮像素子

【課題】クラックや剥がれ、空隙などの欠陥が少ない光導波路を有した固体撮像素子や、その製造方法を提供する。

【解決手段】 基板10中に形成され光電変換により電荷を生じる受光部2と、基板10上の受光部2に隣接する位置に形成されて受光部2が生じた電荷の転送を行う転送電極12と、転送電極12上に形成される上部構造14〜16と、をそれぞれ形成する。さらに、少なくとも受光部2の直上かつ上部構造14〜16に挟まれた空間に、光導波路18を形成する。このとき、光導波路18を成す材料を、少なくとも第1ステップ及び第2ステップにより成膜するが、第1ステップは、第2ステップよりも前に行い、第1ステップにおける成膜速度を、第2ステップにおける成膜速度よりも遅くする。

(もっと読む)

撮像装置及びその駆動方法

【課題】 欠陥画素をより精度良く検出するためには撮像素子の温度上昇や信号電荷の蓄積時間を必要とするため、工場出荷前の調整時間に時間が掛かり、生産効率性の点などにおいて問題があった。

【解決手段】 欠陥画素検出時に、撮像素子内の読み出しゲート部に存在する読み出し電極に印加する電位を読み出しゲート部における半導体基板の界面が空乏状態となるような電位を与えるように撮像素子の駆動方法を変更することにより、温度依存及び露光時間依存しているキズの発生頻度を上げ、欠陥画素検出時間の短縮及び検出精度を高めることができる。

(もっと読む)

リニアセンサ及び画像読み取り装置

【課題】ダーク成分やシェーディングの影響の抑制し、読み取り速度の高速化を図る。

【解決手段】リニアセンサ10は、1次元方向に配列された複数の第1光電変換部11aを有する第1センサ列12aと、1次元方向に配列された複数の第2光電変換部11bを有する第2センサ列12bと、各第1光電変換部から信号電荷を読み出して列方向に転送する第1水平転送部14aと、各第2光電変換部から信号電荷を読み出して列方向に転送する第2水平転送部14bと、第1水平転送部により転送された信号電荷を検出して出力し、第2水平転送部により転送された信号電荷を検出して出力する出力部18とを備える。第1光電変換部11aは光が入射する開口を有する受光センサであり、第2光電変換部は光が入射する開口が塞がれた遮光センサであり、各遮光センサは各々対応する受光センサに隣接して設けられ、第1センサ列と第2センサ列とが並列に設けられて構成される。

(もっと読む)

分子検出および識別に応用する多接合フォトダイオード、およびその製造方法

【課題】分子検出および識別に応用する多接合フォトダイオードおよびその製造方法を提供する。

【解決手段】多接合フォトダイオードは、第1導電型ドーパントを有する基板と、第1導電型ドーパントを有するエピタキシー層と、第2導電型ドーパントを有する深ウェル領域と、第1導電型ドーパントを有する第1ウェル領域と、第2導電型ドーパントを有する第2ウェル領域と、第1導電型ドーパントを有する第3ウェル領域と、第2導電型ドーパントを有する第1ドープ領域とを含む半導体装置を提供する。エピタキシー層は、基板の上に配置され、深ウェル領域は、エピタキシー層の中に配置される。第1ウェル領域は、エピタキシー層に接続された3つの側辺を有し、深ウェル領域の中に配置される。第2ウェル領域は、第1ウェル領域の中に配置される。第3ウェル領域は、エピタキシー層に接続された3つの側辺を有し、第2ウェル領域の中に配置される。第1ドープ領域は、第3ウェル領域の中に配置される。

(もっと読む)

固体撮像素子およびその製造方法、並びに電子情報機器

【課題】読み出し特性や感度劣化がなく、熱酸化処理による電荷転送電極間のギャップ部の拡大を回避することができ、これにより、微細で高速転送可能な固体撮像素子を実現する。

【解決手段】固体撮像素子100において、垂直CCD部110は、シリコン基板1内に形成され、信号電荷を転送する転送チャネル3と、シリコン基板1上にゲート絶縁膜7を介して転送チャネル3に沿って配列された複数の電荷転送電極8と、隣接する電荷転送電極8の間に絶縁材料を堆積して形成され、該隣接する電荷転送電極を電気的に分離する電極分離絶縁膜とを有する構造とし、受光部101は、シリコン基板1内に形成され、入射光の光電変換により信号電荷を生成する光電変換領域5と、該光電変換領域の表面部分の熱酸化により形成された熱酸化膜11とを有する構造とした。

(もっと読む)

固体撮像素子、固体撮像素子の製造方法、及び、電子機器

【課題】グローバルシャッタ機能を有し、白点及び暗電流の抑制が可能な固体撮像素子を提供する。

【解決手段】

半導体基体31と、半導体基体31に形成されているフォトダイオード32と、フォトダイオード32に蓄積された信号電荷が転送される浮遊拡散領域35とを備える。さらに、半導体基体31内において浮遊拡散領域35を覆う半導体基体面と平行な水平遮光部32Aと、半導体基体31面と垂直な垂直遮光部32Bとからなる遮光層32とを備える固体撮像素子30を構成する。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮

像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以

下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジス

タの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向

上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリ

コン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

(もっと読む)

エピタキシャルウエーハ及びその製造方法

【課題】 本発明は、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハ及びその製造方法を提供することを目的とする。

【解決手段】 撮像素子製造用のエピタキシャルウエーハを製造する方法であって、前記エピタキシャル層の成長前に、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXを計算し、前記エピタキシャル層の成長において、前記エピタキシャル層を、前記厚さXに加えて、更に前記撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さで成長することを特徴とするエピタキシャルウエーハの製造方法。

(もっと読む)

固体撮像装置およびその製造方法

【課題】ランダムノイズを低減する。

【解決手段】固体撮像装置は、基板上に形成され、光電変換部(PD)と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備え、複数の画素内トランジスタのうちの所定の画素内トランジスタの電極、具体的には、増幅トランジスタのゲート電極のみに接続されるコンタクトの基板に平行な面の形状は、略長方形または略楕円形に形成される。本技術は、CMOSイメージセンサに適用することができる。

(もっと読む)

固体撮像素子ウエハ、固体撮像素子の製造方法、および固体撮像素子

【課題】裏面照射型の固体撮像素子を備えたチップ領域が複数配列された固体撮像素子ウエハにおいて、個片化されるチップ領域のサイズを縮小し、これにより固体撮像素子の小型化を図る。

【解決手段】複数のチップ領域200と、チップ領域200を囲んで配置された分割領域300と、各チップ領域200に設けられた光電変換部20と、各チップ領域200において光電変換部20に対する受光面Aとは逆の表面側に設けられた駆動回路と、駆動回路に接続され各チップ領域200において表面側に引き出されたデバイス用端子33と、駆動回路に接続され分割領域300において受光面A側に露出された検査用端子400とを備えた固体撮像素子ウエハ100−1である。

(もっと読む)

撮像素子、撮像装置、並びに、撮像装置および方法

【課題】画素特性を向上させるとともにスタンバイリーク電流を抑制することができるようにする。

【解決手段】本開示の撮像素子は、半導体基板の表面側に配線層が形成され、裏面側より入射した光を光電変換する裏面照射型の撮像素子であって、前記半導体基板の、画素が形成される画素部、および、周辺回路が形成される周辺回路部の、裏面界面上に形成される負の固定電荷を有する膜と、前記半導体基板の前記周辺回路部の、P型ウェルと前記裏面界面との間から前記周辺回路部と前記画素部との境界近傍まで形成されるN型の濃度が濃いN型領域とを備える。本開示は撮像素子、撮像装置、並びに、製造装置および方法に適用することができる。

(もっと読む)

固体撮像素子およびその製造方法、電子情報機器

【課題】裏面照射型の固体撮像素子の表面側のフォトダイオードと裏面側のマイクロレンズおよびカラーフィルタとのアライメント精度を向上させる。

【解決手段】裏面照射型の固体撮像素子1において、半導体基板としてのシリコン基板2の表面側に、被写体からの画像光を光電変換して撮像する複数の受光部(複数のフォトダイオード3)と、この受光部の形成時に用いた第1アライメントマークを基準にして所定位置に、シリコン基板2上の一または複数の層間膜(層間絶縁膜)を貫通してシリコン基板2に形成されたトレンチ構造の第2アライメントマーク18とを有し、シリコン基板2の裏面側に、第2アライメントマーク18を基準にして、複数の受光部のそれぞれに対応するように所定色配列のカラーフィルタ21およびその上のマイクロレンズ22がそれぞれ形成されている。

(もっと読む)

半導体装置の製造方法

【課題】高いスループットで製造するために有利な製造方法を提供する。

【解決手段】第1領域101および第2領域102を有する半導体基板において、第1絶縁膜112、第2絶縁膜113および第3絶縁膜122を貫通する第1コンタクトホール形成工程と、第4絶縁膜120、第5絶縁膜121および第6絶縁膜122を貫通する第2コンタクトホール形成工程とを含み、前記第1,3,4,6絶縁膜は第1組成を有し、前記第2,4絶縁膜は前記第1組成とは異なる第2組成を有し、開口工程では、前記第2絶縁膜をエッチングストッパとして前記第3絶縁膜をエッチング後に、前記第2絶縁膜および前記第1絶縁膜を互いに異なるエッチング条件で第1コンタクトホールを形成し、前記第5絶縁膜をエッチングストッパとして前記第6絶縁膜をエッチング後に、前記第5,4絶縁膜を同一のエッチング条件で連続的にエッチングして、前記第2コンタクトホールを形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の不純物濃度を好適に制御する半導体装置の製造方法を提供する。

【解決手段】第2トランジスタ170のゲート電極171を半導体基板1に対するマスクとして半導体基板1へイオン注入を行うことにより、第2トランジスタのドレイン175を形成するとともに、第2トランジスタ170のゲート電極171へイオン注入を行う。

(もっと読む)

1 - 20 / 1,894

[ Back to top ]