Fターム[4M119CC02]の内容

MRAM・スピンメモリ技術 (17,699) | 磁化制御技術 (1,406) | 磁界による磁化制御 (394) | 磁界発生電流線による磁化制御 (371)

Fターム[4M119CC02]の下位に属するFターム

回路、タイミングによるもの (44)

Fターム[4M119CC02]に分類される特許

81 - 100 / 327

半導体装置およびその製造方法

【課題】磁気抵抗素子の短絡不良等が軽減される半導体装置と、その製造方法とを提供する。

【解決手段】メモリセルが形成される層間絶縁膜33において、磁気抵抗素子51が形成されるメモリセル領域Mに位置する層間絶縁膜33の部分の上面の位置が、周辺領域Pに位置する層間絶縁膜33の部分の上面の位置よりも低く形成されている。磁気抵抗素子51を覆うように、層間絶縁膜40が形成されている。その層間絶縁膜40に、磁気抵抗素子に電気的に接続されるビット線41が形成されている。磁気抵抗素子51の直下にディジット線31が形成されている。

(もっと読む)

薄膜磁性体記憶装置

【課題】磁気トンネル接合部(MTJ)を有するメモリセルを用いてデータ記憶を行なう薄膜磁性体記憶装置において、データ読出動作を高速化する。

【解決手段】MTJメモリセルに対しては、データ書込およびデータ読出にそれぞれ用いられるライトワード線WWLおよびリードワード線RWLが独立して設けられる。メモリアレイ10を列方向に分割して形成される領域AR1,AR2ごとにリードワード線RWLを分割配置することによって、リードワード線RWLにおける信号伝搬遅延を低減して、データ読出動作を高速化できる。各リードワード線RWLの活性化は、行選択結果に応じてライトワード線WWLと階層的に制御される。ワード線電流制御回路40は、データ書込時およびデータ読出時のそれぞれに対応して、ライトワード線WWLにおける電流経路を形成および遮断する。

(もっと読む)

薄膜磁性体記憶装置

【課題】磁気トンネル接合部(MTJ)を有するメモリセルを用いてデータ記憶を行なう薄膜磁性体記憶装置において、データ読出動作を高速化する。

【解決手段】MTJメモリセルに対しては、データ書込およびデータ読出にそれぞれ用いられるライトワード線WWLおよびリードワード線RWLが独立して設けられる。メモリアレイ10を列方向に分割して形成される領域AR1,AR2ごとにリードワード線RWLを分割配置することによって、リードワード線RWLにおける信号伝搬遅延を低減して、データ読出動作を高速化できる。各リードワード線RWLの活性化は、行選択結果に応じてライトワード線WWLと階層的に制御される。ワード線電流制御回路40は、データ書込時およびデータ読出時のそれぞれに対応して、ライトワード線WWLにおける電流経路を形成および遮断する。

(もっと読む)

自己参照磁気ランダムアクセスメモリセル

【課題】 自己参照磁気ランダムアクセスメモリセルを提供する。

【解決手段】 本発明は、センス層および記憶層間に含まれる絶縁層から形成された磁気トンネル接合部を含む磁気ランダムアクセスメモリセルに関する。本開示はまた、メモリセルに書き込み、かつ読み出すための方法であって、書き込み動作中に、データを前記記憶層に書き込むために前記記憶層の磁化方向を切り替えることと、読み出し動作中に、前記センス層の磁化方向を第1の配向される磁化方向に配向することと、前記磁気トンネル接合部の第1の抵抗値を測定することによって、前記書き込みデータを前記第1の配向された磁化方向と比較することと、を含む方法に関する。開示のメモリセルおよび方法によって、低電力消費および向上した速度で書き込みおよび読み出し動作を実行することが可能になる。

(もっと読む)

半導体装置

【課題】MTJメモリセルを有するMRAMデバイスにおいて、データ読出動作の高速化および、配線層数の減少による製造コスト低減を図る。

【解決手段】MTJメモリセルは、記憶データのデータレベルに応じて抵抗値が変化する磁気トンネル接合部MTJと、アクセストランジスタATRとを備える。アクセストランジスタATRのゲートはリードワード線RWLと結合される。ビット線BLは、磁気トンネル接合部MTJと直接結合されず、アクセストランジスタATRを介して磁気トンネル接合部MTJと電気的に結合される。磁気トンネル接合部MTJは、ライトワード線WWLおよびアクセストランジスタATRの間に結合される。データ読出時において、ライトワード線WWLの電圧は接地電圧Vssに設定されて、データ読出のための電流経路が形成される。さらに、ライトワード線WWLは、ビット線BLよりも上層側に形成される。

(もっと読む)

磁気メモリデバイス

【課題】書込条件の最適化および良否判断を正確に行うことのできる磁気メモリデバイスを提供する。

【解決手段】複数の磁気メモリセルを有するメモリサブアレイ1020と、定電流源1030と、メモリサブアレイ1020と連結された行方向ドライバ1050および列方向ドライバ1040と、メモリサブアレイ1020と連結されたアドレスレジスタ1065、データレジスタ1055、アドレスマルチプレクサ1090、センスアンプ1085、および入出力バッファ1095と、アドレスマルチプレクサ1090と連結されたアドレスバッファ1080とを備える。これにより、他の磁気メモリセルの磁化状態に対して悪影響を与えることのない最適な書込電流の設定が容易になされる。

(もっと読む)

半導体集積回路装置および磁気メモリ装置

【課題】正確に書込データを選択メモリセルに書込むことのできる磁気メモリ装置を提供する。

【解決手段】メモリセルに書込み電流を伝達する書込電流線(BL0、BL1)と平行にかつ異なる配線層に、制御信号を転送する分割構造の制御信号線(210l、211a

、211b)を配置する。電流ドライブ回路が各書込み電流線に対応して配置されて、制御信号線上の制御信号と書込データとに従って対応の書込電流線に電流を流す。

(もっと読む)

半導体装置およびその製造方法

【課題】製造プロセス中に磁性体膜の材料の拡散を防止しながら、高い磁気シールド効果を有するヘテロ構造磁気シールドを備えた半導体装置を提供する。

【解決手段】半導体装置10は、半導体基板20、半導体基板20の主面上に形成され、かつ多層配線層11Bを含む半導体素子12、および半導体素子12を被覆するヘテロ構造磁気シールド170を含む。ヘテロ構造磁気シールド170は、第一の磁気シールド積層構造16Aと磁気シールド積層構造16Aを覆う第二の磁気シールド積層構造16Bを含む。第一および第二の磁気シールド積層構造16Aおよび16Bは、いずれも、半導体素子12を被覆する磁性体からなる磁気シールド膜および半導体素子12と磁気シールド膜との間に介在し磁性体の拡散を防止するバッファ膜とを有する。

(もっと読む)

低書き込み電流を用いる熱支援スピン移動トルク書き込み手順を備えた磁気メモリ

【課題】 低書き込み電流を用いる熱支援スピン移動トルク書き込み手順を備えた磁気メモリを提供する。

【解決手段】 高温閾値で調整可能な第1の磁化を有する強磁性記憶層、固定された第2の磁化を有する強磁性基準層、及び強磁性記憶層と基準層との間に配置された絶縁層から形成された磁気トンネル接合部と、前記磁気トンネル接合部に電気的に接続されかつワード線を介して、制御可能な選択トランジスタと、前記磁気トンネル接合部に電気的に接続され、少なくとも書き込み電流を伝達する電流線と、を含む、熱支援切り替え(TAS)書き込み手順を備えた磁気ランダムアクセスメモリ(MRAM)セルであって、強磁性記憶層の結晶磁気異方性が、強磁性基準層の結晶磁気異方性とほぼ直角であることを特徴とする磁気ランダムアクセスメモリ(MRAM)セル。STTベースTAS−MRAMセルは、熱安定性を実現するのと同時に、低い書き込み電流密度を必要とする。

(もっと読む)

ホイスラー金属の製造方法および磁気抵抗効果膜の製造方法

【課題】比較的に低い温度で結晶格子の規則化を実現することができるホイスラー金属の製造方法を提供する。

【解決手段】ホイスラー金属の製造方法の一具体例は、ホイスラー金属の全ての構成元素を含有する積層体68を形成する工程と、積層体68に加熱処理を施す工程とを備える。積層体68の各層は、ホイスラー金属の構成元素から選択される少なくとも1以上の構成元素で形成される。

(もっと読む)

磁気記憶装置

【課題】MRAMの情報の記録動作時における安定動作と、記録情報の安定保持とを可能にした磁気記憶装置を提供する。

【解決手段】ダイ110は、基板と、第1および第2配線と、磁気記憶素子と、第1の磁気シールド構造とを有する。第1の磁気シールド構造は、平面視において磁気記憶素子を覆うように形成されている。第2および第3の磁気シールド構造113、114は、厚み方向においてダイ110を挟んでいる。リードフレーム部材112は、ダイ110が実装され、かつ強磁性体を含有する。リードフレーム部材112は平面視においてダイ110の一部のみと重複している。

(もっと読む)

磁気抵抗記憶装置及びその製造方法

【課題】磁界書き込み方式の磁気抵抗記憶装置において、記憶情報の熱的安定性を確保しながら、書き込み電流を低減すること。

【解決手段】磁気抵抗記憶装置は、磁気抵抗素子と、第1電流端子及び第2電流端子に接続された配線層と、を備える。データ書き込み時、配線層を通って第1電流端子と第2電流端子との間に書き込み電流が流れる。磁気抵抗素子は、磁化方向が固定された磁化固定層と、書き込み電流により発生する磁界に応じて磁化方向が反転する磁化自由層と、磁化固定層と磁化自由層との間に挟まれた非磁性層と、を備える。配線層は、磁気抵抗素子と少なくともオーバーラップする配線中央部と、配線中央部よりも外側に位置し、配線中央部よりも抵抗値が高い配線側部と、を含む。

(もっと読む)

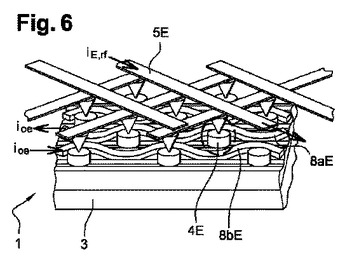

磁気渦記憶装置

本発明は、渦状態の平面磁気セル(4)のネットワークを含む磁気記憶装置(1)であって、各セルの渦コアが、反対方向でありかつセル(4)面に垂直な第1と第2の平衡位置のいずれかの磁化を有し、2つの位置のそれぞれが2進情報を表す、磁気記憶装置(1)に関する。装置(1)は、セルに格納される2進情報を書き込む手段(5、8a、8b、3)であって、各セル(4)の近傍で前記セル(4)面にほぼ垂直な第1のバイアス静磁場と前記セル(4)にほぼ平行な直線偏波無線周波数磁場とを選択的に印加する手段を含む書き込み手段(5、8a、8b、3)を含む。説明の装置はまた、点接触(7)により渦コアの周囲の領域を介し電流線を導くことにより、2つの交差する電極(6)と(9)間の選択的輸送測定を使用して、好ましくは共振的に極性を読み取る手段を含む。  (もっと読む)

(もっと読む)

磁気記憶装置およびその製造方法

【課題】磁気記憶素子の機能低下を抑制することのできる磁気記憶装置およびその製造方法を提供する。

【解決手段】磁気記憶装置は、磁化状態に基づいたデータを保持可能な磁気記憶素子MMと、発生する磁界により磁気記憶素子の磁化状態を変化させることが可能なディジット線DLおよびビット線BLとを備えている。磁気記憶素子MMは、ディジット線DLとビット線BLとの交差部分において、ディジット線DLの上であってビット線BLの下に配置されている。ディジット線DLはこの交差部分において幅WDLを有しており、かつビット線BLはこの交差部分において幅WBLを有している。幅WDLは磁気記憶素子MMの幅WMM1よりも大きく、かつ幅WBLは磁気記憶素子MMの幅WMM2よりも小さい。

(もっと読む)

半導体装置

【課題】内部回路の動作パラメータなどの設定を行うデータを長期にわたって安定に供給する。

【解決手段】第1の動作モード(PROM)時には、不揮発性メモリセルに対し非破壊的に書換え可能な態様でデータを書込み、第2の動作モード(OTP)時には不揮発性メモリセルに対し、破壊的に書換え不可能な態様でデータを書込む。この不揮発性メモリセルは、記憶素子として、可変磁気抵抗素子を有し、可変磁気抵抗素子の抵抗値に応じて情報を不揮発的に記憶する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】磁気抵抗変化素子を備えたメモリセルに記憶された2値の情報を適切に読み出すことができる半導体記憶装置等を提供する。

【解決手段】記憶用磁気抵抗変化素子を備えた複数のメモリセルを含むメモリセルアレイ51と、参照用磁気抵抗変化素子を備えた複数の参照セルを含み、参照電流を出力する参照セルアレイ53と、前記参照電流から求められる参照抵抗値と前記記憶用磁気抵抗変化素子の抵抗値とを比較して当該メモリセルに記憶されている情報を判定する判定手段56と、が設けられている。更に、前記参照セルアレイが前記参照電流を出力する際に、前記複数の参照用磁気抵抗変化素子から選択される高抵抗状態の参照用磁気抵抗変化素子及び低抵抗状態の参照用磁気抵抗変化素子を特定する情報並びにこれらの接続関係を示す制御情報を記憶する記憶手段55と、前記制御情報に基づいて前記参照セルアレイの動作を制御する制御手段54と、が設けられている。

(もっと読む)

磁気抵抗効果素子および磁気記憶装置

【課題】低コストでホイスラー合金の規則化を促進させ、高い磁気抵抗効果を実現すること。

【解決手段】下地層11に自由磁化層12、非磁性層13、固定磁化層14、反強磁性層15および保護層16を積層した積層構造を有する磁気抵抗効果素子1において、自由磁化層12を固定磁化層14のうち少なくともいずれか1層をホイスラー合金で形成し、下地層、非磁性層13、保護層16のうち少なくとも1層をB2規則化構造の合金層で形成する。

(もっと読む)

アクティブストラップ式磁気ランダムアクセスメモリの記憶素子

【課題】 磁気記憶層、基準層及び基準層と記憶層の間に挿入された絶縁層から成る磁気トンネル接合部と、磁気トンネル接合部の一方の端を第一の選択用トランジスタと横方向に接続する第一のストラップ部分とを有する、熱アシストスイッチング書込手順による磁気ランダムアクセスメモリ(MRAM)の記憶素子である。

【解決手段】 この記憶素子には、第一のストラップ部分と逆側に延びるとともに、磁気トンネル接合部の前記の一方の端を第二の選択用トランジスタと横方向に接続する第二のストラップ部分が更に設けられており、これらの第一と第二のストラップ部分は、第一と第二の選択用トランジスタを介して電流が流れるように構成されている。ここで開示した記憶素子の電気消費量は、従来のMRAM記憶素子よりも少ない。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の生産性を向上させる。

【解決手段】シリコン基板1を覆う層間絶縁膜ILと、複数のメモリセルとを有する半導体装置であって、複数のメモリセルは、層間絶縁膜IL内に配置された記憶素子部mr1と、記憶素子部mr1に電気的に接続するようにして配置された下部電極BEおよび上部電極TEとを有する。下部電極BEと上部電極TEとは層間絶縁膜IL内において互いに交差するようにして配置され、その交差部に挟まれるようにして記憶素子部mr1が配置されている。記憶素子部mr1は、磁気抵抗メモリ、相変化メモリ、または、抵抗変化メモリからなる。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、裏面コンタクト電極と拡散層とのコンタクト抵抗が低減して、半導体装置の動作速度の向上を図ることを可能にする。

【解決手段】基板10の表面側に形成された拡散層25P、26P、25N、26Nと、前記拡散層25P、26P、25N、26Nの表面に形成されていて前記拡散層25P、26P、25N、26Nよりも抵抗が低い低抵抗部27P、28P、27N、28Nと、前記基板10の裏面側より前記基板10を貫通して前記拡散層25P、26P、25N、26Nを通して前記低抵抗部27P、28P、27N、28Nに接続された裏面コンタクト電極63P、64P、63N、64Nを有する。

(もっと読む)

81 - 100 / 327

[ Back to top ]